(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С ПАМЯТЬЮ | 1991 |

|

RU2018941C1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1345203A1 |

| УСТРОЙСТВО МЕЖМАШИННОГО ОБМЕНА | 1987 |

|

SU1549371A1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| Устройство для обмена информацией с общей шиной | 1984 |

|

SU1322301A1 |

| Устройство для сопряжения микропроцессора с магистралью | 1985 |

|

SU1302287A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для управления подключением к магистрали общего блока памяти | 1980 |

|

SU934834A1 |

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение области применения устройства за счет возможности сопряжения с несколькими общими магистралями. Устройство содержит блок 1 приемопередатчиков, элемент И 2, дешифратор 3 адреса, элемент 4 задержки, элементы ИЛИ 5, 6. 2 ил.

,

Нп

Ц /5„

Фиг /

Щ 16п

Изобретение относится к вычисгш- тельной технике и может быть использовано -В вычислительных системах с общими магистралями для сопряжения микропрограммных процессоров с мультиплексированными линиями адреса/данных и отсутствием линии синхронизации адреса.,

Цель изобретения расширение области применения устройства за счет возможности сопряжения с несколькими общими магистралями.

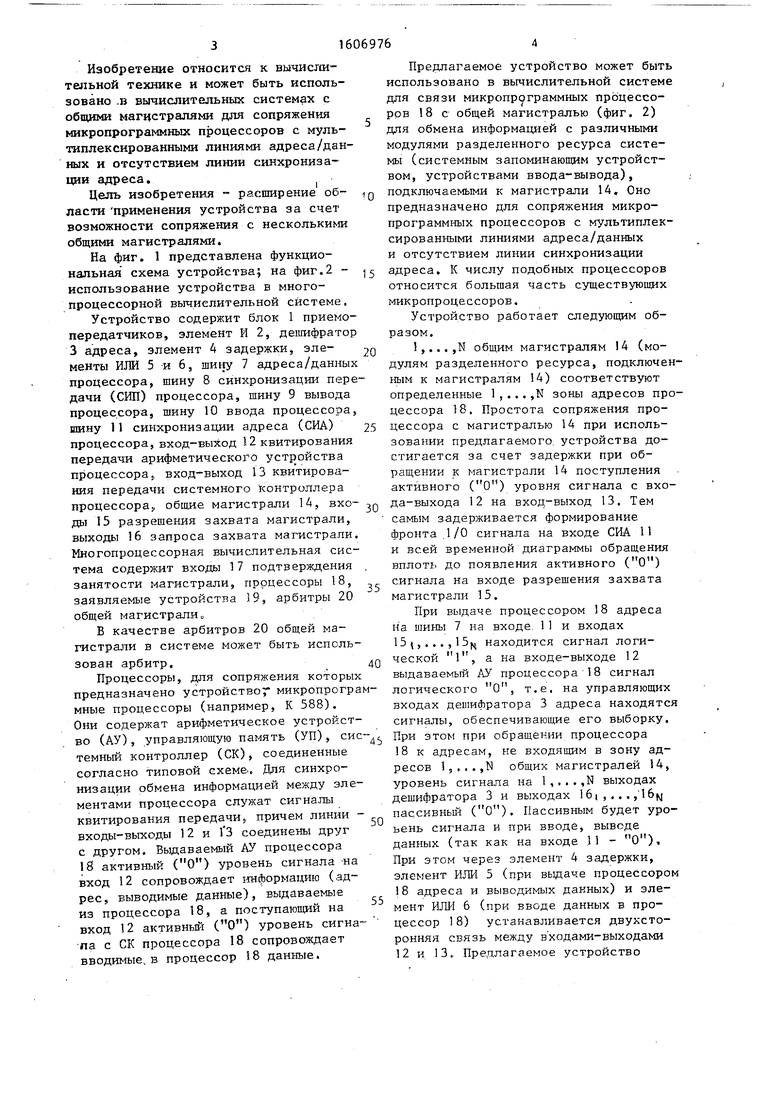

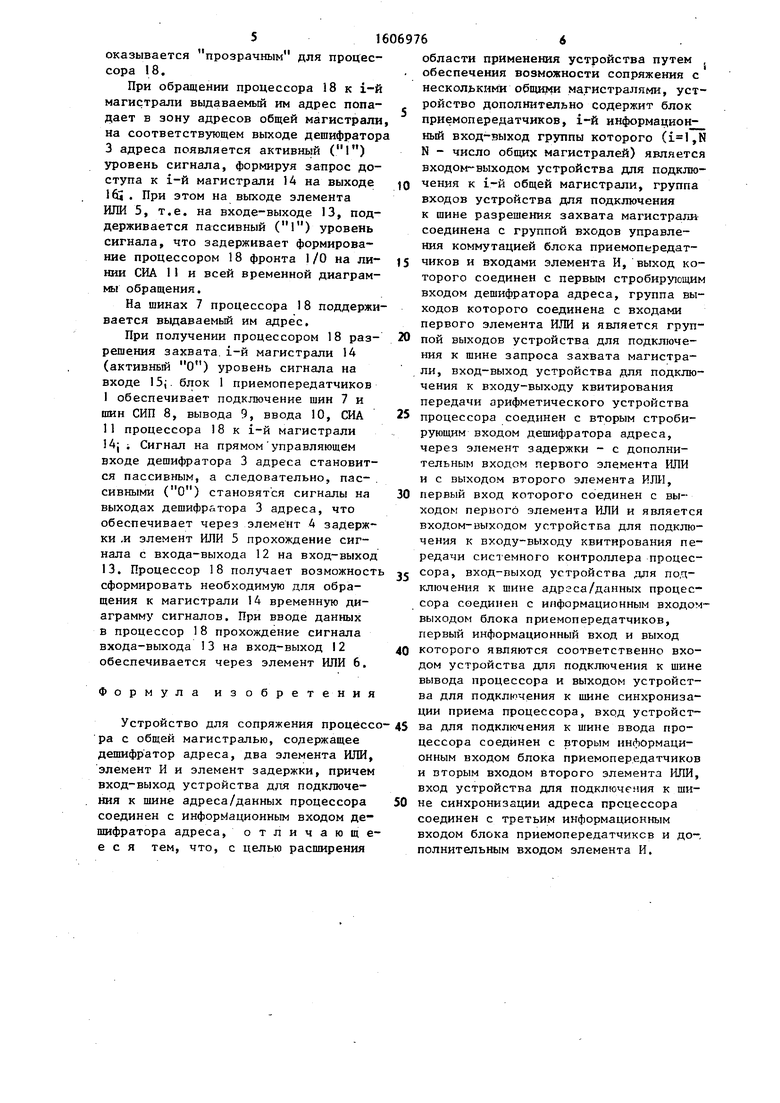

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - использование устройства в многопроцессорной вычислительной системе,

Устройство содержит блок 1 приемопередатчиков, элемент и 2, дешифратор

0

15

3 адреса,

задержки, эле20

25

30

элемент 4

менты ИЛИ 5 и 6, mmty 1 адреса/данных процессора, шину 8 синхронизации П(2ре- дачи (СИП) процессора, шину 9 вывода процессора, шину 10 ввода процессора, шину 11 синхронизации адреса (СИЛ) процессора, вход-выход 12 квитирования передачи арифметического уст1)ойства процессора., вход-выход 13 квитирования передачи системного контроллера процессора, общие магистрали 14, входы 15 разрешения захвата магистрали, выходы 16 запроса захвата магистрали. Многопроцессорная вычислительная система содержит входы 17 подтверждения , занятости магистрали, процессоры 18, заявляемые устройства 9, арбитры 20 общей магистрали

В качестве арбитров 20 общей магистрали в системе может быть использован арбитр.40

Процессоры, для сопряжения которых предназначено устройствог микропрограммные процессоры (например, К 588).

Предлагаемое устройство может быть использовано в вычислительной системе для связи микропрограммных процессоров 18 с общей магистралью (фиг. 2) для обмена информацией с различными модулями разделенного ресурса системы (системным запоминающим устройством, устройствами ввода-вывода), подключаемыми к магистрали 14. Оно предназначено для сопряжения микропрограммных процессоров с мультиплексированными линиями адреса/данных и отсутствием линии синхронизации адреса. К числу подобных процессоров относится большая часть существующих микропроцессоров.

Устройство работает следующим образом.

1,...,N общим магистралям 14 (модулям разделенного ресурса, подключен miiM к магистралям 14) соответствуют определенные 1,...,N зоны адресов про цессора 18. Простота сопряжения процессора с магистралью 14 при использовании предлагаемого, устройства достигается за счет задержки при обращении к магистрали 14 поступления активного (О) уровня сигнала с входа-выхода 12 на вход-выход 13. Тем самым задерживается формирование фронта. 1/0 сигнала на входе СИЛ 11 и всей временной диаграммы обращения вплоть до появления активного ( О ) сигнала на входе разрешения захвата магистрали 15.

При выдаче процессором 18 адреса на шины 7 на входе. 11 и входах 15 ,...,15щ находится сигнал логической 1, а на входе-выходе 12 выдаваемый .АУ процессора 1 8 сигнал логического О, т.е. на управляющих входах дешифратора 3 адреса находятся сигналы, обеспечивающие его выборку.

Они содержат арифметическое устройство (АУ), управляющую память (УП), , При этом при обращении процессора темный контроллер (СК), соединенные 18 к адресам, не входящим в зону ад- согласно типовой схеме. Для синхронизации обмена информацией между элементами процессора служат сигналы квитирования передачи,, причем линии - входы-выходы 12 и 13 соединены друг с другом. Выдаваемый АУ процессора 18 активный (О) уровень сигнала на вход 12 сопровождает информацию (адрес, выводимые данные), выдаваемые

50

из процессора 18, а поступающий на вход 12 активньй (О) уровень сигна- па с СК процессора 18 сопровождает вводимые, в процессор 18 данные.

ресов l,..., общих магистралей 14, уровень сигнала на 1,...,N выходах дешифратора 3 и выходах 16(,..., 16 пассивный (О). Пассивным будет уровень сигнала и при вводе, выводе данных (так как на входе }1 - О ), При этом через элемент 4 задержки, элемент ИЛИ 5 (при вьщаче процессоро 18 адреса и выводимых данных) и элемент ШБ- 6 (при вводе данных в процессор 18) устанавливается двухсторонняя связь между входами-выходами 12 и 13„ Предлагаемое устройство

0

5

0

5

30

,

40

Предлагаемое устройство может быть использовано в вычислительной системе для связи микропрограммных процессоров 18 с общей магистралью (фиг. 2) для обмена информацией с различными модулями разделенного ресурса системы (системным запоминающим устройством, устройствами ввода-вывода), подключаемыми к магистрали 14. Оно предназначено для сопряжения микропрограммных процессоров с мультиплексированными линиями адреса/данных и отсутствием линии синхронизации адреса. К числу подобных процессоров относится большая часть существующих микропроцессоров.

Устройство работает следующим образом.

1,...,N общим магистралям 14 (модулям разделенного ресурса, подключен miiM к магистралям 14) соответствуют определенные 1,...,N зоны адресов процессора 18. Простота сопряжения процессора с магистралью 14 при использовании предлагаемого, устройства достигается за счет задержки при обращении к магистрали 14 поступления активного (О) уровня сигнала с входа-выхода 12 на вход-выход 13. Тем самым задерживается формирование фронта. 1/0 сигнала на входе СИЛ 11 и всей временной диаграммы обращения вплоть до появления активного ( О ) сигнала на входе разрешения захвата магистрали 15.

При выдаче процессором 18 адреса на шины 7 на входе. 11 и входах 15 ,...,15щ находится сигнал логической 1, а на входе-выходе 12 выдаваемый .АУ процессора 1 8 сигнал логического О, т.е. на управляющих входах дешифратора 3 адреса находятся сигналы, обеспечивающие его выборку.

с, При этом при обращении процессора 18 к адресам, не входящим в зону ад-

При этом при обращении процессора 18 к адресам, не входящим в зону ад-

ресов l,..., общих магистралей 14, уровень сигнала на 1,...,N выходах дешифратора 3 и выходах 16(,..., 16 пассивный (О). Пассивным будет уровень сигнала и при вводе, выводе данных (так как на входе }1 - О ), При этом через элемент 4 задержки, элемент ИЛИ 5 (при вьщаче процессором 18 адреса и выводимых данных) и элемент ШБ- 6 (при вводе данных в процессор 18) устанавливается двухсторонняя связь между входами-выходами 12 и 13„ Предлагаемое устройство

оказывается прозрачным для процессора 18.

При обращении процессора 18 к i-й магистрали выдаваемый им адрес попадает в зону адресов общей магистрали на соответствующем выходе дешифратор 3 адреса появляется активный (1) уровень сигнала, формируя запрос доступа к i-й магистрали 14 на выходе 165 . При зтом на выходе элемента ИЛИ 5, т.е. на входе-выходе 13, поддерживается пассивный () уровень сигнала, что задерживает формирование процессором 18 фронта 1/0 на ли- НИИ СИА 11 и всей временной диаграммы обращения.

На шинах 7 процессора 18 поддерживается выдаваемьй им адрес.

При получении процессором 18 раз- решения захвата, i-й магистрали 14 (активнБш О) уровень сигнала на входе 15;. блок 1 приемопередатчиков 1 обеспечивает подключение шин 7 и шин СИП 8, вывода 9, ввода 10, СИА П процессора 18 к i-й магистрали 14j i Сигнал на прямом управляющем входе дешифратора 3 адреса становится пассивным, а следовательно, пассивными (О) становятся сигналы на

выходах дешифратора 3 адреса, что обеспечивает через элемент 4 задержки ,и элемент ИЛИ 5 прохождение сигнала с входа-выхода 12 на вход-выход 13. Процессор 18 получает возможност сформировать необходимую для обращения к магистрали 14 временную диаграмму сигнсшов. При вводе данных в процессор 18 прохождение сигнала входа-выхода I3 на вход-выход I2 обеспечивается через элемент ИЛИ 6.

Формула изобретения

Устройство для сопряжения процёссо ра с общей магистралью, содержащее дешифратор адреса, два элемента ИЛИ, элемент И и элемент задержки, причем вход-выход устройства ддя подключения к шине адреса/данных процессора соединен с информационным входом дешифратора адреса, отличающееся тем, что, с целью расширения

Q 5

0 5

0

5

О

5 0

области применения устройства путем , обеспечения возможности сопряжения с несколькими общими магистралями, устройство дополнительно содержит блок приемопередатчиков, i-й информационный вход-выход группы которого (,N N - число общих магистралей) является входом-выходом устройства для подключения к i-й общей магистрали, группа входов устройства для подключения к шине разрешения захвата магистрали соединена с группой входов управления коммутацией блока приемопередатчиков и входами элемента И, выход которого соединен с первым стробирующим входом дешифратора адреса, группа выходов которого соединена с входами первого элемента ИЛИ и является группой выходов устройства для подключения к шине запроса захвата магистрали, вход-выход устройства для подключения к входу-выходу квитирования передачи арифметического устройства процессора соединен с вторым стробирующим входом дешифратора адреса, через элемент задержки - с дополнительным входом первого элемента ИЛИ и с выходом второго элемента ИЛИ, первый вход которого соединен с выходом первого элемента ИЛИ и является входом-выходом устройства для подключения к входу-выходу квитирования передачи системного контроллера процессора, вход-выход устройства для подключения к шине адрзса/данных процессора соединен с информационным входом- выходом блока приемопередатчиков, первый информационный вход и выход которого являются соответственно входом устройства для подключения к шине вывода процессора и выходом устройства для подключения к шине синхронизации приема процессора, вход устройства для подключения к шине ввода процессора соединен с вторым информационным входом блока приемопередатчиков и вторым входом второго элемента ИЛИ, вход устройства для подключения к шине синхронизации адреса процессора соединен с третьим информационным входом блока приемопередатчиков и до-, полнительным входом элемента И.

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1984 |

|

SU1180906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппаратные средства микроэвм | |||

| М | |||

| : ир | |||

| с | |||

| Коловратный насос с кольцевым поршнем, перемещаемым эксцентриком | 1921 |

|

SU239A1 |

| Крутильный аппарат | 1922 |

|

SU234A1 |

Авторы

Даты

1990-11-15—Публикация

1988-12-05—Подача