Изобретение относится к вычислительной технике, а именно к средствам для автоматического контроля микропроцессорных больших интегральных схем и других цифровых обьектов.

Целью изобретения является повышение коэффициента использования оборудования и достоверности контроля.

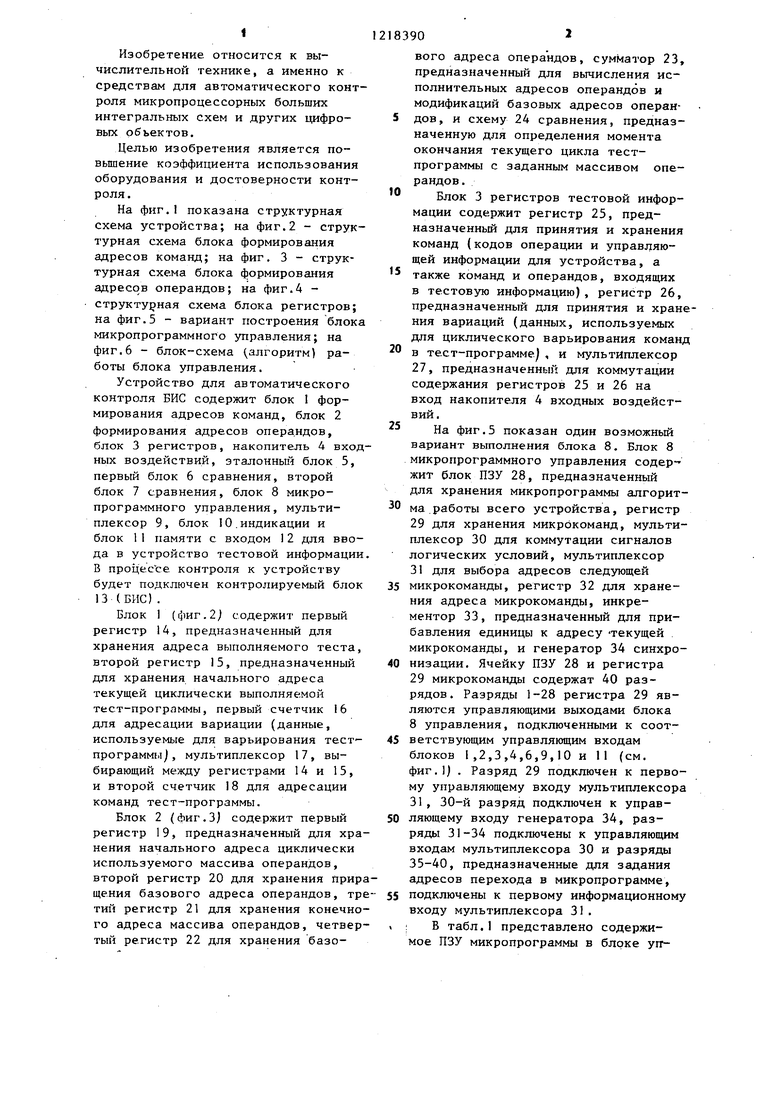

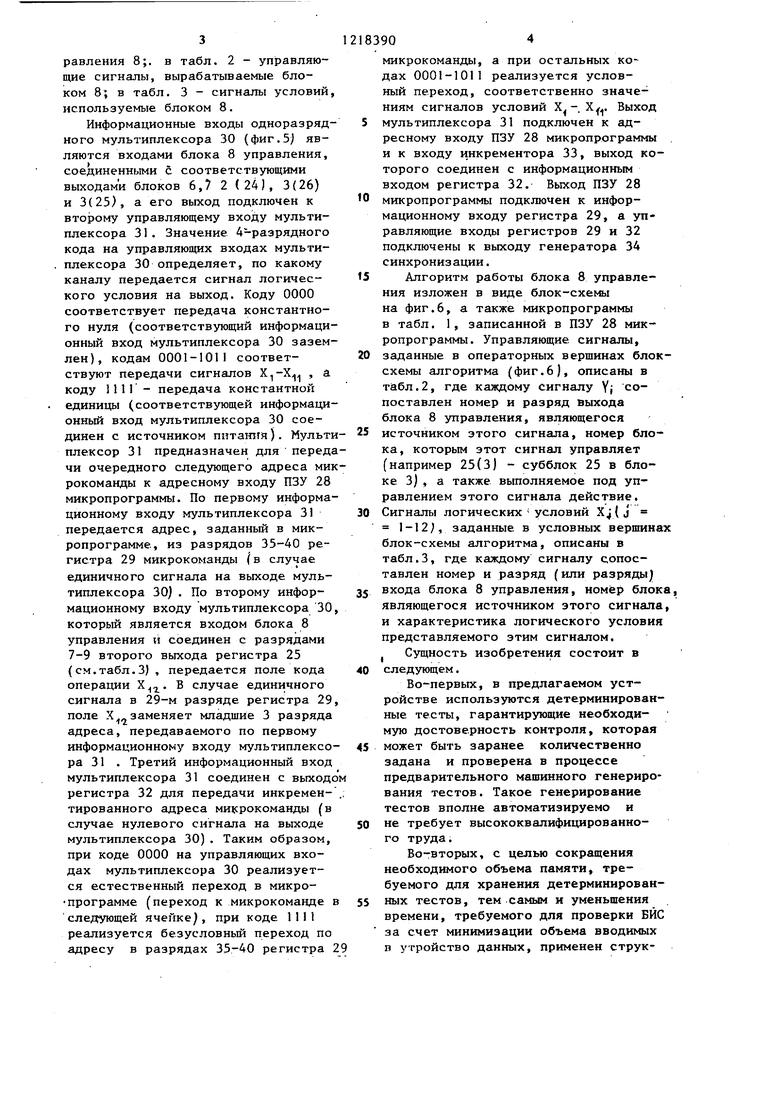

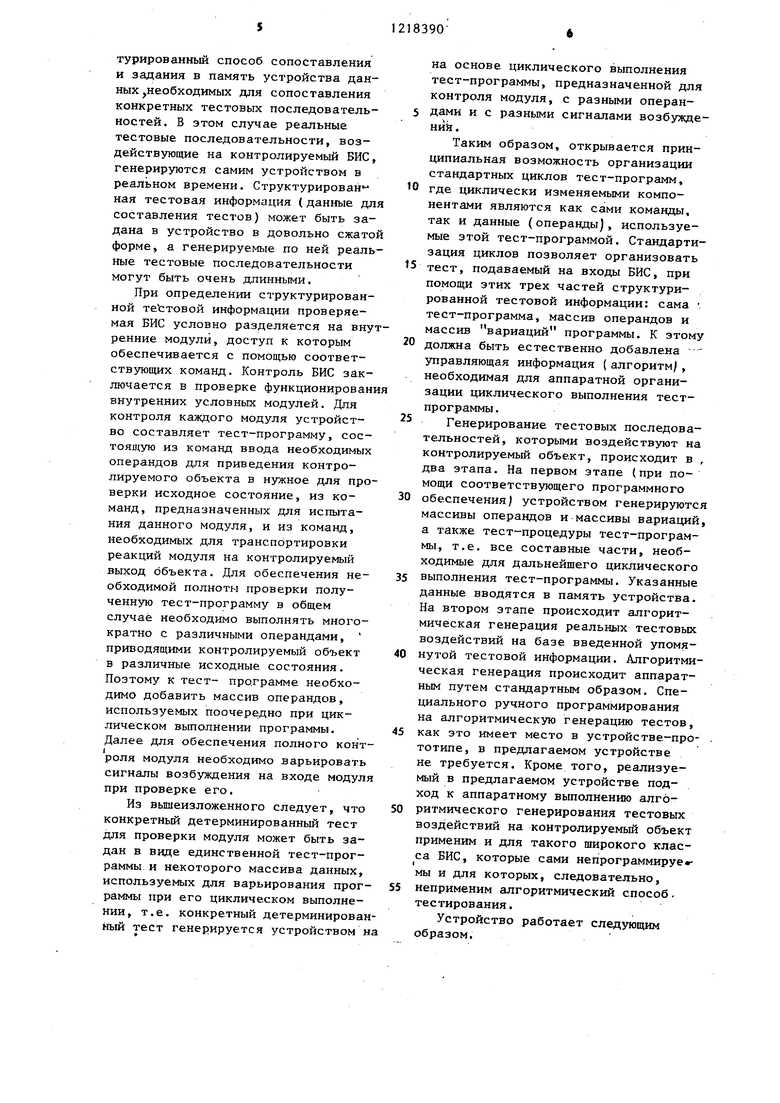

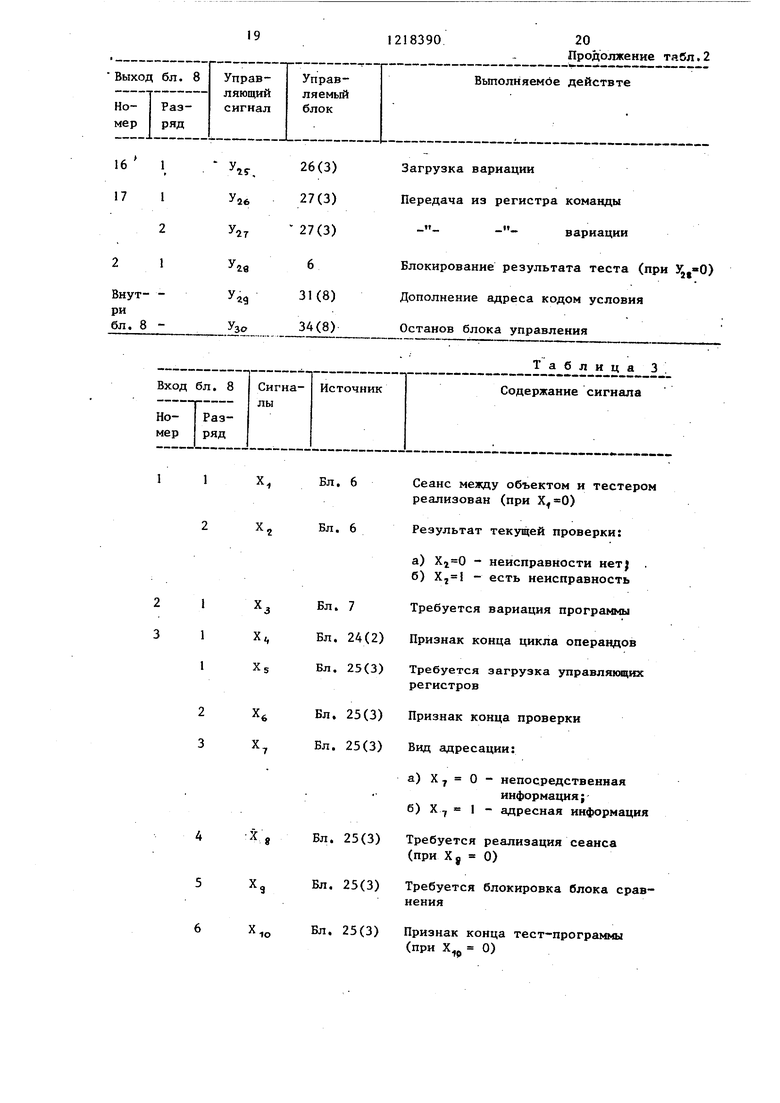

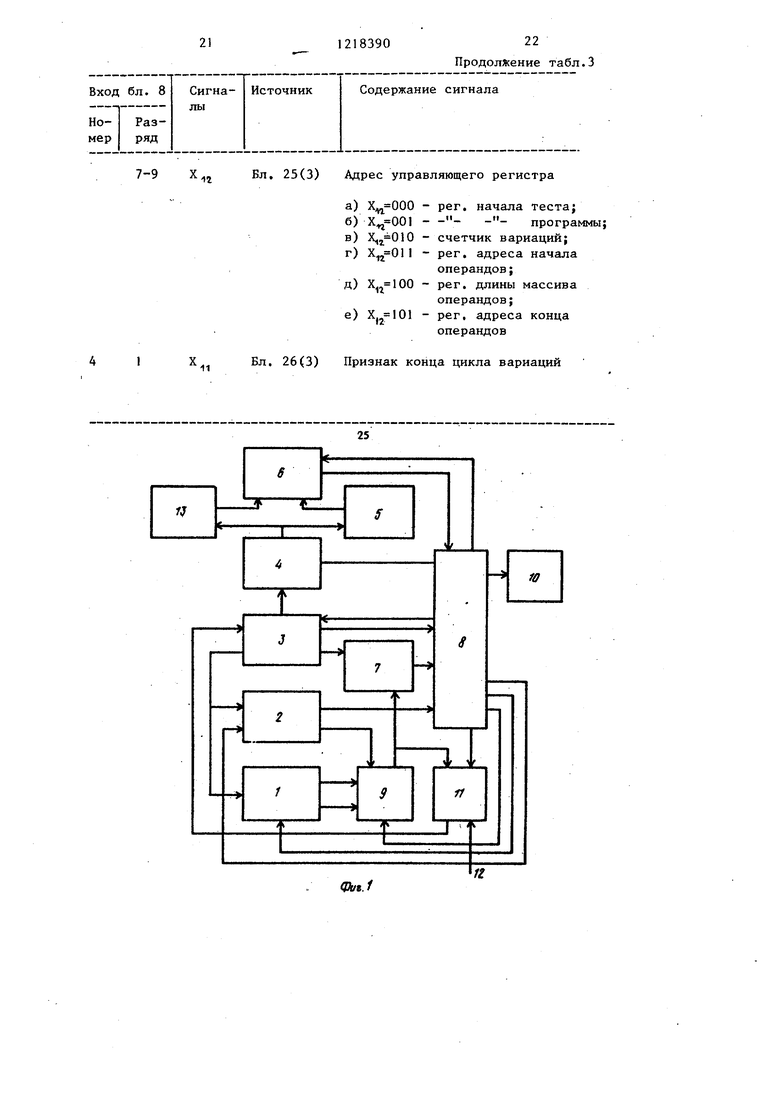

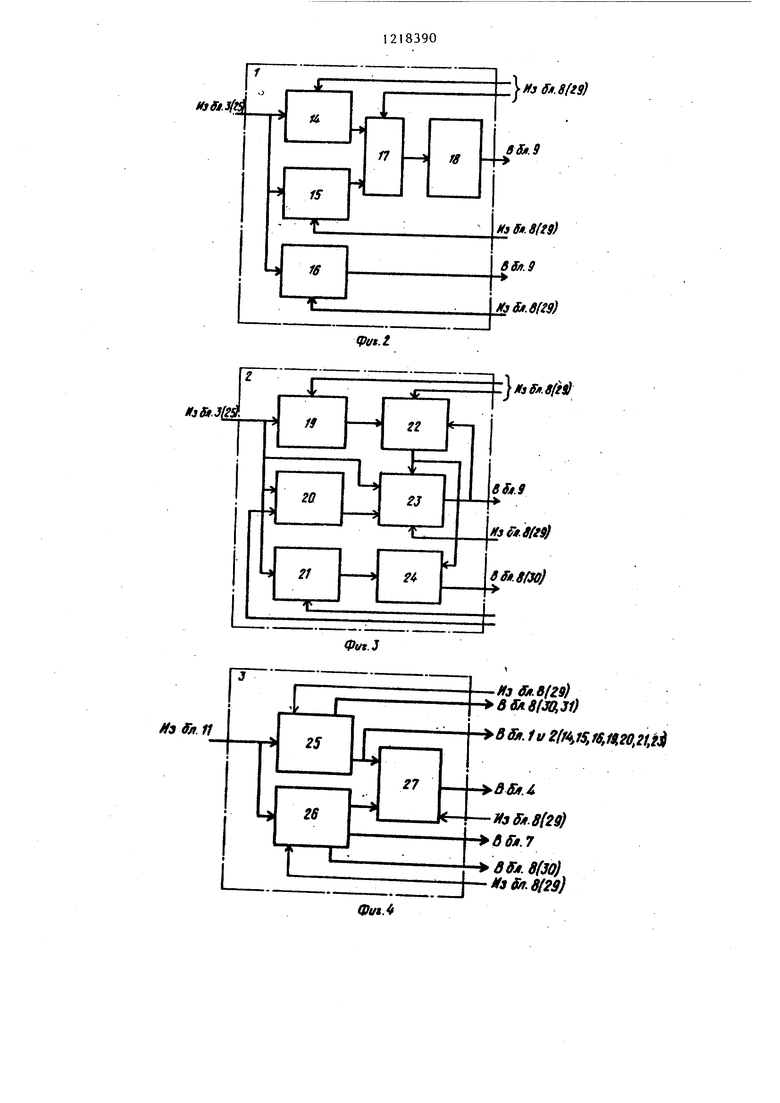

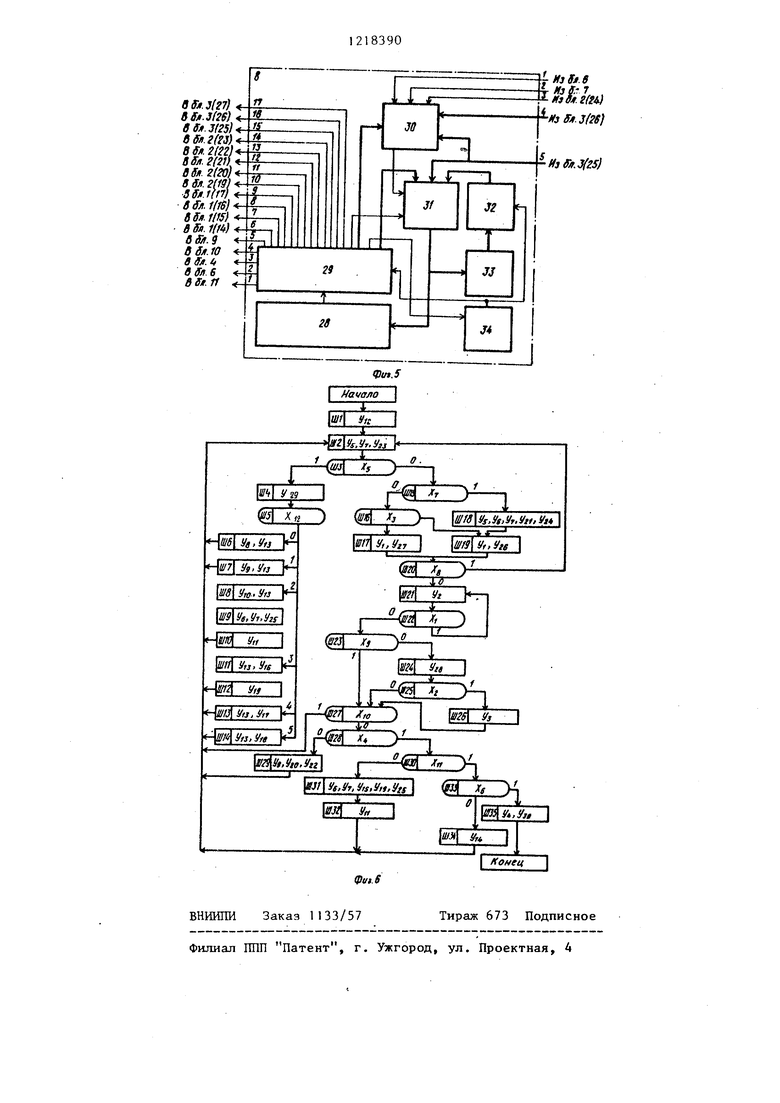

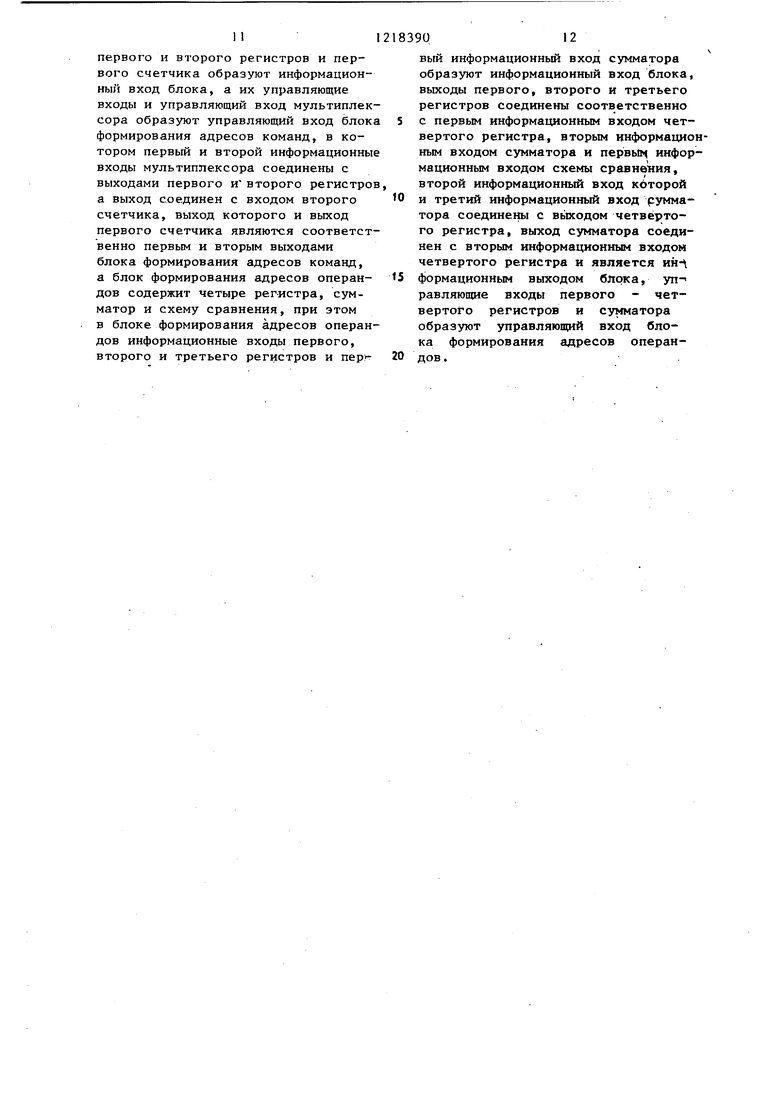

На фиг.1 показана структурная схема устройства; на фиг.2 - структурная схема блока формирования адресов команд; на фиг. 3 - структурная схема блока формирования адресов операндов; на фиг.4 - структурная схема блока регистров; на фиг.5 - вариант построения блока микропрограммного управления; на фиг,6 - блок-схема (алгоритм) работы блока управления.

Устройство для автоматического контроля БИС содержит блок 1 формирования адресов команд, блок 2 формирования адресов операндов, блок 3 регистров, накопитель 4 входных воздействий, эталонный блок 5, первый блок 6 сравнения, второй блок 7 сравнения, блок 8 микропрограммного управления, мультиплексор 9, блок 10.индикации и блок 11 памяти с входом 12 для ввода в устройство тестовой информации В процессе контроля к устройству будет подключен контролируемый блок 13 (БИС).

Блок 1 (фиг.2) содержит первый регистр 14, предназначенный для хранения адреса выполняемого теста, второй регистр 15, предназначенный для хранения начального адреса текущей циклически выполняемой тест-прогрпммы, первый счетчик 16 для адресации вариации (данные, используемые для варьирования тест- nporpaMMf.ij, мультиплексор 17, выбирающий между регистрами 14 и 15, и второй счетчик 18 для адресации команд тест-программы.

Блок 2 (фиг.З) содержит первый регистр 19, предназначенный для хранения начального адреса циклически используемого массива операндов, второй регистр 20 для хранения Прир щения базового адреса операндов, тр тий регистр 21 для хранения конечного адреса массива операндов, четвертый регистр 22 для хранения базо15

вого адреса операндов, сумматор 23, предназначенный для вычисления исполнительных адресов операндов и модификаций базовых адресов оперен5 ДОН, и схему 24 сравнения, предназначенную для определения момента окончания текущего цикла тест- программы с заданным массивом операндов.

Блок 3 регистров тестовой информации содержит регистр 25, предназначенный для принятия и хранения команд (кодов операции и управляющей информации для устройства, а также команд и операндов, входящих в тестовую информацию), регистр 26, предназначенный для принятия и хранения вариаций (данных, используемых для циклического варьирования команд

20 в тест-программе), и мультиплексор 27, предназначенный для коммутации содержания регистров 25 и 26 на вход накопителя 4 входных воздействий.

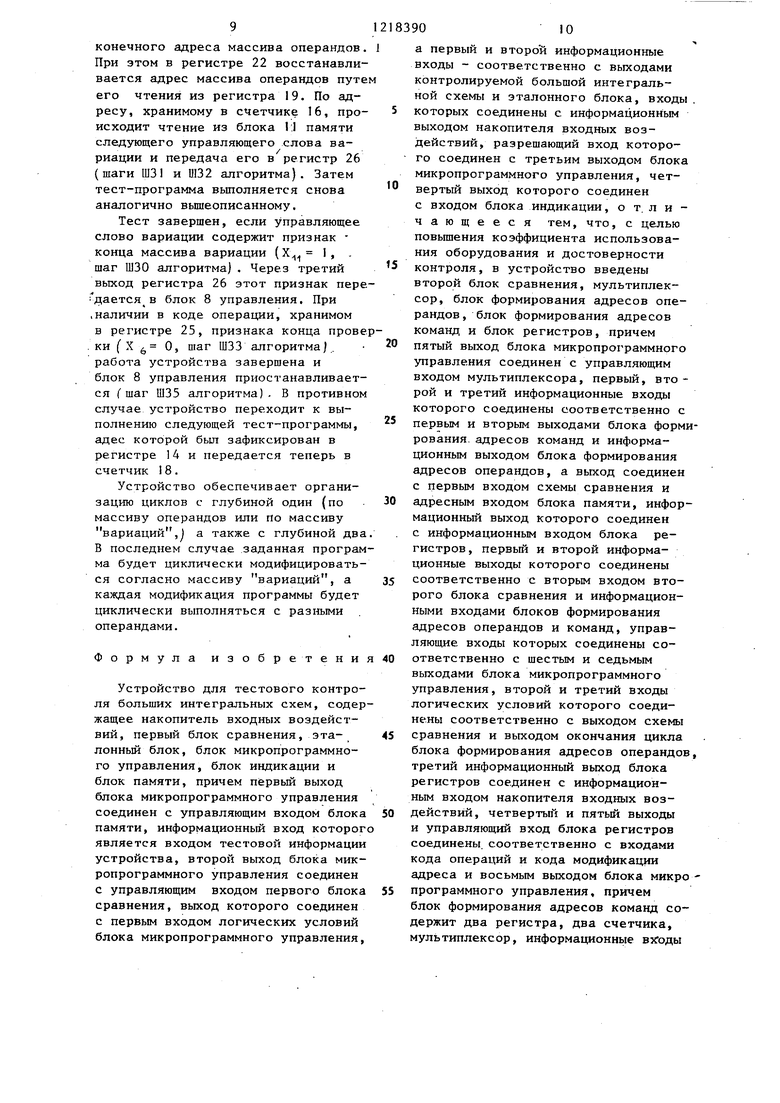

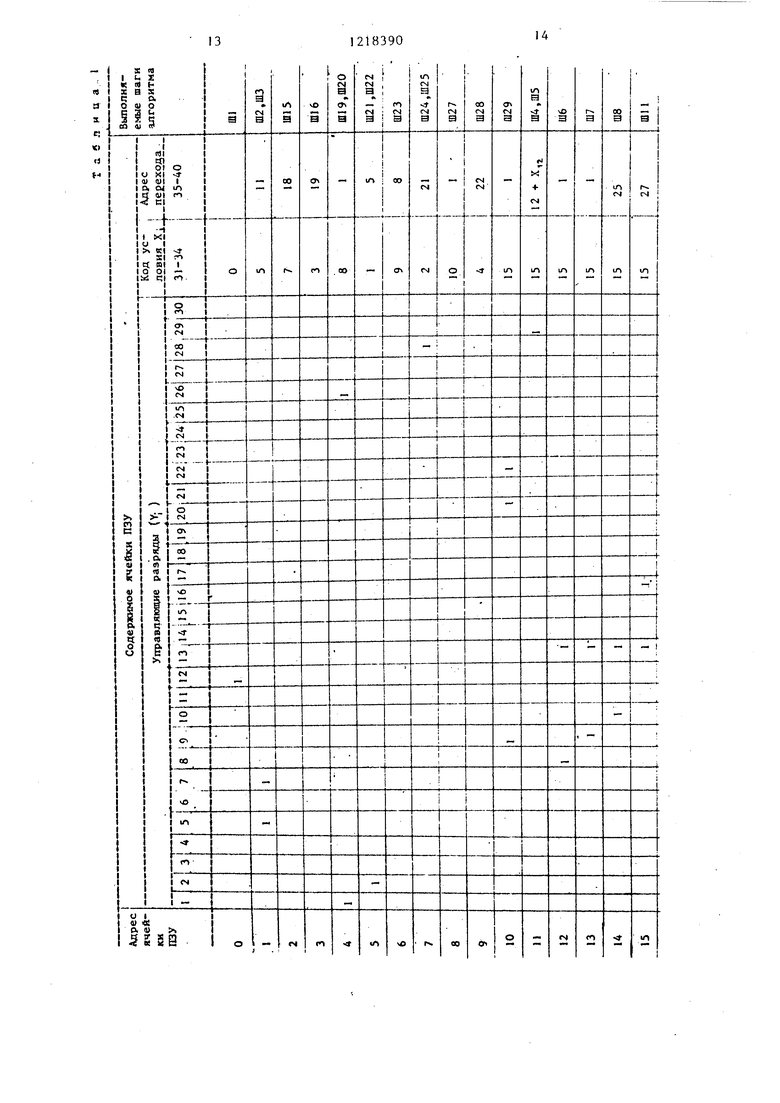

На фиг.5 показан один возможньш вариант выполнения блока 8. Блок 8 микропрограммного управления содержит блок ПЗУ 28, предназначенный для хранения микропрограммы алгорит30 ма.работы всего устройства, регистр 29 для хранения микрокоманд, мультиплексор 30 для коммутации сигналов логических условий, мультиплексор 31 для выбора адресов следующей

35 микрокоманды, регистр 32 для хранения адреса микрокоманды, инкре- ментор 33, предназначенный для прибавления единицы к адресу текущей микрокоманды, и генератор 34 синхро40 низации. Ячейку ПЗУ 28 и регистра 29 микрокоманды содержат 40 разрядов. Разряды 1-28 регистра 29 являются управляющими выходами блока 8 управления, подключенными к соот45 ветствующим управляющим входам блоков 1,2,3,4,6,9,10 и 11 (см. фиг.1) . Разряд 29 подключен к первому управляющему входу мультиплексора 31, 30-й разряд подключен к управ50 ляющему входу генератора 34, разряды 31-34 подключены к управляющим входам мультиплексора 30 и разряды 35-40, предназначенные для задания адресов перехода в микропрограмме, 55 подключены к первому информационному входу мультиплексора 31.

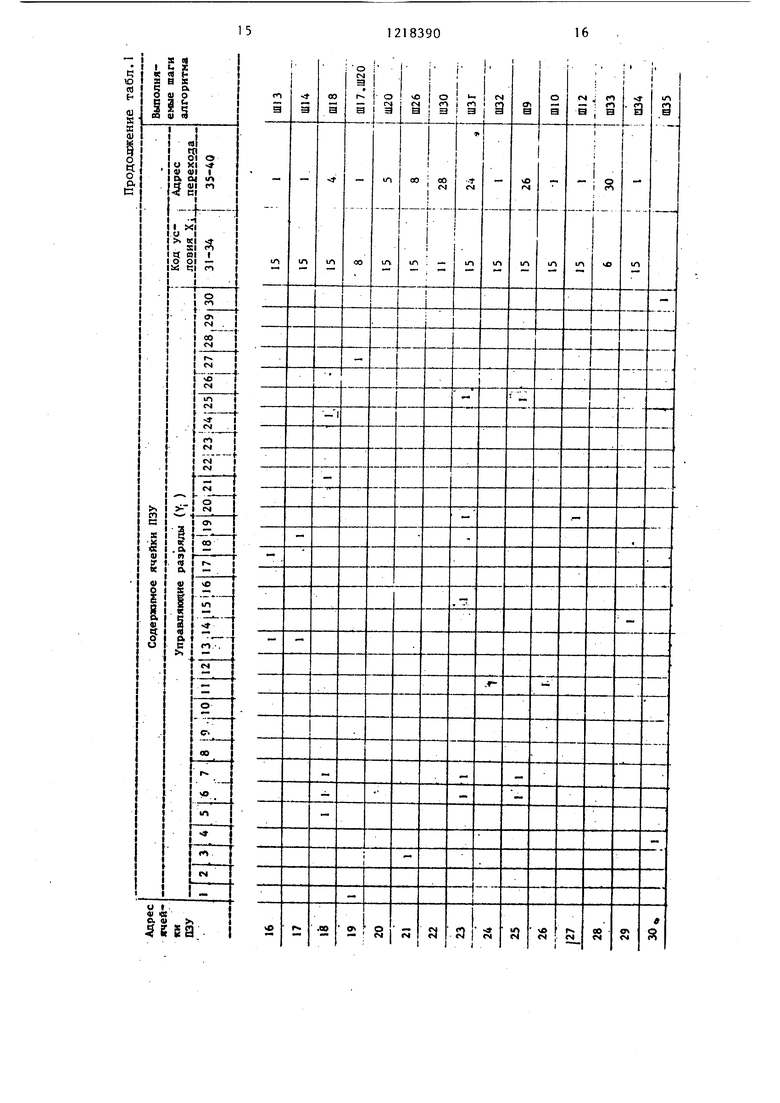

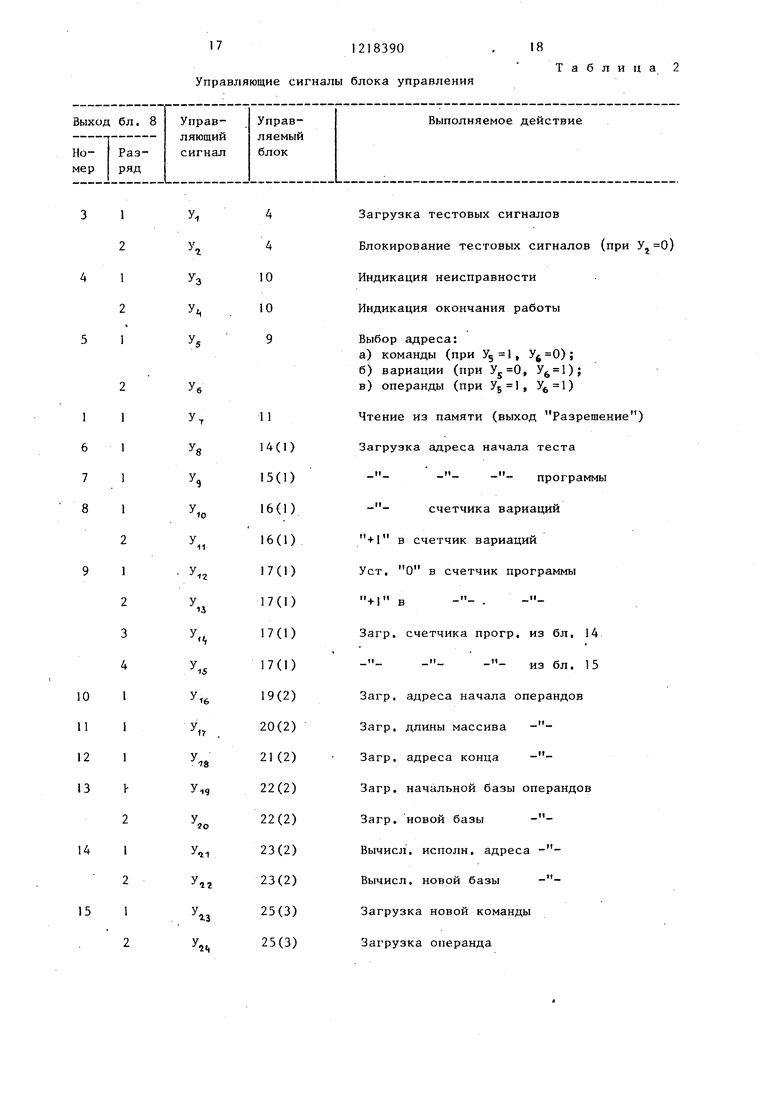

. : В табл.1 представлено содержимое ПЗУ микропрограммы в блоке уггравления 8;. в табл. 2 - управляющие сигналы, вырабатываемые блоком 8; в табл. 3 - сигналы условий, используемые блоком 8.

Информационные входы одноразрядного мультиплексора 30 (фиг.5 являются входами блока 8 управления, соединенными с соответствующими выходами блоков 6,7 2 (24), 3(26) и 3(25), а его выход подключен к второму управляющему входу мультиплексора 31. Значение 4-разрядного кода на управляющих входах мультиплексора 30 определяет, по какому каналу передается сигнал логического условия на выход. Коду 0000 соответствует передача константного нуля (соответствующий информационный вход мультиплексора 30 заземлен), кодам 0001-1011 соответствуют передачи сигналов , а

коду 1111 - передача константной единицы (соответствующей информационный вход мультиплексора 30 соединен с источником питаштя). Мультиплексор 31 предназначен для передачи очередного следующего адреса микрокоманды к адресному входу ПЗУ 28 микропрограммы. По первому информационному входу мультиплексора 31 передается адрес, заданный в микропрограмме, из разрядов 35-40 регистра 29 микрокоманды |в случае единичного сигнала на выходе мультиплексора 30). По второму информационному входу мультиплексора 30, который является входом блока 8 управления и соединен с разрядами 7-9 второго выхода регистра 25 (см.табл.3), передается поле кода операции Х. В случае единичного сигнала в 29-м разряде регистра 29, поле Х заменяет младшие 3 разряда адреса, передаваемого по первому информационному входу мультиплексора 31 . Третий информационный вход мультиплексора 31 соединен с выходо м регистра 32 для передачи инкремен- .; тированного адреса микрокоманды (в случае нулевого сигнала на выходе мультиплексора 30). Таким образом, при коде 0000 на управляющих входах мультиплексора 30 реализуется естественный переход в микро- программе (переход к микрокоманде в следующей ячейке), при коде 1111 реализуется безусловный переход по адресу в разрядах 35-40 регистра 29

12183904

микрокоманды, а при остальных ко дах 0001-1011 реализуется условный переход, соответственно значениям сигналов условий Х -. Х. Выход 5 мультиплексора 31 подключен к адресному входу ПЗУ 28 микропрограммы и к входу инкрементора 33, выход которого соединен с информационным входом регистра 32. Выход ПЗУ 28

О микропрограммы подключен к информационному входу регистра 29, а управляющие входы регистров 29 и 32 подключены к выходу генератора ЗА синхронизации.

15 Алгоритм работы блока 8 управления изложен в виде блок-схемы на фиг.6, а также микропрограммы в табл. 1, записанной в ПЗУ 28 микропрограммы. Управляющие сигналы,

20 заданные в операторных вершинах блок- схемы алгоритма (фиг.6), описаны в табл.2, где каждому сигналу Yj сопоставлен номер и разряд выхода блока 8 управления, являющегося

25 источником этого сигнала, номер блока, которым этот сигнал управляет (например 25(3) - субблок 25 в блоке 3) ,, а также выполняемое под управлением этого сигнала действие.

30 Сигналы логических - условий X j ( j 1-12, заданные в условных вершинах блок-схемы алгоритма, описаны в табл.3, где каждому сигналу сопоставлен номер и разряд (или разряды)

35 входа блока 8 управления, номер блока, являющегося источником этого сигнала, и характеристика логического условия представляемого этим сигнгшом. Сущность изобретения состоит в

40 следующем.

Во-первых, в предлагаемом устройстве используются детерминированные тесты, гарантирующие необходимую достоверность контроля, которая

45 может быть заранее количественно задана и проверена в процессе предварительного машинного генерирования тестов. Такое генерирование тестов вполне автоматизируемо и

50 не требует высококвалифицированного труда.

Во-вторых, с целью сокращения необходимого объема памяти, требуемого для хранения детерминирован55 ных тестов, тем самым и уменьшения времени, требуемого для проверки БИС за счет минимизации объема вводимых в утройство данных, применен струкследующем.

Во-первых, в предлагаемом устройстве используются детерминированные тесты, гарантирующие необходимую достоверность контроля, которая

может быть заранее количественно задана и проверена в процессе предварительного машинного генерирования тестов. Такое генерирование тестов вполне автоматизируемо и

не требует высококвалифицированного труда.

Во-вторых, с целью сокращения необходимого объема памяти, требуемого для хранения детерминированных тестов, тем самым и уменьшения времени, требуемого для проверки БИС за счет минимизации объема вводимых в утройство данных, применен структурированный способ сопоставления и задания в память устройства данных необходимых для сопоставления конкретных тестовых последовательностей. В этом случае реальные тестовые последовательности, воздействующие на контролируемый БИС, генерируются самим устройством в реальном времени. Структурирован ная тестовая информация (данные дл составления тестов) может быть задана в устройство в довольно сжато форме, а генерируемые по ней реальные тестовые последовательности могут быть очень длинными.

При определении структурированной тестовой информации проверяемая БИС условно разделяется на внуренние модули, доступ к которым обеспечивается с помощью соответствующих команд. Контроль БИС заключается в проверке функционирован внутренних условных модулей. Для контроля каждого модуля устройство составляет тест-программу, состоящую из команд ввода необходимых операндов для приведения контролируемого объекта в нужное для проверки исходное состояние, из команд, предназначенных для испытания данного модуля, и из команд, необходимых для транспортировки реакций модуля на контролируемый выход объекта. Для обеспечения необходимой полноты проверки Полученную тест-программу в общем случае необходимо выполнять многократно с различными операндами, приводящими контролируемый объект в различные исходные состояния. Поэтому к тест- программе необходимо добавить массив операндов, используемых поочередно при циклическом вьтолнении программы. Далее для обеспечения полного контроля модуля необходимо варьировать сигналы возбуждения на входе модул при проверке его.

Из вышеизложенного следует, что конкретный детерминированный тест для проверки модуля может быть задан в виде единственной тест-программы и некоторого массива данных, используемых для варьирования программы при его циклическом выполнении, т.е. конкретный детерминированый тест генерируется устройством

на основе циклического выполнения тест-программы, предназначенной для контроля модуля, с разными операн- дами и с разными сигналами возбуждений.

Таким образом, открывается принципиальная возможность организации стандартных циклов тест-программ,

где циклически изменяемыми компонентами являются как сами команды, так и данные (операнды), используемые этой тест-программой. Стандартизация циклов позволяет организовать

тест, подаваемый на входы БИС, при помощи этих трех частей структурированной тестовой информации: сама . тест-программа, массив операндов и массив вариаций программы. К этому

должна быть естественно добавлена - управляющая информация (алгоритм/, необходимая для аппаратной организации циклического выполнения тест- программы .

Генерирование тестовых последовательностей, которыми воздействуют на контролируемый объект, происходит в , два этапа. На первом этапе (при помощи соответствующего программного

обеспечения) устройством генерируются массивы операндов и массивы вариаций, а также тест-процедуры тест-программы, т.е. все составные части, необходимые для дальнейщего циклического

выполнения тест-программы. Указанные данные вводятся в память устройства. На втором этапе происходит алгоритмическая генерация реальных тестовых воздействий на базе введенной упомянутой тестовой информации. Алгоритмическая генерация происходит аппаратным путем стандартным образом. Специального ручного программирования на алгоритмическую генерацию тестов,

как это имеет место в устройстве-прототипе, в предлагаемом устройстве не требуется. Кроме того, реализуемый в предлагаемом устройстве подход к аппаратному выполнению алгоритмического генерирования тестовых воздействий на контролируемый объект применим и для такого широкого класса БИС, которые сами непрограммируе - мы и для которых, следовательно,

неприменим алгоритмический способ. тестирования.

Устройство работает следующим образом.

7

До начала работы в блок 11 памяти через вход 12 вводится снаружи тестовая информация, состоящая из последовательности тестов, причем в каждый тест входит управляющее слово, тест-программа, массив вариаций и массив операндов. В управляющее слово йходит адрес следующего теста, начальйый адрес тест- программы, начальный, адрес массива вариаций, начальный адрес массива операндов, приращение для массива операндов и конечный адрес операндов.

После запуска устройства, согласно блок-схеме алгоритма, приведенной на фиг.6, начинает работать бло 8 управления, а также блок 3 регистров тестовой информации, прочитывая тестовую информацию из блока 11 памяти. По адресу, хранимому в счетчике 18, в начале работы устройства он устанавливается в нулево состояние (шаг 1111 алгоритма), затем в ходе работы устройства он будет загружен или из регистра 14 ( шаг 34 алгоритма), или из регистра 15 (шаг 35), происходит чтение очеред ного слова из блока 11 памяти в регистр 25 (шаг й2) . Слово состоит из кода операции и тестовой информации. Код операции выдается через второй выход регистра 25 в блок 8 управления. Тестовая информация выдается через первый выход регистра 25, и она может представить адрес из управляющего слова теста (при Хб и , тестовое воздействие (при yij 0) или адрес операнда (при Х и . Этим операциям соответствуют шаги ШЗ и Ш5 алгоритма.

В начале выполнения теста управляющее слово теста распределяется по регистрам 14,15.19,20 и счетчику 16 (шаги Ш4-Ш14 алгоритма). По адресу, записанному в счетчик 18 происходит чтение из блока 11 памяти управляющего слова вариации и запись его в регистр 26 (шаг Ш9 алгоритма « Управляющее слово вариации состоит из тестового воздействи и адреса слова в тест-программе, которое должно быть подвергнуто варированию. Сравнение этого адреса с текущими адресами выполняемой тест программы происходит в блоке 7 сравнения (шаг Ш16 алгоритма). Регистр 22 загружается базовым адресо

o

S

0

5

8390

5

0

5

0

5

8

операндов, хранимых в регистре 19 (шаг Ш12 алгоритма),

При выполнении тест-программы, тестовые воздействия из регистра 25 через мультиплексор 27 передаются в накопитель 4 .{шаг Ш19 алгоритма) . Формированные входные сигналы подаются на контролируемый 13 и эталонный 5 блоки. Если тестовая информация в регистре 25 представляет собой адрес операнда (Х l) , то последний передается в сумматор 23 для вычисления исполнительного адреса, который используется для чтения из блока 11 памяти нужного операнда (шаг Ш8 алгоритма). Последний принимается в регистр 25 и передается в качестве очередного тестового воздействия в накопитель 4 (шаг Ш19 алгоритма). В случае сигнала из блока 7, означающего равенство адреса, хранимого в регистре 26, и текущего адреса выполняемой тест-программы (Хз 1) , тестовое воздействие берется из регистра 26 и передается через мультиплексор 27 в блок j4 (шаг Ш17 алгоритма).

В процессе приложения тестовых воздействий (при Xg О, шаг Ш20 алгоритма) к входам контролируемого 13 и эталонного 5 блоков сигналы с их выходов сравниваются в блоке 6 сравнения (шаги UI2I и Ш22 алгоритма). Блок 8 управления опрашивает результаты сравнения (шаги F123 и Ш25 алгоритма). При обнаружении несоответствия (неисправности блока 13), т.е. г блок 8 управления останов ли-; вается и блок 10 индикации сигнализирует об этом (шаги Ш25 и Ш 26 алгоритма) .

При завершении тест-программы и при соответствии выходных сигналов блоков 13 и 5 ( О, шаг Ш27 алгоритма) в счетчике 18 восстанавливается начальный адрес программы, а в сумматоре 23 путем прибавления приращения из регистра 20 к содержанию регистра 22 определяется новый базовьп адрес операндов (шаг Ш29 , алгоритма). Затем тест-программа выполняется снова аналогично вышеописанному.

Окончание текущего цикла тест- программы определяется сигналом схемы 24 сравнения (X , I , maij Ш28 . алгоритма), которая фиксирует равенство базового адреса операндов и

конечного адреса массива операндов. При этом в регистре 22 восстанавливается адрес массива операндов путе его чтения из регистра 19. По адресу, хранимому в счетчике 16, происходит чтение из блока 1:1 памяти следующего управляющего слова вариации и передача его в регистр 26 (шаги ШЗ1 и Ш32 алгоритма). Затем тест-программа выполняется снова аналогично вышеописанному.

Тест завершен, если управляющее слово вариации содержит признак конца массива вариации (Х:, I, - шаг ШЗО алгоритма). Через третий выход регистра 26 этот признак пере ается в блок 8 управления. При .наличии в коде операции, хранимом в регистре 25, признака конца провеки f X О, шаг ШЗЗ алгоритма). работа устройства завершена и блок 8 управления приостанавливается (шаг ШЗЗ алгоритма). В противном случае устройство переходит к выполнению следующей тест-программы, адее которой был зафиксирован в регистре 14 и передается теперь в счетчик 18.

Устройство обеспечивает организацию циклов с глубиной один (по массиву операндов или по массиву вариаций,j а также с глубиной два В последнем случае заданная программа будет циклически модифицироваться согласно массиву вариаций, а каждая модификация программы будет циклически выполняться с разными операндами.

Формула изобретени

Устройство для тестового контроля больших интегральных схем, содержащее накопитель входных воздействий, первый блок сравнения, эта- лонньш блок, блок микропрограммного управления, блок индикации и блок памяти, причем niepBbrft выход блока микропрограммного управления соединен с управляющим входом блока памяти, информационный вход которог является входом тестовой информации устройства, второй выход блока микропрограммного управления соединен с управляющим входом первого блока сравнения, выход которого соединен с первым входом логических условий блока микропрограммного управления.

а первый и второй информационные входы - соответственно с выходами контролируемой большой интегральной схемы и эталонного блока, входы которых соединены с информационным выходом накопителя входных воздействий, разрешающий вход которо- го соединен с третьим выходом блока микропрограммного управления, четвертый выход которого соединен

с входом блока индикации, о т. л и - чающееся тем, что, с целью повышения коэффициента использования оборудования и достоверности

контроля, в устройство введены

второй блок сравнения, мультиплексор, блок формирования адресов операндов, блок формирования адресов команд и блок регистров, причем

пятый выход блока микропрограммного управления соединен с управляющим входом мультиплексора, первый, вто - рой и третий информационные входы которого соединены соответственно с

первым и вторым выходами блока формирования, адресов команд и информационным выходом блока формирования адресов операндов, а выход соединен с первым входом схемы сравнения и

адресным входом блока памяти, информационный выход которого соединен с информационным входом блока регистров , первьй и второй информационные выходы которого соединены

соответственно с вторым входом второго блока сравнения и информационными входами блоков формирования адресов операндов и команд, управляющие входы которых соединены соответственно с шестым и седьмым выходами блока микропрограммного управления, второй и третий входы логических условий которого соединены соответственно с выходом схемы

сравнения и выходом окончания цикла блока формирования адресов операндов, третий информационный выход блока регистров соединен с информационным входом накопителя входных воздействий, четвертый и пятый выходы и управляющий вход блока регистров соединены, соответственно с входами кода операций и кода модификации адреса и восьмым выходом блока микро

программного управления, причем

блок формирования адресов команд содержит два регистра, два счетчика, мультиплексор, информационные вх оды

первого н второго регистров и первого счетчика образуют информационный вход блока, а их управляющие входы и управляющий вход мультиплексора образуют управляющий вход блока формирования адресов команд, в котором первый и второй информационные входы мультиплексора соединены с выходами первого и второго регистров а выход соединен с входом второго счетчика, выход которого и выход первого счетчика являются соответственно первым и вторым выходами блока формирования адресов команд, а блок формирования адресов операндов содержит четыре регистра, сумматор и схему сравнения, при этом в блоке формирования адресов операндов информационные входы первого, второго и третьего регистров и пер:-1839012

вый информационный вход сумматора образуют информационный вход блока, выходы первого, второго и третьего регистров соединены соответственно 5 с первым информационным входом четвертого регистра, вторым информационным входом сумматора и первыц информационным входом схемы сравнения, второй информационный вход которой

to и третий информационный вход румма- тора соединены с вькодом четвёртого регистра, выход сумматора соединен с вторым информационным входом четвертого регистра и является ин-

15 формационным выходом блока, уп-- равляющие входы первого - четвертого регистров и сумматора образуют управляющий вход блока формирования адресов операн20 дов.

71218390

Управляющие сигналы блока управления

18

Таблица 2

1

1

2

1

-

,

У26 У27

гв

У 29

УЗО

26(3) 27(3) 27(3)

6

31(8) 34(8)

Бл, 6 Сеанс между объектом и тестером

реализован (при )

Бл. 6 Результат текущей проверки:

а) - неисправности нет .

б) - есть неисправность

Требуется вариация программы Признак конца цикла операндов

Требуется загрузка управляющих регистров

Признак конца проверки Вид адресации:

а)X О - непосредственная

информация;

б)X-, I - адресная информация

Бл, 25(3) Требуется реализация сеанса

(при X J 0)

Бл. 25(3) Требуется блокировка блока сравнения

Бл, 25(3) Признак конца тест-программы (при О)

Загрузка вариации Передача из регистра команды вариации

Блокирование результата теста (при Дополнение адреса кодом условия Останов блока управления

Таблица 3.

7-9

12

Бл, 25(3) Адрес управляющего регистра

а)

б)

в)Х,010

г)X,

д)Х,

е)X,

11

Бл. 26(3) Признак конца цикла вариаций

per II

начала теста;

програм счетчик вариаций; per. адреса начала операндов; per. длины массива операндов; per. адреса конца операндов

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение относится к области вычислительной техники, а именно к средствам для автоматического контроля микропроцессорных больших интегральных схем. Целью изобретения является повышение коэффициента использования оборудования и достоверности контроля. Цель достигается за счет введения в устройство, содержащее накопитель входных воздействий, блок сравнения, эталонный блок, блок микропрограммного управления, блок индикации и блок памяти, второго блока сравнения, мультиплексора, блока формирования адресов операндов, блока формирования адресов команд и блока регистров, осуществляющих более гибкий механизм формирования тестовых последовательностей. 9 ил. с S (Л го 00 со о

Itjfy.Jfl

19

20

21

Щ

ff36Jr.8ffi)

n

2J

efjtJ

Из f. if IS)

24

8S.8f3e)

/fsfjtll

25

26

ll3iJi.6(Z9} - 6 ел 8(Щ 31)

, 1v Zff4,JS,fSM20,2t,

27

д5л.А.

Из Ул. 8(29)

- вifл. 8(30) -Jf3Sff.8f29)

| ПРИБОР ДЛЯ РАЗРЕЗАНИЯ ГИПСОВОГО БЛОКА НА КУСКИ ПРИ МАССОВОМ ПРОИЗВОДСТВЕ ФОРМ ДЛЯ ОТЛИВКИ ЗАЩИТНЫХ ПЛАСТИНОК К ИСКУССТВЕННЫМ ЗУБАМ ТИПА СТИЛЛИ И ИМ ПОДОБНЫМ | 1925 |

|

SU3614A1 |

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

| Устройство для автоматическогоКОНТРОля бОльшиХ иНТЕгРАльНыХ CXEM | 1978 |

|

SU798841A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-15—Публикация

1984-08-25—Подача