Изобретение относится к вычйсли тельной технике и может использоваться в автоматических устройствах, к которым предъявляются требования повыгаенной надежности.

Цель изобретения повьппение достоверности работы устройства.

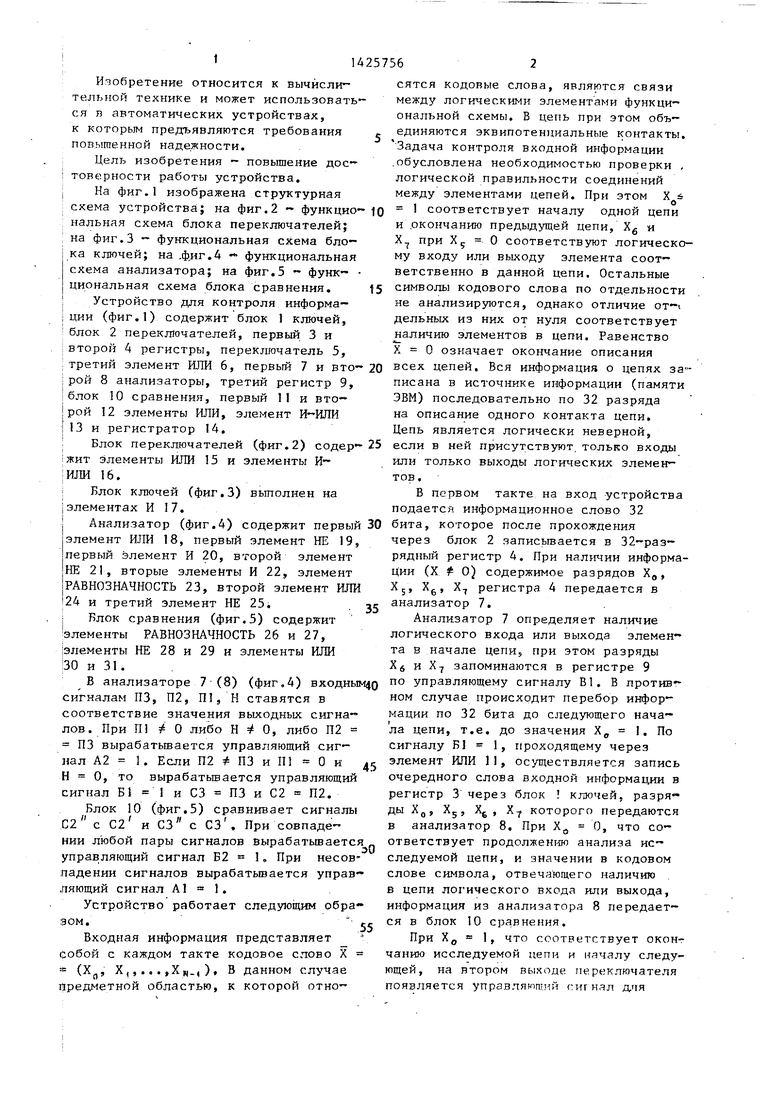

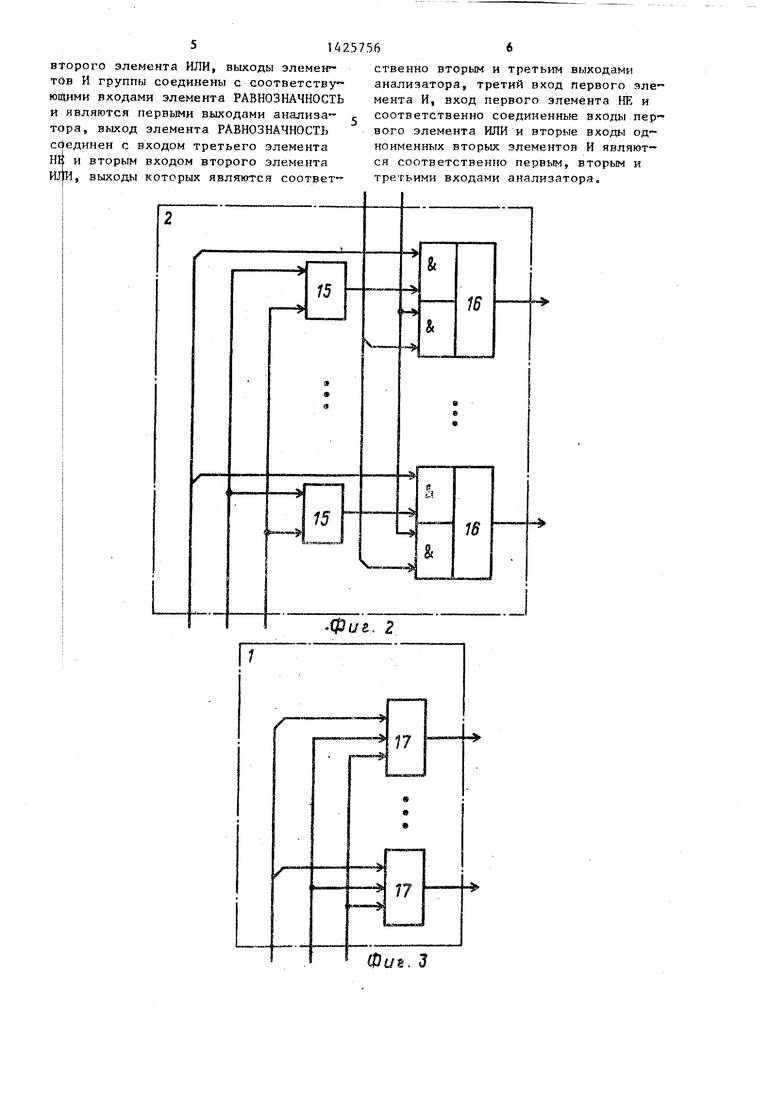

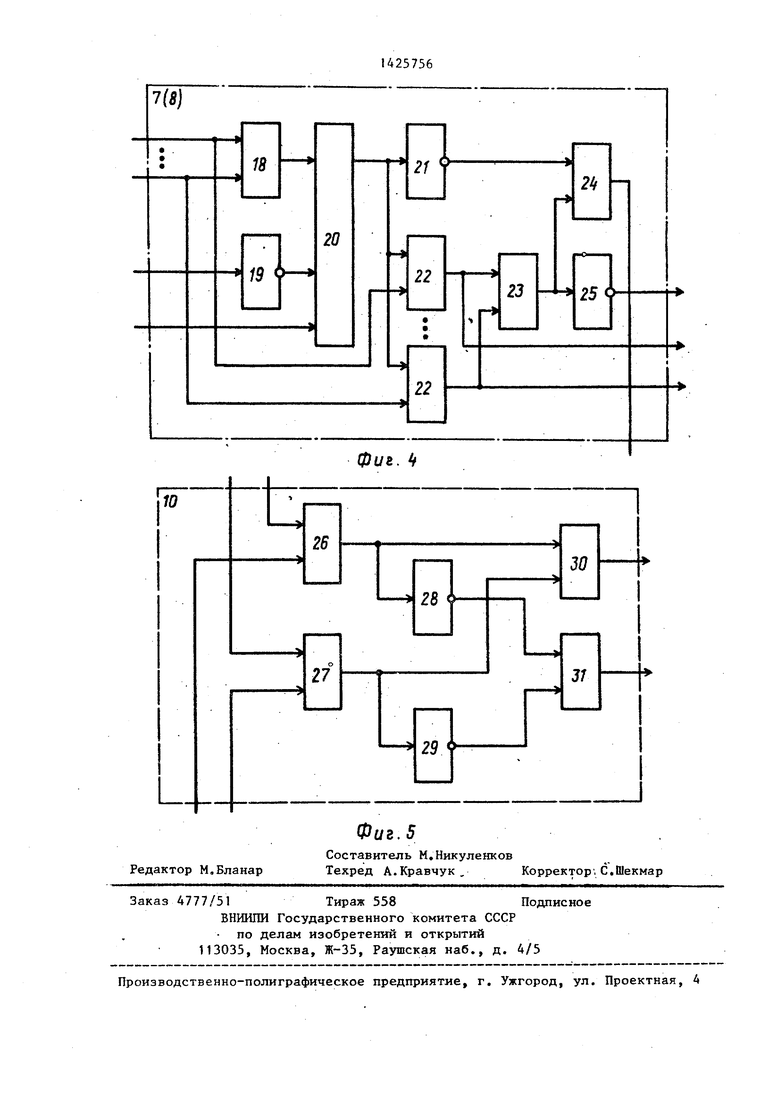

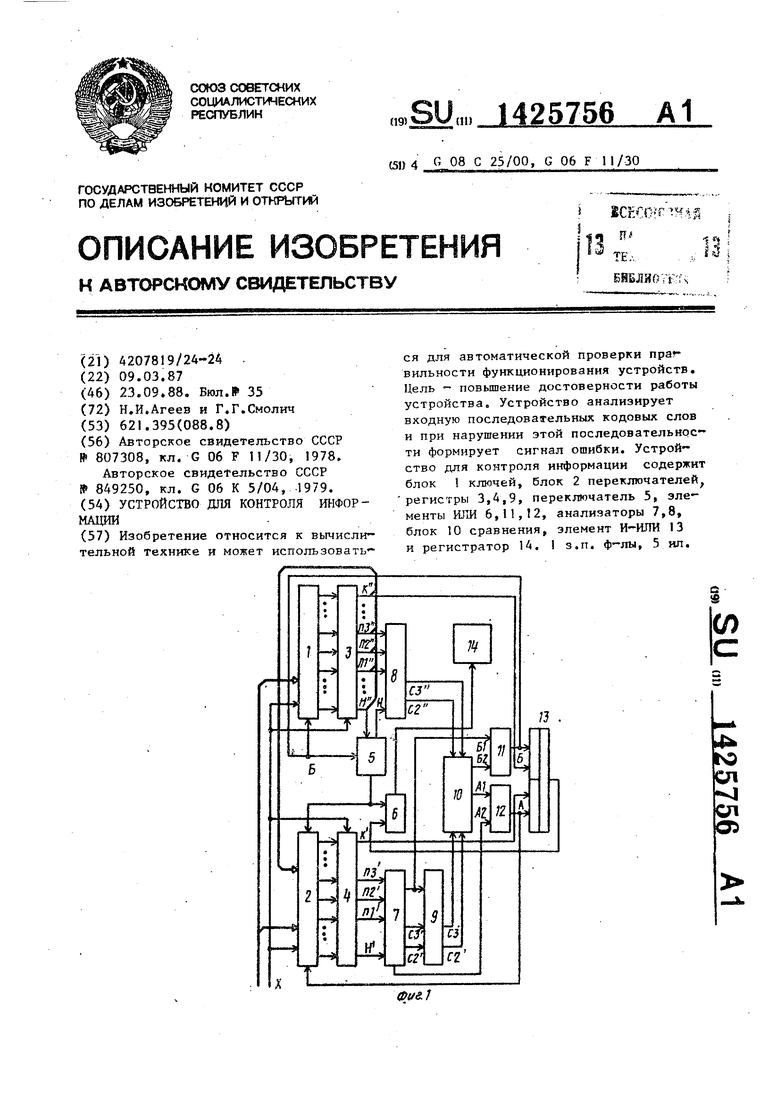

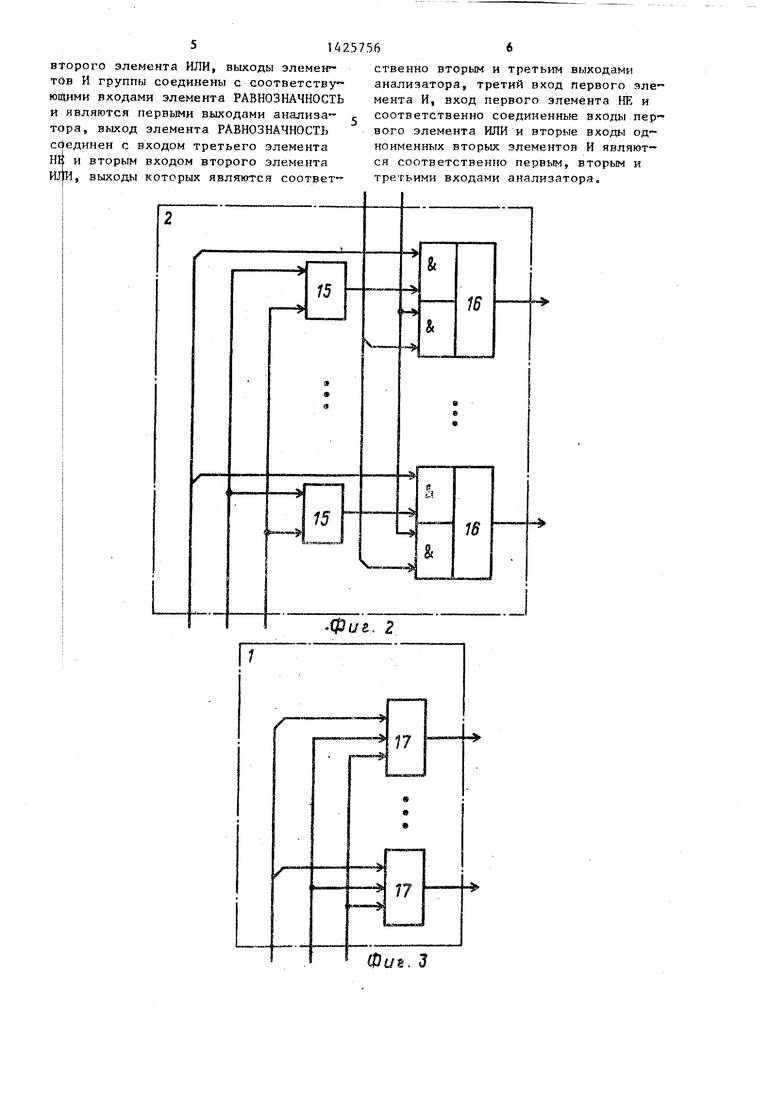

На фиг.1 изображена структурная схема устройства;; на фиг.2 - функцио- нальная схема блока переключателей; на фиг.З - функциональная схема блока ключей; на .ф,иг.4 функциональная схема анализатора; на фиг.5 - функ циональная схема блока сравнения. I Устройство для контроля информа- i цин (фиг.1) содержит блок 1 ключей, блок 2 переключателей, первый 3 и : второй 4 регистры, переключатель 5,

сятся кодовые слова, являются связи между логическими элементами функциональной схемы. В цепь при этом объединяются эквипотенциальные контакты. Задача контроля входной информации .обусловлена необходимостью проверки , логической правильности соединений между элементами цепей. При этом соответствует началу одной цепи и окончанию предыдущей цепи, Xg и Х при Х О соответствуют логическому входу или выходу элемента соответственно в данной цепи. Остальные символы кодового слова по отдельности не анализируются, однако отличие от-t дельных из них от нуля соответствует наличию элементов в цепи. Равенство X О означает окоргчание описания

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Логический анализатор | 1983 |

|

SU1170458A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки /ЭЛТ/ | 1989 |

|

SU1633387A1 |

| Устройство для дельта-модуляции | 1984 |

|

SU1241479A1 |

| Аналоговый декодер кода с ортогональными проверками | 1986 |

|

SU1401614A1 |

Изобретение относится к вычисли- тельной технике и может использовать ся для автоматической проверки праг вильности функционирования устройств. Цель повышение достоверности работы устройства. Устройство анализирует входную последовательных кодовых слов и при нарушении этой последовательности формирует сигнал ошибки. Устройство для контроля информации содержит блок 1 ключей, блок 2 переключателей регистры 3,4,9, переключатель 5, элементы ИЛИ 6,11,12, анализаторы 7,8, блок 10 сравнения, элемент И-ИЛИ 13 и регистратор 14, 1 з.п. ф-лы, 5 ил.

третий элемент ИЛИ 6, первый 7 и вто- 20 всех цепей. Вся информация о цепях заi рой 8 анализаторы, третий регистр 9, I блок 10 сравнения, первый 11 и вто-

писана в источнике информации (памяти ЭВМ) последовательно по 32 разряда на описание одного контакта цепи. Цепь является логически неверной. Блок переключателей (фиг. 2) содер-25 если в ней присутствуют, только входы

I рой 12 элементы ИЛИ, элемент И-ИЛИ i 13 и регистратор 14.

iжит элементы ИЛИ 15 и элементы И-

:шш 16.

: Блок ключей (фиг.З) вьтолнен на iэлементах И 17.

Анализатор (фиг.4) содержит первый 30 бита, которое после прохождения

элемент ИЛИ 18, первый элемент НЕ 19, первый элемент И 20, второй элемент НЕ 2, вторые элементы И 22, элемент IРАВНОЗНАЧНОСТЬ 23, второй элемент ИЛИ 24 и третий элемент НЕ 25. . 35 ; Блок сравнения (фиг.5) содержит элементы РАВНОЗНАЧНОСТЬ 26 и 27, элементы НЕ 28 и 29 и элементы ИЛИ 30 и 31.

В анализаторе 7 (8) (фиг,4) входным40 по управляющему сигналу В1. В противном случае происходит перебор информации по 32 бита до следующего начала цепи, т.е. до значения Х„ 1. По сигналу Б 1, проходящему через элемент ИЛИ 11, осуществляется запись очередного слова входной информации в регистр 3 через блок ключей, разря ды Хд, Xg , Xg , X-j, которого передаются в анализатор 8. При Х, О, что сосигналам ИЗ, П2, П, Н ставятся в соответствие значения выходных сигналов. При П О либо Н О, либо П2 ПЗ вырабатьшается управляющий сигнал А2 1. Если П2 18 ПЗ и П1 О и д Н О, то вырабатьшается управляющий сигнал Б1 1 и СЗ ПЗ и С2 П2.

Блок 10 (фиг.З) сравнивает сигналы С2 с С2 и СЗ с СЗ , При совпадении любой пары сигналов вырабатьшается „ ответствует продолжению анализа исуправляющий сигнал Б2 1. При несов падении сигналов вырабатьшается управляющий сигнал А1 1.

Устройство работает следующим образом. 55

Входная информация представляет собой с каждом такте кодовое слово X « (Х„, X,,...,Х„., ) В данном случае Предметной областью, к которой относледуемой цепи, и значении в кодовом слове символа, отвечающего наличию в цепи логического входа или выхода информация из анализатора 8 передает ся в блок 10 сравнения.

При XQ 1, что соответствует око чанию исследуемой цепи и началу след ющей, на втором выходе переключател появляется управляющий сигнал д.пя

или только выходы логических элементов.

В первом такте на вход устройства подается информационное слово 32

через блок 2 яаписьгоается в 32-разрядный регистр 4. При наличии информации (X Ф- О) содержимое разрядов Х,,, Хд, Xg, Х регистра 4 передается в анализатор 7.

Анализатор 7 определяет наличие логического входа или выхода элемен- та в начале цепи, при этом разряды Xj И XY запоминаются в регистре 9

по управляющему сигналу В1. В противном случае происходит перебор информации по 32 бита до следующего начала цепи, т.е. до значения Х„ 1. По сигналу Б 1, проходящему через элемент ИЛИ 11, осуществляется запись очередного слова входной информации в регистр 3 через блок ключей, разря ды Хд, Xg , Xg , X-j, которого передаются в анализатор 8. При Х, О, что соследуемой цепи, и значении в кодовом слове символа, отвечающего наличию в цепи логического входа или выхода, информация из анализатора 8 передается в блок 10 сравнения.

При XQ 1, что соответствует оконг чанию исследуемой цепи и началу следующей, на втором выходе переключателя появляется управляющий сигнал д.пя

фиксации ошибки и передачи информации из регистра 3 в регистр 4. Если при сравнении в блоке 10 сигналы окаэьта- ются одинаковыми, т.е. в исследуемой цепи до настоящего момента присутствуют только входы или только выходы, то анализу подвергается очередное слово информации 32 бит, запоминаемое в регистре 3 и поступающее в анализатор 8 и переключатель 5. При неравенстве информации, поступающей в блок 10 сравнения, исследуемая цепь считается логически верной и анализ начинается с новой цепи. Контроль информации завершается, когда на входы элемента 13 поступает сигнал К 0 либо К 0. При А 1 происходит нормальное завершение контроля очередной цепи, при Б 1 происходит завершение контроля -информации с фиксацией ошибки в последней цепи.

Предлагаемое устройство позволяет по сравнению с известным производить проверку входной информации по совпадению нескольких критериев, что повышает достоверность раб|Оты устройства.

Формула изобретения

I. Устройство для контроля инфор е мации, содержащее регистры, тактовый вход первого регистра является такто - 35 вым входом устройства, и блок сравне- ния, отличающее.ся тем, что, с целью повышения достоверности работы устройства, в него блок ключей, блок переключателей, 40 переключатель, анализаторы, элементы ИЛИ и элемент И-ИЛИ, информационные входы блока ключей объединены соответ- ствешшо с одноименными первыми

второго и последующих разрядов которого, кроме выхода последнего , азряда, соеди- нены с соответствзпощими первым,вторым и третьими входами первого анализатора, первые,второй и третий выходы которого соединены соответственно с однош- еы- ными информационными входами третьего регистра, объединенными тактовь м вхог дом третьего регистра и первым входом первого элемента ИЛИ, и первым входом второго элемента 1ШИ, выходы третьего регистра соединены с эдноимен{пыми первыми входами блока сравнения, пер- вый и второй выходы которого соединены с вторыми входами соответственно первого и второго элементов ИЛИ, вьг ход первого элемента ИЛИ соединен с первым входом элемента И-ИЛИ, управляющим входом блока ключей и информационным входом переключателя, управляющий вход, первый и второй выходы переключателя соединены соответствен - но с выходом первого разряда первого регистра, первым входом второго анализатора и объединенными первым управляющим Входом блока переключателей и первым входом третьего элемента ИЛИ, второй и третий входы второго анали затора подключены соотватственно к выходам второго и последующих разрядов первого регистра, кроме выходов первого и последнего разрядов, первые выходы второго анализатора соединень с одноименными вторыми входами блока сравнения, выход второго элемента И.ПИ соединен с вторым входом элемента И- ИЛИ и вторым управляющш-i входом блока переключателей, выход последнего разряда второго регистра соединен с третьим входом элемента И-ИЛИ, четвертый вход и выход которого подключены соответственно к выходу последнего разряда первого регистра и второму входу

информационными входами блока пере- 45 третьего элемента ИЛИ,вьисод которого

является выходом устройства.

ключателей и являются информационными входами устройства, тактовые входы блока ключей, блока переключателей и

второ: о регистра подключены к тактоI

вому входу устройства, выходы блока

ключей соединены с одноименными информационными входами первого регист ра, выходы всех разрядов которого соединены с одноименными вторыми инфорi

50

является выходом устройства.

элементов И группы, выход второго элемента НЕ соединен с первым входом

5 0

5

0

5 0

второго и последующих разрядов которого, кроме выхода последнего , азряда, соеди- нены с соответствзпощими первым,вторым и третьими входами первого анализатора, первые,второй и третий выходы которого соединены соответственно с однош- еы- ными информационными входами третьего регистра, объединенными тактовь м вхог дом третьего регистра и первым входом первого элемента ИЛИ, и первым входом второго элемента 1ШИ, выходы третьего регистра соединены с эдноимен{пыми первыми входами блока сравнения, пер- , вый и второй выходы которого соединены с вторыми входами соответственно первого и второго элементов ИЛИ, вьг ход первого элемента ИЛИ соединен с первым входом элемента И-ИЛИ, управляющим входом блока ключей и информационным входом переключателя, управляющий вход, первый и второй выходы переключателя соединены соответствен - но с выходом первого разряда первого регистра, первым входом второго анализатора и объединенными первым управляющим Входом блока переключателей и первым входом третьего элемента ИЛИ, второй и третий входы второго анали затора подключены соотватственно к выходам второго и последующих разрядов первого регистра, кроме выходов первого и последнего разрядов, первые выходы второго анализатора соединень с одноименными вторыми входами блока сравнения, выход второго элемента И.ПИ соединен с вторым входом элемента И- ИЛИ и вторым управляющш-i входом блока переключателей, выход последнего разряда второго регистра соединен с третьим входом элемента И-ИЛИ, четвертый вход и выход которого подключены соответственно к выходу последнего разряда первого регистра и второму входу

третьего элемента ИЛИ,вьисод которого

является выходом устройства.

торого соединен с первым входом вто- рого элемента НЕ и первыми входами

элементов И группы, выход второго элемента НЕ соединен с первым входом

51425

второго элемента ИЛИ, выходы элемен тов И группы соединены с соответству- юйими входами элемента РАВНОЗНАЧНОСТЬ и являются первыми выходами анализатора, выход элемента РАВНОЗНАЧНОСТЬ сдединен с входом третьего элемента НИ и вторым входом второго элемента ИЛИ, выходы которых являются соответ

6

ственно вторым и третьим выходами анализатора, третий вход первого элемента И, вход первого элемента НЕ и соответственно соединенные входы первого элемента ИЛИ и вторые входы одноименных вторых элементов И являются соответственно первым, вторым и третьими входами аналиэатора.

18

19 Ф-

Редактор М.Бланар

Составитель М.Никуленков

Техред А.Кравчук, Корректор,С.Шекмар

21

2if

22

23

250фиг.

Фиг.5

| Устройство для контроля распредели-ТЕля иМпульСОВ | 1978 |

|

SU807308A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и коррек-ТиРОВКи иНфОРМАции | 1979 |

|

SU849250A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-09—Подача