4 N9 СП

00

о

00

Изобретение относится к электросвязи и может быть использовано в стьжовом приемном оборудовании основного цифрового 1 анала.

Цель изобретения - повышение достоверности приема и сокращение времени вхождения в синхронизм.

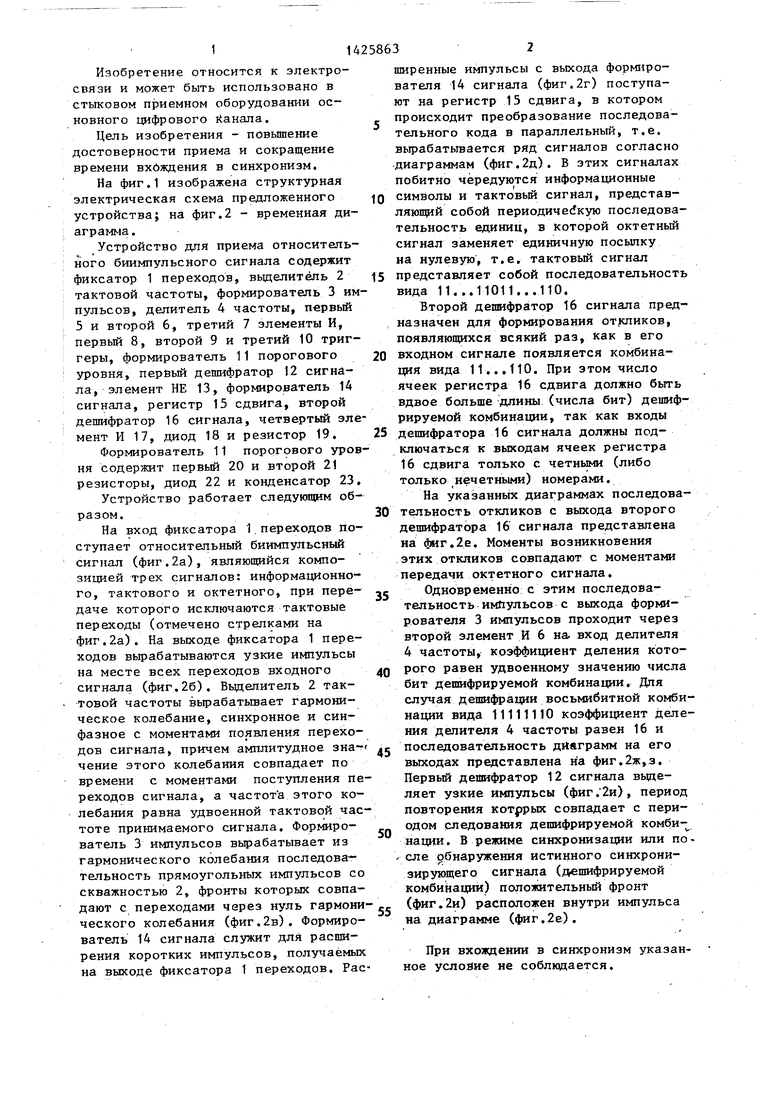

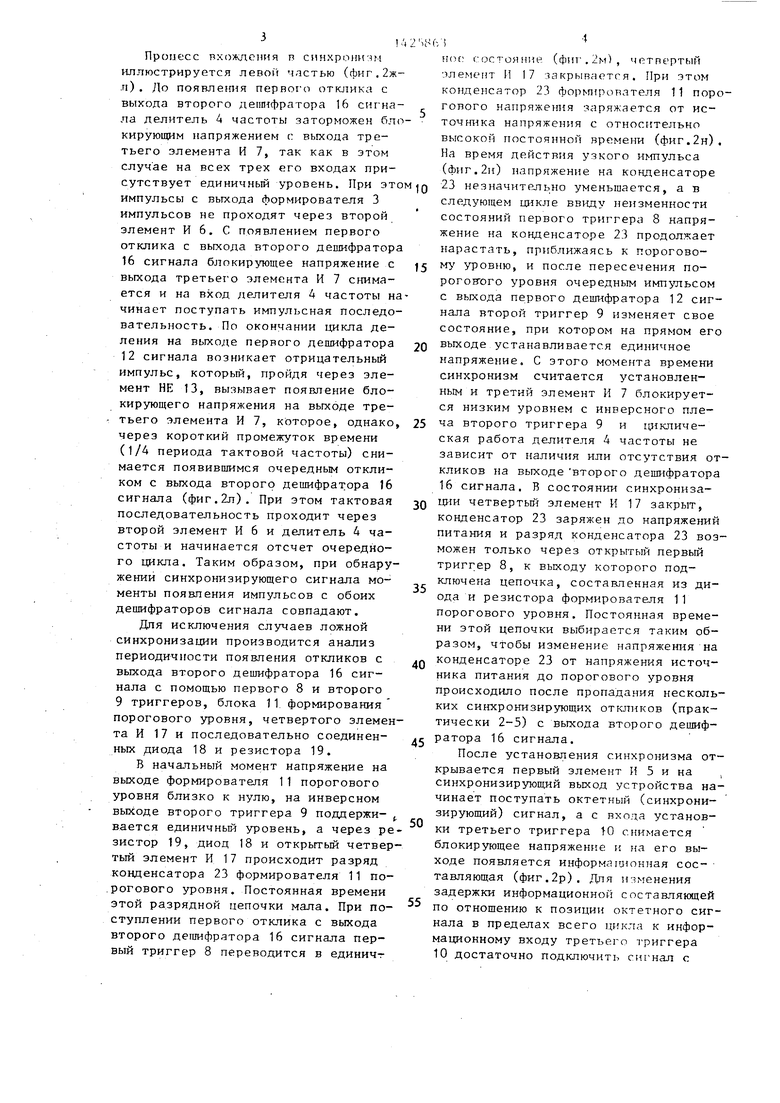

На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг.2 - временная диаграмма .

Устройство для приема относительного биимпульсного сигнала содержит фиксатор 1 переходов, выделитель 2 тактовой частоты, формирователь 3 импульсов, делитель 4 частоты, первый 5 и второй 6, третий 7 элементы И, первый 8, второй 9 и третий 10 триггеры, формирователь 11 порогового уровня, первый дешифратор 12 сигнала, элемент НЕ 13, формирователь 14 сигнала, регистр 15 сдвига, второй дешифратор 16 сигнала, четвертый элемент И 17, диод 18 и резистор 19.

Формирователь 11 порогового уровня содержит первый 20 и второй 21 резисторы, диод 22 и конденсатор 23,

Устройство работает следующим образом.

На вход фиксатора 1 переходов поступает относительный биимпульсный сигнал (фиг.2а), являющийся композицией трех сигналов: информационного, тактового и октетного, при передаче которого исключаются тактовые переходы (отмечено стрелками на фиг.2а). На выходе фиксатора 1 переходов вырабатываются узкие импульсы на месте всех переходов входного сигнала (фиг.26). Вьщепитель 2 тактовой частоты вырабатьшает гармоническое колебание, синхронное и синфазное с моментами появления переходов сигнала, причем амплитудное значение этого колебания совпадает по времени с моментами поступления переходов сигнала, а частот а этого колебания равна удвоенной тактовой частоте принимаемого сигнала. Формирователь 3 импульсов вырабатывает из гармонического колебания последова- тельность прямоугольных импульсов со скважностью 2, фронты которых совпадают с переходами через нуль гармонического колебания (фиг.2в). Формирователь 14 сигнала служит для расширения коротких импульсов, получаемых на выходе фиксатора 1 переходов. Рас0

5

0

5

0

5

0

5

0

5

ширенные импульсы с выхода форм1 ро- вателя 14 сигнала (фиг.2г) поступают на регистр 15 сдвига, в котором происходит преобразование последовательного кода в параллельный, т.е. вырабатывается ряд сигналов согласно диаграммам (фиг.2д). В этих сигналах побитно чередуются информационные символы и тактовый сигнал, представляющий собой пepиoдичedкyю последовательность единиц, в Которой октетный сигнал заменяет единичную посьшку на нулевую, т.е. тактовый сигнал представляет собой последовательность вида 11...11011...110.

Второй дешифратор 16 сигнала предназначен для формирования откликов, появляющихся всякий раз, как в его входном сигнале появляется комбина- дая вида 11...110. При этом число ячеек регистра 16 сдвига должно быть вдвое больше длины (числа бит) дешифрируемой комбинации, так как входы дешифратора 16 сигнала должны подключаться к выходам ячеек регистра 16 сдвига только с четнь1ми (либо только нечетными) номерами.

На указаннь1х диаграммах последовательность откликов с выхода второго дешифратора 16 сигнала представлена на фиг.2е. Моменты возникновения этих откликов совпадают с моментами передачи октетного сигнала.

Одновременно с этим последовательность импульсов с выхода формирователя 3 импульсов проходит через второй элемент И 6 на вход делителя 4 частоты, коэффициент деления которого равен удвоенному значению числа бит дешифрируемой комбинации. Для случая дешифрации восьмибитной комбинации вида 11111110 коэффициент деления делителя 4 частоты равел 16 и последовательность диаграмм на его выходах представлена на фиг,2ж,з. Первый дешифратор 12 сигнала вьще- ляет узкие импульсы (фиг;2и), период повторения котррых совпадает с периодом следования дешифрируемой комби- нации. В режиме синхронизации или по- г еле обнаружения истинного синхронизирующего сигнала (дешифрируемой комбинации) положительньш фронт (фиг.2и) расположен внутри импульса на диаграмме (фиг.2е).

При вхождении в синхронизм указанное условие не соблюдается.

Проиесс вхождения п сянхр1.-1нкзм иллюстрируется левой частью (фиг.2ж- л) . До появле {ия первого отклика с выхода второго депп-гфратора 16 снг на- ла делитель 4 частоты заторможен блокирующим напряжением t: выхода третьего элемента И 7, так как в этом случае на всех трех его входах присутствует единичный уровень. При это импульсы с выхода формирователя 3 импульсов не проходят через второй элемент И 6. С появлением первого отклика с выхода второго дешифратора 16 сигнала блокирующее напряжение с выхода третьет о элемента И 7 снимается и на вход делителя 4 частоты начинает поступать импульсная последовательность. По окончании деления на выходе первого дешифратора 12 сигнала возникает отрицательный импульс, который, пройдя через элемент НЕ 13, вызывает появление блокирующего напряжения на выходе третьего элемента И 7, которое, однако, через короткий промежуток времени (1/4 периода тактовой частоты) снимается появившимся очередным откликом с выхода второго дешифратора 16 сигнала (фиг.2л). При этом тактовая последовательность проходит через второй элемент И 6 и делитель 4 частоты и начинается отсчет очередного цикла. Таким образом, при обнаружении синхронизирующего сигнала моменты появления импульсов с обоих дешифраторов сигнала совпадают.

Для исключения случаев ложной синхронизации производится анализ периодичности появления откликов с выхода второго дешифратора 16 сигнала с помощью первого 8 и второго 9 триггеров, блока 11 формирования порогового уровня, четвертого злемен та И 17 и последовательно соединенных диода 18 и резистора 19.

В начальный момент напряжение на выходе формирователя 11 порогового уровня близко к нулю, на инверсном выходе второго триггера 9 поддержи- вается единичный уровень, а через резистор 19, диод 18 и открытый четвертый элемент И 17 происходит разряд конденсатора 23 формирователя 11 по- .рогового уровня. Постоянная времени этой разрядной цепочки мала. При поступлении первого отклика с выхода второго дешифратора 16 сигнала первый триггер 8 переводится в единич

0

5

0

5

0

5

0

5

4

; )

Н(н: состояние (фит.2м), четвертый элемент И 17 закрыг аетгя. При этом конденсатор 23 фор троиателя 11 порогового напряжения заряжается от источника напряжения с относительно высокой постоянной времени (фиг.2н). На время действия узкого и тульса (фиг.2и) напряжение на конденсаторе 23 незначительно уменьшается, а в следующем цикле ввиду неизменности состояний первого триггера 8 напряжение на конденсаторе 23 продолжает нарастать, приближаясь к пороговому уровню, и после пересечения по- рогоЕГого уровня очередным импульсом с выхода первого дешифратора 12 сигнала второй триггер 9 изменяет свое состояние, при котором на прямом его выходе устанавливается еди}1ичное напряжение. С этого момента времени синхронизм считается установленным и третий элемент И 7 блокируется низким уровнем с инверсного плеча второго триггера 9 и 1Ц1кпиче- ская работа делителя 4 частоты не зависит от наличия или отсутствия откликов на выходе второго дешифратора 16 сигнала. В состоянии синхронизации четвертьпЧ элемент И 17 закрыт, конденсатор 23 заряжен до напряжений питания и разряд конденсатора 23 возможен только через открытый первый тригг;ер 8, к выходу которого подключена цепочка, составленная из диода и резистора формирователя 11 порогового уровня. Постоянная времени этой цепочки выбирается таким образом, чтобы изменение напряжения на конденсаторе 23 от напряжения источника питания до порогового уровня происходило после пропадания нескольких синхронизирующих откликов (практически 2-5) с выхода второго дешифратора 16 сигнала.

После установления синхронизма открывается первый элемент И 5 и на , синхронизирующий выход устройства начинает поступать октетный (синхронизирующий) сигнал, а с входа установки третьего триггера Ю снимается блокирующее напряжение и на его выходе появляется информаш онная сое- тавляющая (фиг.2р). Дпя из eнeния задержки информационной составляющей по отношению к позиции октетного сигнала в пределах всего цикла к информационному входу третьего триггера 10 достаточно подключить сигнал с

I

соответстнующег о пыходл рот истра 15 сдшп а.

Формула изобретения

Устройство для приема относительного биимпульсного сигнала, содержащее фиксатор переходов, выход которого через вьщелитель тактовой .частоты соединены с входом формирователя импульсов, первый триггер, выход которого соединен с входом фор ;мирователя порогового уровня, выход которого соединен с первым входом второго триггера, единичный выход которого подключен к первому входу первого элемента И, второй и третий ;элементы И, делитель частоты, первый выход которого соединен с первым входом третьего триггера, отличающееся тем, что, с целью повьпиения достоверности приема и сокращения времени вхождения в синхронизм, введены четвертый элемент И, диод, резистор, первый и второй депифраторы сигнала, регистр сдвига, фор№1рователь С1 гнала и элемент НЕ, выход которого соединен с первым входом третьего элемента И, с вторым входом первого элемента И и с первым входом четвертого элемента И, выход которого по71ключен к катоду диода, анод которого через ре

36

зистор подключен к первому входу второго триггера, второй вход )ро- го подк.чючен к первому входу первого триггера, к входу элемента НЕ и к выходу первого депшфратора сигнала, первый и второй входы которого под- Ю1ючены соответственно к первому и второму выходам делителя частоты,

вход которого подключен к В1 гходу второго элемента И, первый вход которого соединен с выходом формирователя импульсов, с первым входом формирователя сигнала и с первым входом

регистра сдвига, первый выход которого соединен с первым входом второго дешифратора сигнала и с вторым входом третьего триггера, третий вход которого подключен к инверсному выходу второго триггера, к второму

входу четвертого элемента И и к второму входу третьего элемента И,третий вход которого подключен к второму входу первого триггера и к выходу второго дешифратора сигнала, второй вход которого подключен к второму выходу регистра сдвига, второй вход которого подключен к выходу фор- мирователя сигнала, второй вход которого соединен с выходом фиксатора переходов, выход третьего элемента И подключен к второму входу второго элемента И.

0 1 1 0 0 1 0 1 1 1 0 1 0 1 1 0

I .J

твяяш

я I 11 11 I 111 III111 111 I 11111 JlлЛJlmгплJIJlпллnл

«JгJlЛ-лл.-Л-JГ лn-Jl гглJLJ лллл-ГL.

LJ LT

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный приемник относительного биимпульсного сигнала | 1988 |

|

SU1601768A1 |

| Приемник относительного биимпульсного сигнала | 1986 |

|

SU1327306A1 |

| Анализатор состояний приемника цикловой синхронизации | 1984 |

|

SU1350838A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| РЕЛЕ ВРЕМЕНИ | 2002 |

|

RU2219613C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности приема и сокращение времени вхождения в синхронизм. Устр-во содержит фиксатор 1 переходов, вьщелитель 2 тактовой частоты, формирователь (Ф) 3 импульсов, делитель 4 частоты, эл-ты И 5-7 и 17, триггеры 8-10, Ф 11 порогового уровня, дешифратор 12 и 16 сигнала, эл-т НЕ 13, Ф 14 сигнала;, регистр 15 сдвига, диод 18 и резистор 19. Для исключения случаев ложной синхронизации производится анализ периодичности появления откликов с выхода дешифратора 16 с помощью триггеров 8 и 9, Ф 11, эл-та И 17 и последовательно соединенных диода 18 и резистора 19. 2 ил.

LI

X

u

u

JofoioBbiu ень

и

u

u

| Авторское свидетельство СССР | |||

| Приемник относительного биимпульсного сигнала | 1986 |

|

SU1327306A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-27—Подача