Изобретение относится к электросвязи и может использоваться в приемниках цикловой синхронизации многоканальных цифровых систем передачи,

Цель изобретения - повышение помехозащищенности приема цифровой информации,

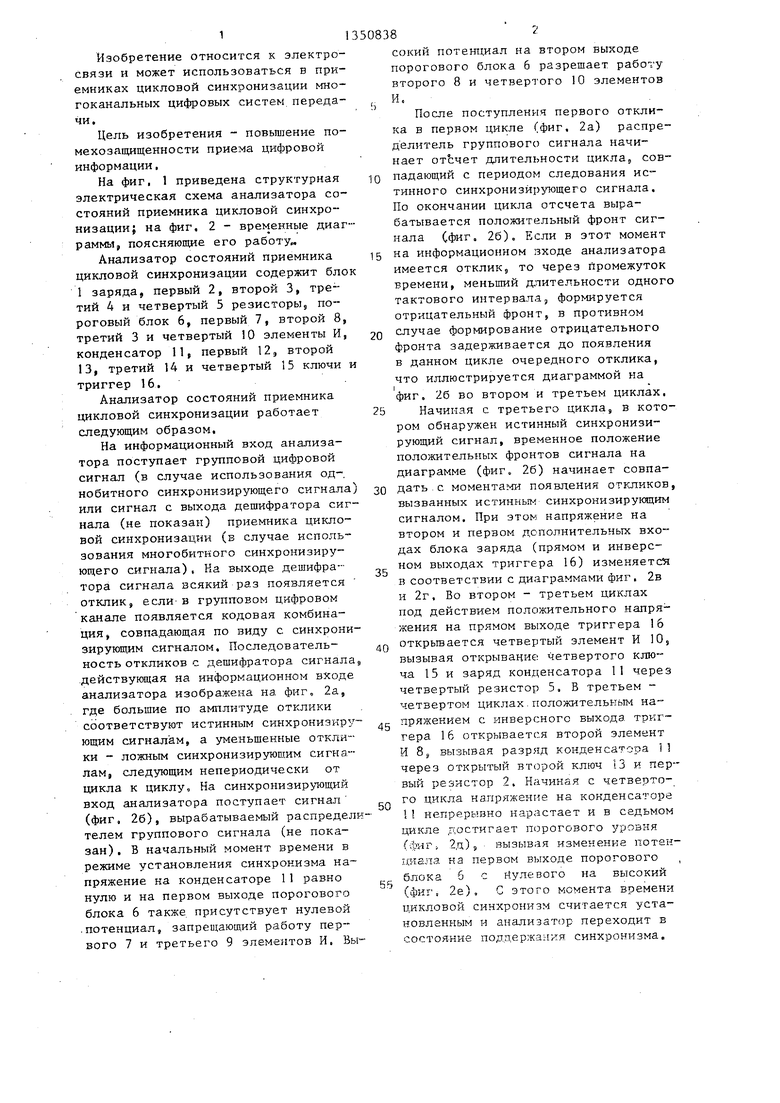

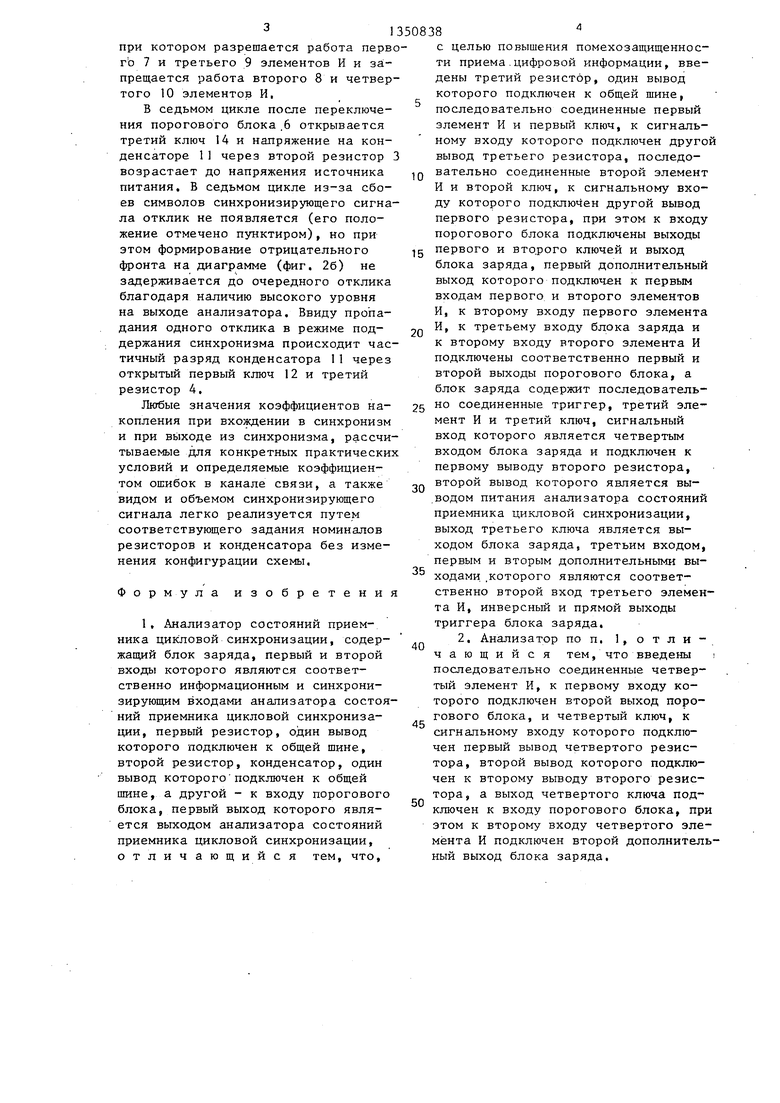

На фиг, 1 приведена структурная электрическая схема анализатора состояний приемника цикловой синхронизации; на фиг, 2 - временные диаграммы, поясняющие его работу,,

Анализатор состояний приемника цикловой синхронизации содержит бло 1 заряда, первый 2, второй 3, третий А и четвертый 5 резисторы5 пороговый блок 6, первый 7, второй 8, третий 3 и четвертый 10 элементы И, конденсатор 11, первый 12, второй 13, третий 14 и четвертый 15 ключи триггер 16.

Анализатор состояний приемника цикловой синхронизации работает следующим образом,

На информационный вход анализатора поступает групповой цифровой сигнал (в случае использования однобитного синхронизирующего сигнала или сигнал с выхода дешифратора сигнала (не показан) приемника цикловой синхронизации (в случае использования многобитного синхронизирующего сигнала), На выходе дешифратора сигнала всякий раз появляется отклик, если-в групповом цифровом

канале появляется кодовая комбинация, совпадающая по виду с синхронизирующим сигналом. Последовательность откликов с дешифратора сигнала

.действукщая на информационном входе анализатора изображена на фиг, 2а, где большие по амплитуде отклики соответствуют истинным синхронизирующим сигналам, а уменьщен 1ые отклики - ложным синхронизирующим сигналам, следующим непериодически от цикла к циклу. На синхронизирующий вход анализатора поступает сигнал (фиг, 26), вырабатываемый распределтелем группового сигнала (не показан) , В начальный момент времени в режиме установления синхронизма напряжение на конденсаторе 11 равно нулю и на первом выходе порогового блока 6 также присутствует нулевой

.потенциал, запрещающий работу первого 7 и третьего 9 элементов И. Вы0

5

5

0

5

0

5

0

сокий потенциал на втором выходе порогового блока 6 разрешает работу второго 8 и четвертого 10 элементов И.

После поступления первого отклика в первом цикле (фиг, 2а) распределитель группового сигнала начинает отЬчет длительности цикла совпадающий с периодом следования истинного синхронизирующего сигнала. По окончании цикла отсчета вырабатывается положительный фронт сигнала СФиг, 26), Если в этот момент на информационном зходе анализатора имеется отклик, то через йромежуток времени, меньший длительности одного тактового интервала, формируется отрицательный фронт, в противном случае формирование отрицательного фронта задерживается до появления в данном цикле очередного отклика, что иллюстрируется диаграммой на фиг, 26 во втором и третьем циклах.

Начиная с третьего цикла, в котором обнаружен истинный синхронизирующий сигнал, временное положение положительных фронтов сигнала на диаграмме (фиг. 26) начинает совпадать с моментами появления откликов, вызванных истинным синхронизирукщим сигналом. При этом напряженна на втором и первом дополнительных входах блока заряда (прямом и инверсном выходах триггера 16) изменяется в соответствии с диаграммами фнг, 2в н 2г, Во втором - третьем циклах под действием положительного напряжения на прямом выходе триггера 16 открьшается четвертый элемент И lOj вызывая открывание четвертого ключа 15 и заряд конденсатора 11 через четвертый резистор 5, В третьем - четвертом циклах.положительным напряжением с инверсного выхода триггера 16 открывается второй элемент И 8„ вызывая разряд конденсатора 11 через открытый второй ключ 13 и первый резистор 2, Начиная с четвертого цикла напряженна на конденсаторе I непрерывно нарастает и в седьмом цикле достигает порогового уровня

2д),

вызывая измекение потен

циала на первом выходе порогового блока б с Нулевого на высокий (фиг, 2е), С этого момента времени цикловой синхронизм считается установленным и анализатор переходит в состояние поддержания синхронизма.

при котором разрешается работа первго 7 и третьего 9 элементов И и за;- прещается работа второго 8 и четвертого 10 элементов И.

В седьмом цикле после переключения порогового блока .6 открывается третий ключ 14 и напряжение на конденсаторе 11 через второй резистор возрастает до напряжения источника питания, В седьмом цикле из-за сбоев символов синхронизирующего сигнала отклик не появляется (его положение отмечено пунктиром), но при этом формирование отрицательного фронта на диаграмме (фиг, 2б) не задерживается до очередного отклика благодаря наличию высокого уровня на выходе анализатора. Ввиду пропадания одного отклика в режиме поддержания синхронизма происходит частичный разряд конденсатора 11 через открытый первый ключ 12 и третий резистор 4,

Любые значения коэффициентов накопления при вхождении в синхронизм и при выходе из синхронизма, рассчитываемые для конкретных практически условий и определяемые коэффициентом ошибок в канале связи, а также видом и объемом синхронизирующего сигнала легко реализуется путем соответствующего задания номиналов резисторов и конденсатора без изменения конфигурации схемы.

Формула изобретени

1, Анализатор состояний приемника цикловой синхронизации, содержащий блок заряда, первый и второй входы которого являются соответственно информационным и синхронизирующим входами анализатора состояний приемника цикловой синхронизации, первый резистор, один вывод которого подключен к общей шине, второй резистор, конденсатор, один вывод которого подключен к общей шине, а другой - к входу порогового блока, первый выход которого является выходом анализатора состояний приемника цикловой синхронизации, отличающийся тем, что.

0

5

с целью повышения помехозащищенности приема.цифровой информации, введены третий резистор, один вывод которого подключен к общей шине, последовательно соединенные первый элемент И и первый ключ, к сигнальному входу которого подключен другой вывод третьего резистора, последовательно соединенные второй элемент И и второй ключ, к сигнальному входу которого подключен другой вывод первого резистора, при этом к входу порогового блока подключены выходы первого и второго ключей и выход блока заряда, первый дополнительный выход которого подключен к первым входам первого и второго элементов И, к второму входу первого элемента И, к третьему входу блока заряда и к второму входу второго элемента И подключены соответственно первый и второй выходы порогового блока, а блок заряда содержит последователь- 5 но соединенные триггер, третий элемент И и третий ключ, сигнальный вход которого является четвертым входом блока заряда и подключен к первому выводу второго резистора, второй вывод которого является вы- .водом питания анализатора состояний приемника цикловой синхронизации, выход третьего ключа является выходом блока заряда, третьим входом, первым и вторым дополнительными выходами .которого являются соответственно второй вход третьего элемента И, инверсный и прямой выходы триггера блока заряда,

2, Анализатор по п. 1, о т л и - чающийся тем, что введены i последовательно соединенные четвертый элемент И, к первому входу которого подключен второй выход порогового блока, и четвертый ключ, к сигнальному входу которого подключен первый вывод четвертого резистора, второй вывод которого подключен к второму выводу второго резис0

5

0

5

50

тора, а выход четвертого ключа подключен к входу порогового блока, при этом к второму входу четвертого элемента И подключен второй дополнительный выход блока заряда.

J /у

п jiJbijiJl IL

1IIIг

n.

)

п IL

I1II

h hh K,. h

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема относительного биимпульсного сигнала | 1987 |

|

SU1425863A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1992 |

|

RU2019046C1 |

| Устройство для цикловой синхронизации | 1990 |

|

SU1786675A1 |

| Приемник относительного биимпульсного сигнала | 1986 |

|

SU1327306A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

Изобретение относится к электросвязи и обеспечивает повышение помехозащищенности приема цифровой информации. Анализатор содержит блок 1 заряда, состоящий из триггера 16, элемента И 9 и ключа 14, резисторы 2-5, пороговый блок (ПБ) 6, элементы И 7, 8, 10, конденсатор 11 и ключи 12, 13, 15. В режиме установления синхронизма на прямом выходе ПБ 6 (выходе устр-ва) присутствует нулевой потенциал, который запреща- , ет работу элементов И 7, 9. Высокий потенциал на втором выходе ПБ 6 разрешает работу элементов И 8, 10. При поступлении на вход анализатора первого отклика на кодовую комбинацию, совпадающую по виду с синхронизирующим сигналом, начинается отсчет длительности цикла, совпадающего с периодом следования истинного синхронизирующего сигнала, Триггер 16 формирует сигнал рассогласования. При положит, напряжении на прямом выходе триггер 16 через открытый ключ 15 происходит заряд конденсатора П. При положит, напряжении на инверсном выходе триггера 16 через открытый ключ 13 и резистор 2 происходит разряд конденсатора 11. При достижении напряжением на конденсаторе 1I порогового уровня ПБ 6 на его выходе формируется высокий потенциал, соотв. установлению синхронизма, 1 з.п. ф-лы, 2 ил. i(Л С ел

и

лор

CPU г. 2.

| Gray Т | |||

| R., Pan Т | |||

| W | |||

| Using Didit Statisties to Word-Frame PCM Signals | |||

| - Itie Bell System Technical Tornal, 1964, vol | |||

| XLIII, № 6, fig | |||

| Насос | 1917 |

|

SU13A1 |

| I | |||

Авторы

Даты

1987-11-07—Публикация

1984-11-29—Подача