Изобретение относится к контрольно-измерительной технике и может быть использовано в автоматизированных устройствах управления и контроля электронных систем различного назначения..

По основному авт.св. 980027 известно устройство для автоматического контроля электронных систем содержащее ЭВМ, соединенную черезконтроллер с управляющим входом первого ксиимутатора, выходы первого коммутаторд соединены с клеммами дл подключения входов объекта контроля входы первого шифратора соединены с выходами первого коммутатора, а выход - с магистральными шинами контроллера, входы второго и третьего шифраторов соединены между собой и с клеммами для подключения выходов объекта контроля, а выходы соединены соответственно с входами пятого и шестого регистров пг№1яти, входы первого, второго, третьего и четвертого регистров памяти соединены с магистральньа и и соответствующими адресными шинами контроллера, выходы,первого и второго регистров памяти соединены соответственно с первым и вторым входами первого логического элемента эквивалентности, выход третьего регистра памяти соединен с первыми входами второго и четвертого элементов эквивалентности, выход четвертого регистра памяти соединен с первыми входами третьего и пятого элементов эквивалентности, входы пятого и шестого регистров памяти соединены с выходами второго и третьего шифраторов соответственно, а выход пятого регистра памяти соединен с вторыми входами второго и третьего элементов эквивалентности, выход шестого регистра памяти соединен с вторьоми входами четвертого и пятого элементов эквивалентности , выход пятого элемента эквивалентности соединен с входом мла,чшего разряда дешифратора, а выходы четвертого, третьего, второго и первого элементов эквивалентности соответственно с входами последующих разрядов дешифратора, выходы пятиразрядного дешифратора с тридцать первого по двадцать восьмой , с двадцать седьмого по двадцать четвертый, с Двадцать третьего по двадцатый, с девятнадцатого по шестнадцатый соединены с четырьмя входами первого, второго, третьего и четвертого элементов ИЛИ соответственно, выходы дешифратора с первого по четвертый, седьмой, восьмой, с одиннадцатого по четырнадцатый и выходы первого, второго и третьего элементов ИЛИ соединены с входами пятого элемента ИЛИ, а его выход соединен с входом прерывания

ЭВМ, выходы дешифратора нулевой, пятый, шестой,девятый, десятый,пятнадцатый соединены с входами шестого элемента ИЛИ, выходы дешифратора с первого по пятнадцатый и выходы второго, третьего и четвертого элементвв ИЛИ соединены с входами седьмого элемента ИЛИ, выходы дешифратора с первого по третий, седьмой, одиннадцатый соединены с входами восьмого элемента ИЛИ, выходы дешифратора четвертый, восьмЬй, с двенадцатого по четырнадцатый соединены с входами девятого элемента ИЛИ, выходы дешифратора первый, четвертый, пятый и выход третьего элемента ИЛИ соединенены с входами десятого элемента ИЛИ выходы дешифратора нулевой,шестой девятый, пятнадцатый соединены с входами одиннадцатого элемента ИЛИ, выходы дешифратора второй, восьмой, десятый и выход второго элемента ИЛИ соединены с входами двенадцатого элемента ИЛИ, выходы дешифратора нулевой, пятый, шестой, девятый, пятнадца тый соединены с входами тринадцатого элемента ИЛИ, выходы дешифратора с пятого по седьмой, с девятого по одиннадцатый, с тринадцатого По пятнадцатый соединены с входами четырнадцатого элемента ИЛИ,выходы логических элементов ИЛИ первого, четвертого, с пятого по четырнадцатый и нулевой выход дешифратора подключены к выходным.шинам устройства ij .

Недостатком известного устройства является низкая точность самоконтроля, вследствие наличия неопределенности в определении места неисправности .

Цель изобретения - повышение точности самоконтроля.

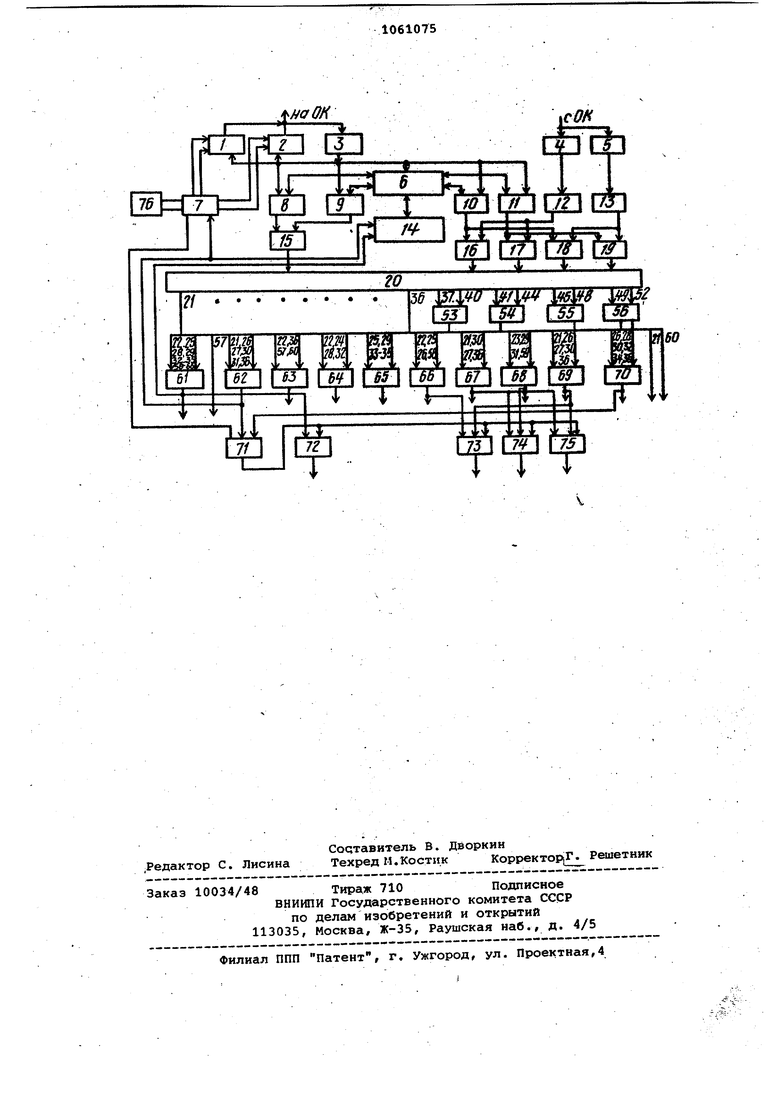

Поставленная цель достигается тем,, что в устройство для автоматического контроля электронных систем. Содержащее ЭВМ, соединенную через контроллер с управляющим входом первого коммутатора, выходы первого коммутатора соединены с клеммами для подключения входов объекта контроля, входы первого шифратора соединены с выходами первого коммутатора, а выход - с магистральными шинами контроллера входы второго и третьего Шифраторов соединены между собой и с клеммами для подключения выходов объекта контроля, а выходы соединены соответственно с входами пятого и шестого регистров памяти, входы первого, второго, третьего и четвертого, регистров памяти соединены с магистральными и соответствующими адресными шинами контроллера, выходы первого и второго регистров памяти соединены соответственно с первым вторым входами первого логического элемента эквивалентности, в.ыход третьего регистра памяти соединен с nepBboviH входами второго и четвертог элементов эквивалентности, выход. четвертого регистра памяти соединен с первыми входами третьего и пя того элементов экв.ивалентности,входы пятого и шестого регистров памяти соединены с выходами второго и третьего шифраторов соответственно, а выход пятого регистра памяти соединен с вторыми входами второго и третьего элементов эквивалентности, выход шестого регистра памяти соеди нен с вторыми входами четвертого И пятого элементов эквивалентности, выход пятого элемента эквивалентности соединен с входом-младшего разряда дешифратора, а выходы четвертого, третьего, второго и первог .элементов эквивалентности соответственно с входами последующих разрядов дешифратора, выходы пятиразрядного дешифратора с тридцать первого по двадцать восьмой, с двадцать седьмого по двадцать четвертый с двадцать третьего по двадцатый, с девятнадцатого по шестнадцатый со динены с четырьмя входами первого, второго, третьего и четвертого элементов ИЛИ соответственно, выходы дешифратора с первого по четвертый, седьмой, восьмой, с одиннадцатого по четырнадцатый и выходы первого, второго и третьего элементов ИЛИ соединены с входами пятого элемента ИЛИ, а его выход соединен с входом прерывания ЭВМ, выходы дешифратора нулевой, пятый, шестой, девятый, десятый, пятнадцатый соединены с входами шестого элемента ИЛИ,выходы дешифратора с первого по пятнадцатый и выходы второго, третьего и четвертого элементов ИЛИ соединены с входами седьмого элемента ИЛИ, выходы дешифратора с первого по тре тий, седьмой, одиннадцатой соединен с входами, восьмого элемента ИЛИ,выходы дешифратора четвертый, восьмой с двенадцатого по четырнадцатый сое динены с входами девятого элемента ИЛИ, выходы дешифратора первый, четвертый, пятый и выход третьего элемента ИЛИ соединены с входами де сятого элемента ИЛИ, выходы дешифра тора нулевой, шестой, девятый, пятнадцатый соединены с входами одинна цатого элемента ИЛИ, выходы дешифра тора второй, восьмой, десятый и выход второго элемента ИЛИ соединены с входами двенадцатого элемента ИЛИ выходы дешифратора нулевой,пятый, шестой, девятый, пятнадцатыми соедин ны с входами тринадцатого элемента ИЛИ, вьлходы дешифратора с пятого по седьмой, с девятого по одиннадца тый, с тринадцатого по пятнадцатый соединены с входами четырнадцатого элемента ИЛИ, выходы логических эле ментов ИДИ первого, четвертого, с пятого по четырнадцатый и нулевой выход дешифратора подключены к выходным шинам устройства, введены первый, второй, третий, четвертый и пятый элементы И, второй коммутатор и распределитель, причем выход и первый вход второго коммутатора соединены соответственно с выходом и первым входом первого коммутатора,вторые входы первого и второго кока утаторов Соединены с.соответствующими первыми и вторыми выходам распределителя, первый вход которого соединен с выходом источника стимулирующих сигналов, второй вход - с выходом шестого элемента ИЛИ, с вторым входом прерывани-я ЭВМ и с первым входом первого элемента И, контроль- ный выход распределителя соединен с вторым входом первого элемента И, третий вход которого соединен с выходом четырнадцатого элемента ИЛИ, выход которого соединен с первыми входами второго, третьего, четвертого и пятого элементов И, второй вход второго элемента И соединен с выходом Пятого элемента- ИЛИ, второй вход третьего элемента И соединен с выходом десятого элемента ИЛИ, третий вход третьего элемента И соединен с выходом тринадцатого элемента ИЛИ и с третьим входом пятого элемента И, йторой вход которого соединен с выходом одиннадцатого элемента ИЛИ и с вторым входом четвертого элемента И, третий вход которого соединен с выходом двенадцатого элемента ИЛИ, выходы второго, третьего, четвертого и пятого эле- : ментов И подклю ;ены к выходным шинам устройства. На чертеже представлена схема предлагаемого устройства. Устройство содержит первый 1 и второй 2 кЪммутаторы, первый 3, второй 4 и Третий 5 шифраторы,контроллер б, распределитель 7, регистры 8-13 памяти, ЭВМ 14, логические элементы 15-19 эквивалентностигДе- . шифратор 20 с выходами 21-52, логические элементы 53-56 ИЛИ с выходами 57-60, логические элементы 61-70 ИЛИ, логические элементы 71-75, источник 76 стимулирующих сигналов. Входами устройства явлжотся входы шифраторов 4 и 5. Выходами устройства являются выходы коммутаторов 1 и 2 и выходы логических элементов 53,56,61-70 ИЛИ, выход 21 дешифратора 20 и выходы логических элементов 72-75, подключенные к выходным шинам устройства. Устройство работает следующим образом. ЭВМ 14 содержит в своей памяти последовательность выдачи воздействий HZk объект контроля и его логическую модель, позволяющую формировать эталонную реакцию объекта контроля на любое воздействие из имеющегося перечня. ЭВМ 14 через контроллер 6 выдает код стимулирующего воздействия на коммутаторы 1 и 2 и регистр 8. Стимулирующее воздействие с выхода коммутатора 1 поступает на объект контроля и на вход шифратора 3, с выхода которого контрольный код поступает на вход регистра 9 и через контроллер б - на ЭВМ 14.

После выдачи воздействия на объект контроля ЭВМ 14 формирует кодовое сообщение, соответствующее эталонной реакции объекта контроля на запланированное воздействие, и вьздает его через контроллер б на регистр 10. Если коды ввданного на объект контроля (юступившего от шифратора 3) и запланированного воздействий ие совпадают, ЭВМ 14 выдает через контроллер 6 на регистр 11 дополнительное кодовое сообщение, соответствующее эталонной реакции объекта контроля на код воздействия, зарегистрированный шифратором 3.

Реакция объекта контроля на выгданное воздействие воспринимается шифраторами 4 и 5, с выходов которых кодовые сообщения поступают на входы регистров 12 и 13 соответственно. С выходов регистров 12 и 13 коды поступают на входы элементов 16-19 эквивалентности соответственно. На вторые входы элементов

16и 18 эквивалентности поступают коды с регистра 10, а элементов

17и 19 эквивалентности - с регистра 11. Совпадение кодов на входах элемента 15 эквивалентности свидетельствует о выдаче на объект контроля запланированного воздействия, на входах элементов 16 и 18 эквивалентности - о реакции объекта контроля на запланированное воздействие, на входах элементов 17 и 19 эквивалентности - о реакции объекта контроля на воздействие, код которого зарегистрирован шифратором 3. Комбинация состояний выходов логических элементов 15-19 эквивалентно ти позволяет сделать заключение о состоянии , Не норма, Неопределенность каждого элемента устройства и объекта контроля. Выxopta элементов : 15-19 эквивалентности поступгиот на дешифратор 20, выходы которого собрайы на логические элементы 3-56, 61-70 ИЛИ по принципу аналогичности заключений о

состоянии соответствующих элементов устройства и объекта контроля

.следующим образом: элемент 53 ИЛИ объект контроля Не норма, элемент 56 ИЛИ - устройство контрол Норма, элемент 61 ИДИ - объект 5 контроля Норма, элемент 62 ИЛИ объект контроля, коммутатор 1, шифратор 3 в состоянии Неопределенность, элемент 63 ИЛИ - устройство контроля Не норма, элемент

Л 64 или -.коммутатор 1 Не норма, элемент 65 или - шифратор 3 Не норма, элемент б6 ИЛИ - шифратор 4 Не норма,элемент 67 ИЛИ - шифратор 4 в состоянии Неопределенность, элемент 68 ИЛИ - шифратор 5

Не норма, элемент 69 ИЛИ - шифратор 5 в сйстоянии Неопределенность, элемент 70 ИЛИ - элементы 15-19 эквивалентности Не норма, выход 21 дешифратора 20 - эле0 менты 15-19 эквивалентности в состоянии Неопределенность.

Появление сигнала на выходе элемента 62 ИЛИ, соответствующего состоянию Неопределенность - объек5 та контроля, коммутатора 1 и шифратора 3, вызывает переключение источников стимулирующих сигналов с .помощью распределителя 7 с одного выхода на другой, а следовательно,

0 с входов коммутатора 1 на входы коммутатора 2. Одновременно этот сигнал поступает на вход прерывания ЭВМ для запуска нового цикла выдачи кодовых сообщений об эталонных реак5 циях объекта контроля. Комбинация состояний выходов элементов 61, 62, 66-70 ИЛИ по результатам выдачи воздействия на объект контроля с одного и другого коммутаторов позволяет

сделать заключение о местах неисправности: элемент 72 И - элементы 15-19 эквивалентности Не норма, элемент 73 И - элементы 15-19 эквива- . лентности Не норма, шифратор 5 Не норма, элемент 74 И - элемен5 ты 15-19 эквивалентности Не норма, шифратор 4 Не норма, элемент 75 И коммутатор 1, работающий в предыдущем цикле, Не норма.

При появлении сигнала с выхода

0 элемента ИЛИ 61 ЭВМ 14 получает уведомление через систему прерывания об успешном окончании цикла контроля и формирует выдачу следующих воздействий .

5 Введение дополнительного коммутатора 2, распределителя 7, логических элементов И 71-75, новых связей позволяет разрешить неоднозначность в определении места неисправ.ности по выходу элемента 62 ИЛИ,

обозначающему неопределенное состояние объекта контроля коммутатора, шифратора 3 и повысить таким образом точность самоконтроля.

наОН

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматического контроля электронных систем | 1981 |

|

SU980027A1 |

| Устройство автоматического контроля электронных систем | 1982 |

|

SU1129570A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1982 |

|

SU1053139A1 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

УСТРОЙСТВО АВТОМАТИЧЕСКОГО КОНТЮЛЯ ЭЛЕКТРОННЫХ СИСТЕМ по авт.св. I 980027 отличающееся тем, что, с целью повышения точности самоконтроля в устройство введены первый, второй,третий, четвертый и пятый элементы И, второй коммутатор и распределитель, причем выход и первый вход второго коммутатора соединены соответственно с ВЫХОДОМ и первым входом первого коммутатора, вторые входы первого и второго коммутаторов соединены с соответствующими первьми и вторыми выходами распределителя, первый вход которого соединен с выходом источника стимулирующих сигналов, второй вход - с выходом шестого элемента ИЛИ, с вторым входом прерывания ЭВМ и с первым входом, первого элемен та И, контрольный выход расп еделителя соединен с вторым входом первого элемента И,третий вход которого соединен с выходом четырнадцатого элемента ИЛИ, выход которого соединен с первыми входами второго, третьего, четвертого и пятого элементов И, второй вход второго элемента И соединен с выходам пятого элемента ИЛИ, второй вход третьего элемента И соединен с выходом ч есятого элемента ИЛИ, третий вход третьего элемента И соединен с выходом тринадцатого КЛ элемента ИЛИ и с третьим входом пятого элемента И. второй вход которого соединен с выходом одиннадцатого элемента ИЛИ и с вторым входом четвертого элемента И, третий вход которого срединен с выходом двенадцатого элемента ИЛИ, выходы второго, ь третьего, четвертого и пятого элементов И подк100чены к выходным ши нам устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство автоматического контроля электронных систем | 1981 |

|

SU980027A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-12-15—Публикация

1982-05-07—Подача