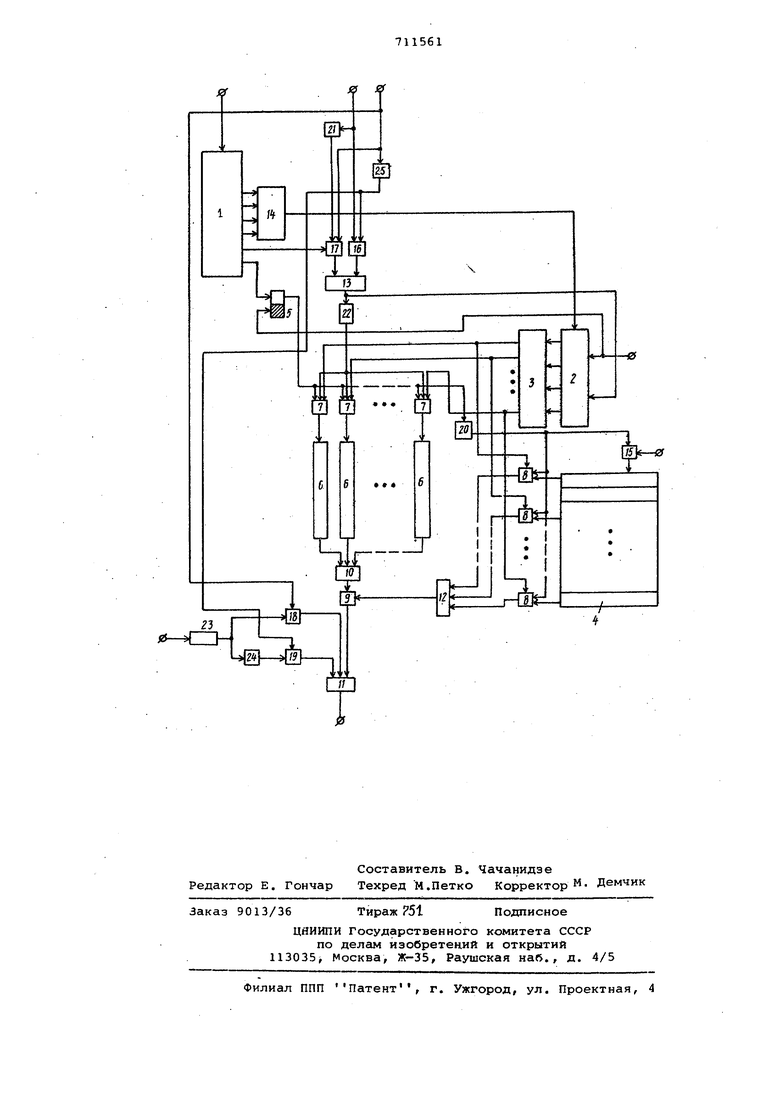

(54) УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ И ПОТЕНЦИРОВАНИЯ выходом элемента Ж, а также триггер нулевой вход которого соединен с шиной установки 2. Целью изобретения является расширение функциональных возможностей устройства путем логарифмирования и потенцирования дроичных чисел с плавающей запятой. Достигается это тем, что в устрой для логарифмирования и потенцирования, содержащее регистр сдвига и триггер, первые входы которых соединены с установочным входом устройства, распределитель, вход которого со единен с первым управлянляим входом устройства, первый выход распределит ля соединен с вторым входом триггера выход которого соединен с первыми вх дами элементов И первой группы и че рез первый элемент задержки - с первыми входами элементов И второй груп пы и первым входом первого элемента И, который тактирующий вход устройства соединен с входом блока регистров сдвига, выходы котового соединены с вторыми входами соответствующих элементов И второй группы, третьи входы которых и вторые входы элементов И первой группы соединены с соответствующими выходами дешифратора, входы которого соединены с выходами регистра сдвига, выходы элементов И первой группы через соответ ствующие узлы задания коэффициентов группы соединены с входами первого элемента ИЛИ, выход которого через последовательно соединенные сумматор и второй элемент ИЛИ соединен с выходом, устройства, выходы элементов И второй группы через третий элемент ИЛИ соединены с входом сумматора, второй управляющий вход устройства через последовательно соединенные элемент ЯЕ и второй элемент И соединен с первым входом четвертого элемента ИЛИ, введены пятый элемент ИЛИ три элемента И, три элемента задержки, причем, первый информационный вход устройства соединен с входом второго элемента И и через второй элемент задержки - с первым входом третьего элемента И, второй вход которого и первый вход четвертого элемента И соединены с в-торкпи управляющим входом устройства,.выход элемента НИ соединен с первым входом пятого элемента И, второй выход распредели геля соединен с третьим входом третьего элемента И, выход которого соединен через четвертый элемент ИЛИ с вторым входом регистра сдвига и входом третьего элемента задержки, выход которого соединен с третьими входами узлов задания коэффициентов группы, группа выходов распределите ля через пятый -элемент ИЛИ соединена с третьим входом регистра сдвига, второй информационный вход устройст |ва через четвертый элемент задержки соединен с вторым входом четвертого элемента И и входом пятого элемента задержки, выход которого соединен с вторым входом пятого элемента И, выход которого и выход четвертого элемента И соединены с соответствующими входами второго элемента ИЛИ. На чертеже приведена блок-схема устройства. Устройство содержит распределитель 1, регистр 2 сдвига, дешифратор 3, блок 4 регистров сдвига, триггер 5, группу узлов 6 задания коэффициентов, группу элементов И 7, группу элементов И 8, сумматор 9, элементы ИЛИ 10-14, элементы И 15-19, элементы 20-24 задержки, элемент НЕ 25. Функционирование устройства для логарифмирования и потенцирования двоичных чисел осуществляется следующим образом. В исходном состоянии регистр 2 и триггер 5 установлены в нулевое состояние. В случае логарифмирования на второй управляющий вход устройства постоянно подается едини:ца, в результате чего, в функционировании устройства принимают участие элементы И 17, 18 и одна часть узлов б группы. В случае потенцирования на второй управляющий вход устройства постоянно подается нуль, в результате чего оказываются включенными элементы И 16, 19 и другая часть узлов 7 группы. Вначале рассмотрим случай логарифмирования двоичных чисел. На первом этапе на первый управляющий вход устройства поступает единица, которая распределяется, на выходах распределителя 1 в течение семнадцати тактов. Начиная с первого по шест.надцатый такты, на первый инЛормационный вход устройства поступает мантисса младшими разрядами вперед. Мантисса, задержанная на один такт элементом 21, через элементы И 17 и И.ЛИ 13 поступает на вход элемента 22; при этом на семнадцатом такте нулем с второго выхода распределителя 1 осуществляется гашение старшей единицы мантиссы. С тринадцатого по шестнадцатый такты с выхода элемен-та или 14 выдается единигха, которая разрешает записать в регистр 2 с элемента ИЛИ 13 с двенадцатого по пятнадцатый разряды мантиссы. В результате этого на одном из выходов дешифратора 3 образуется единица, которая.подается на один из элементов И 7 и a .один из элементов И 8. На семнадцатом такте сигналов с первого выхода распределителя 1 триггер 5 устанавливается в единичное состояние. Единица триггера 5 разре1чает прохождение информации, задержанной на шестнадцать тактов элементом 22, через выбранный элемент И 7 на вход соот,ветствуюцего узла 6. Этот же сигнал с триггера 5 через элемент 20, время задержки которого равняется времени работы узлов б/ подается на эле мент И 15, разрешая тем самьтм проход тактовых импульсов на регистры блока 4. Через выбранный элемент И 8 и элемент ИЛИ 12 информация с соответствующего регистра блока 4 подается на вход сумглатора 9, на другой вход которого через элемент ИЛИ 10 подается информация с выбранного узла б На выходе сумматора 9 образуется ман тисса логарифма двоичного числа по следующей системе уравнений: у 1,01100110010х + 0,00000000001 у 1,01010001101Х + 0,000000010111 у 1,001И111011Х + 0,000000111011 vl 1,00101111000х + 0,00000110,1100 у 1,00100000010Х + 0,000010100111 у l,00010010111X.-f 0,000011101001 У 1,00000110101Х + 0,000100110011 yg Д + 0,00000100100Х+ 0,00010011100 Уц Х+0,00001110110Х-(- 0,00001110011 У-10 X-+0,OOOilOOOOlOX+ 0,00001010010 У Х+0,00100001000Х+ 0,00000111000 ,00101001001х + 0,00000100011 у Х+0,00110000101х + 0,00000010100 4 0/00110111110х -f 0,00000001010 у X-fo,00111110010x + 0,00000000011 , X+0,01000100011X + 0,00000000000 Первые члены уравнение у -у-, и первые два члена уравнений фор мируются в узлах б, а вторые члены уравнений у, - у и третьи члены урав нений (, записаны в регистрах бло ка 4. При этом каждому узлу 6 соответствует один из регистров блока 4. С семнадцатого по двадцатый такты на второй информационный вход младшими разрядами вперед подается порядок, а на двадцать первом такте его знак. Эта информация на элементе 23 задерживается на 27 тактов и через элемент И 18 подается на вход элемента ИЛИ 11 в виде характеристи,ки погарифма. Начиная с двадцать восьмого такта с выхода устройства снимается сначала мантисса логарифма младшими разрядами вперед, затем характеристика логарифма также младшими разрядами вперед, а на последнем сорок восьмом такте - знак характеристики. При потенцировании запускается распределитель 1 и выдается единица на его выходе. Начиная с первого по шестнадцатый такты, на первый информационный вход поступает мантисса логарифма младшими разрядами впередF которая через элеменТЫ И 16 и ИЛИ 13 поступает на вход элемента 22. С тринадцатого по шестнадцатый такты на выходе элемента ИЛИ 14 образуется единица, которая разрешает записать в регистр 2 с выхода элемента ИЛИ 13 с тринадцатого по шестнадцатый разряды мантиссы логарифмы. Вследствие этого на одном -из выходов дешифратора 3 образуется единица, которая подается на соответствующие элементы И 7 и И 8. На семнадцатом такте по сигналу с первого выхода распределителя 1 триггер 5 устанавливается в единицу, которая разрешает прохождение мантиссы логарифма, задержанного на шестнадцать тактов элементом 22, через выбранный элемент И 7 на соответствующий узел 6. Единичный сигнал с триггера 5 через элемент 20 открывает элемент И 15, разрешая тем самым поступление тактовых импульсов на регистры блока 4. Через выбранный элемент И 8 и элемент ИЛИ 12 информация с соответствующего регистра блока 4 подается на один из входов сумматора, на другой вход которого через элемент ИЛИ 10 подается информация с выхода выбранного узла б. На выходе сумматора 9 образуется мантисса двоичного числа по следующей системе уравнений: Х У+0,01001010110У +0,101101010011 Х, У+0,01000010101У +0,101111001101 X.j У+0,ООИ1010010У +0,110001000010 Х У + 0,00110001100У +0,110010110100 Xj- У + 0,00101000011У +0,110100100001 Х(, У + 0,00011110111У +0,110110001010 Х У+0,00010100111У +0,110111101110 Xg У+0,00001010011У +0,111001001100 XQ У+0,0111010011111 Хю 1,00001011И1У + 0,111000110101 Х 1,00010111101У + 0,110110111111 X,, 1,00100100001У + 0,110100110101 Х 1,00110001000У + 0,110010011011 Х 1,00111110100У + 0,101111101011 1,01001100101У + 0,101100100101 Xi6 1,01011011010У + 0,101001001010 с семнадцатого по двадцатый такты на второй информационный вход младшими разрядами вперед подаётся характеристика, а на двадцать первом такте - ее знйк. Эта информация на элементе 23 задерживается на двадцать семь тактов и через элемент 24 и элемент И 19 подается на элемент ИЛИ 11 в виде порядка двоичного числа. Начиная с двадцать девятого такта, с выхода устройства снимается мантисса и порядок мла пиими разрядами вперед, а на последнем сорок девятом такте - знак порядка. В предлагаемом устройстве достигается расширение его функциональных возможностей путем обработки последовательных двоичных кодов чисел с плавающей запятой. Это приводит к резкому увеличению диапазона двоичных чисел, над которыми оперирует устройство для логарифмирования и потенцирования . По предла-гаемому изобретению разработан технический проект, утвержденный Минприбором СССР. Согласно плану Минприбора СССР предложенное устройство логарифмирования и потенцирования двоичных чисел впервые будет внедсено на предприятии НПО ЭЛВА в 1979-79 гг. в составе микро-ЭВМ и п рестраиваемой управляющей логической мацшны. Экономический эффект, который может быть получен народным хозяйством в результате использования изобретения при серийном производстве указанных ЭВМ в год в количестве 100 штук каждой составит около 215 тыс. руб. в год. Формула изобретения Устройство для логарифмирования и потенцирования, содержащее регистр сдвига и триггер, первые входы которых соединены с установочным входом устройства, распределитель, вход которого соединен с первым управляющим входом устройства, первый выход распределителя соединен с вторым входом триггера, выход которого соединен с Первыми входами элементов И первой группы и,через первый элемент задерж ки - с первьпии входами элементов И второй группы и первым входом первого элемента И, через который тактиру ющий вход устройства соединен с вхо- дом блока регистров сдвига, выходы которого соединены с вторыми входами соответствующих элементов И второй группы, третьи входы которых и вторые входы элементов И первой группы соединены с соответствующими выходами дешифратора, входы которого соеди нены с выходами регистра сдвига, вхо ды элементов И первой группы через соответатвующие узлы задания коэффициентов группы соединены с входами .первого элемента ИЛИ, выход которого через последовательно срединенные сумматор и второй элемент ИЛИ соеди.иен с вьзходом устройства, выходы эле ментов И :1§торой группы через третий элемент ИЛИ соединены с входом сумматора, второй управляющий вход устройства через последовательно соединенные элемент НЕ и второй элемент И соединен с первЕЛМ входом четвертого элемента ИЛИ, отлич ающее с я тем, что, с целью расширения функциональных возможностей путем логарифмирования и потенцирования двоичных чисел с плавающей запятой, в него введены пятый элемент ИЛИ, три элемента И, три элемента задержки, причем первый информационный вход устройства соединен с входом второго элемента И и через второй элемент задержки - с первым входом третьего элемента И, второй вход которого и первый вход четвертого элемента И соединены с вторым управляющим входом устройства, выход элемента НЕ соединен с первым входом пятого элемента И, второй выход распределителя соединен с третьим входом третьего элемента И, выход которого соединен через четвертый элемент ИЛИ с вторым входом регистра сдвига и входом третьего элемента задержки, выход которого соединен с третьими входами узлов задания коэффициентов группы, группа выходов распределителя через пятый элемент ИЛИ соединена с третьим входом регистра сдвига, второй информационный вход устройства через четвертый элемент задержки соединен с вторым входом четвертого элемента И и входом пятого элеме чта задержки, выход которого соединен с вторым входом пятого элемента И, выход которого и выход, четвертого элемента И соединены с соответствующими входами второго элемента ИЛИ, .. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР, № 446054, кл. G 06 F 5/02, 1973. 2„ Авторское свидетельство СССР, № 523408, кл. G 06 F 5/02, 1974 (прототип) .. SS 0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для потенцирования | 1978 |

|

SU711562A1 |

| Устройство для логарифмирования | 1978 |

|

SU711560A1 |

| Устройство для преобразования двоичных чисел | 1973 |

|

SU446054A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Устройство для вычисления показательно-степенных функций | 1980 |

|

SU928350A1 |

| Логарифмирующее устройство | 1976 |

|

SU634272A1 |

| Устройство для вычисления функций | 1985 |

|

SU1287150A1 |

| Устройство для логарифмирования | 1982 |

|

SU1030800A1 |

Авторы

Даты

1980-01-25—Публикация

1978-08-08—Подача