lif ю ел

Од N9

Изобретение относится к радиотехнике и может быть использовано для подавления помех, например, при измеении малых сигналов на фоне значительно превосходящих их по уровню промышленных помех.

Цель изобретения - упрощение синхонного режекторного фильтра за счет уменьшения аппаратурных затрат. Q

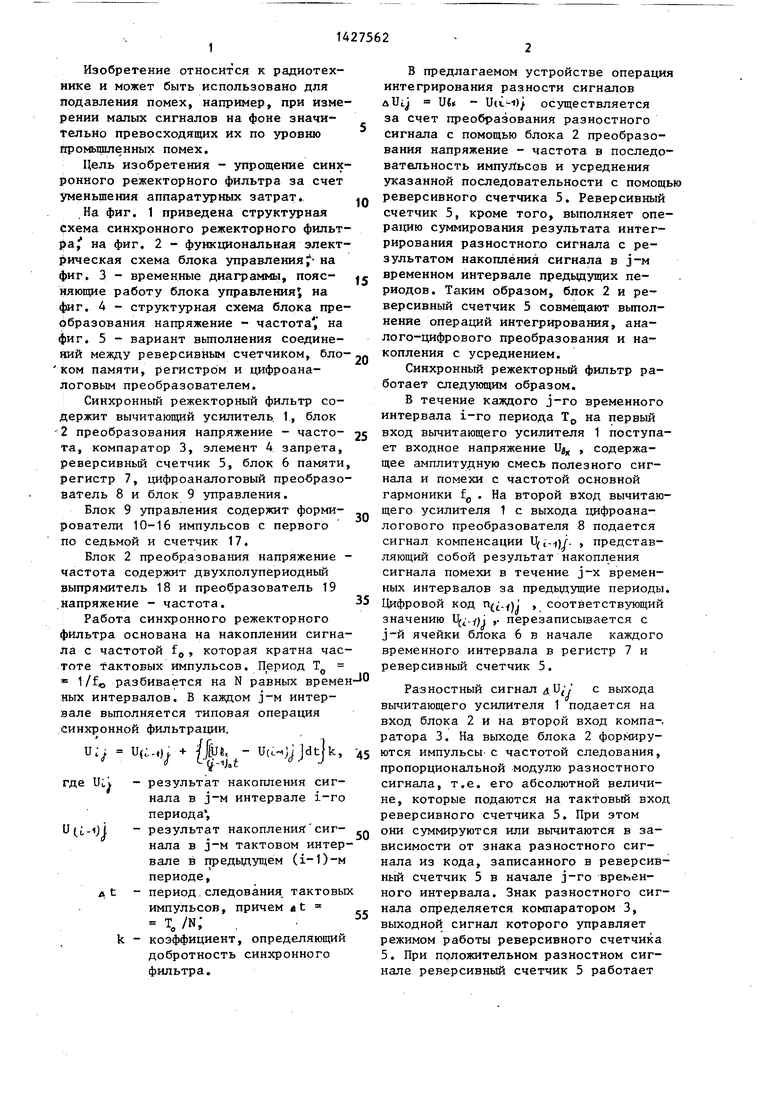

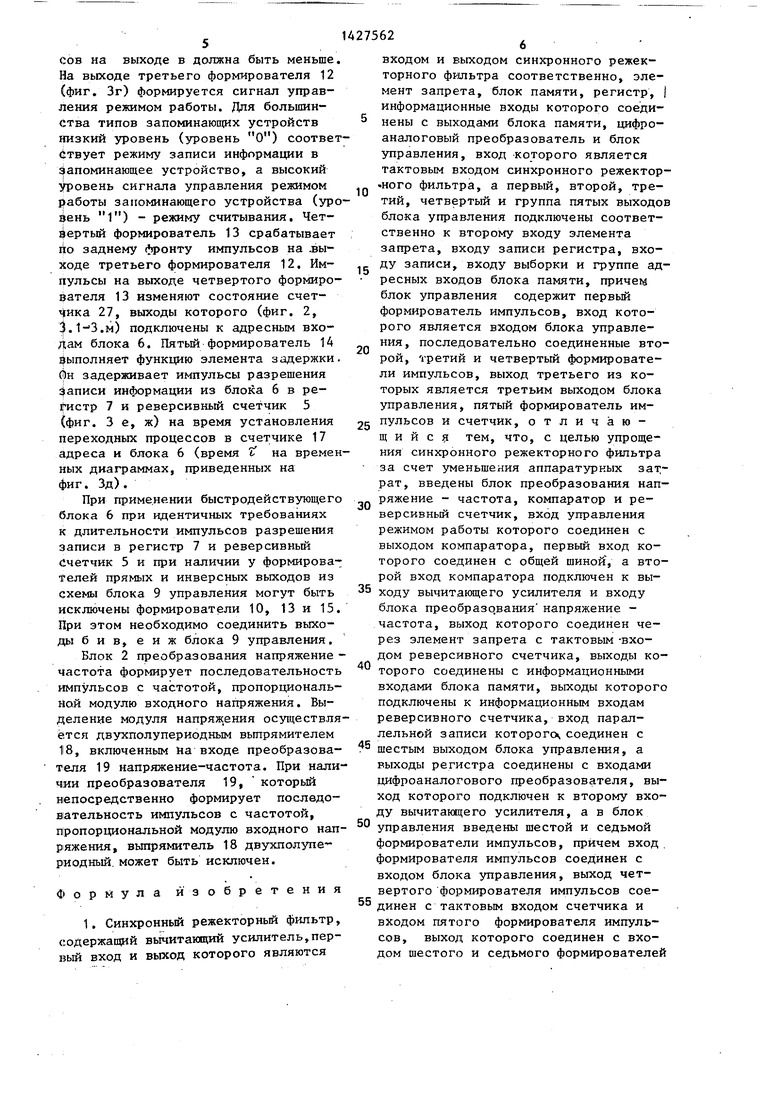

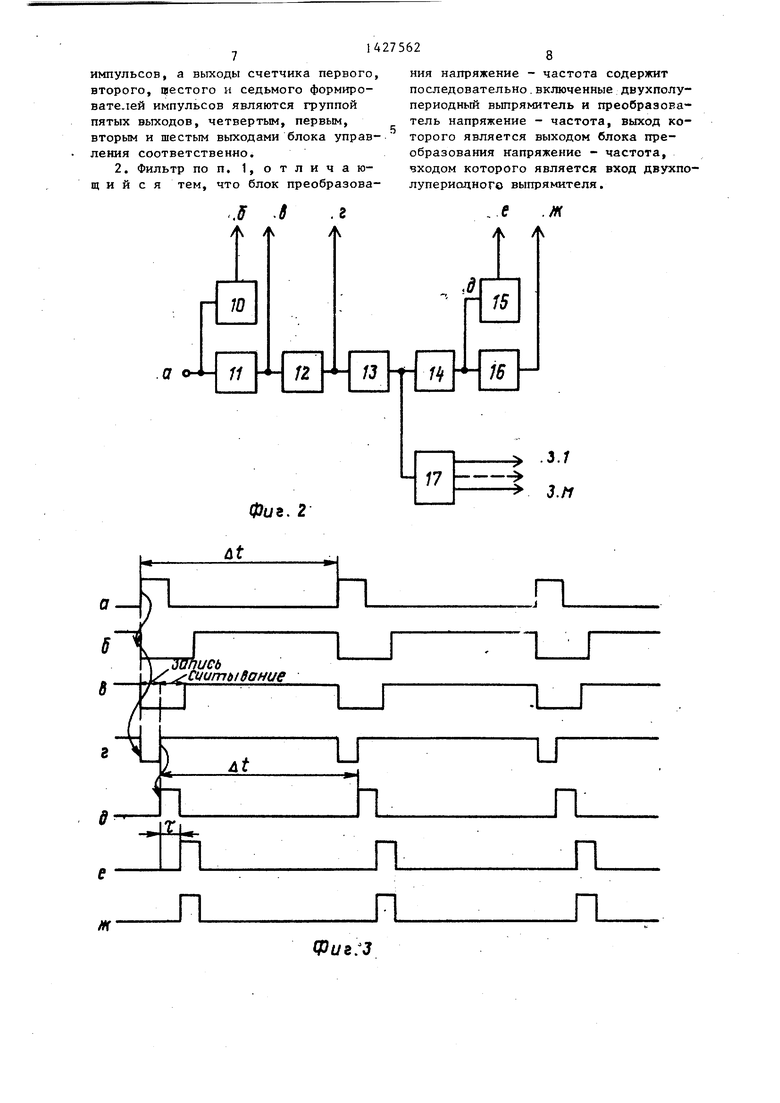

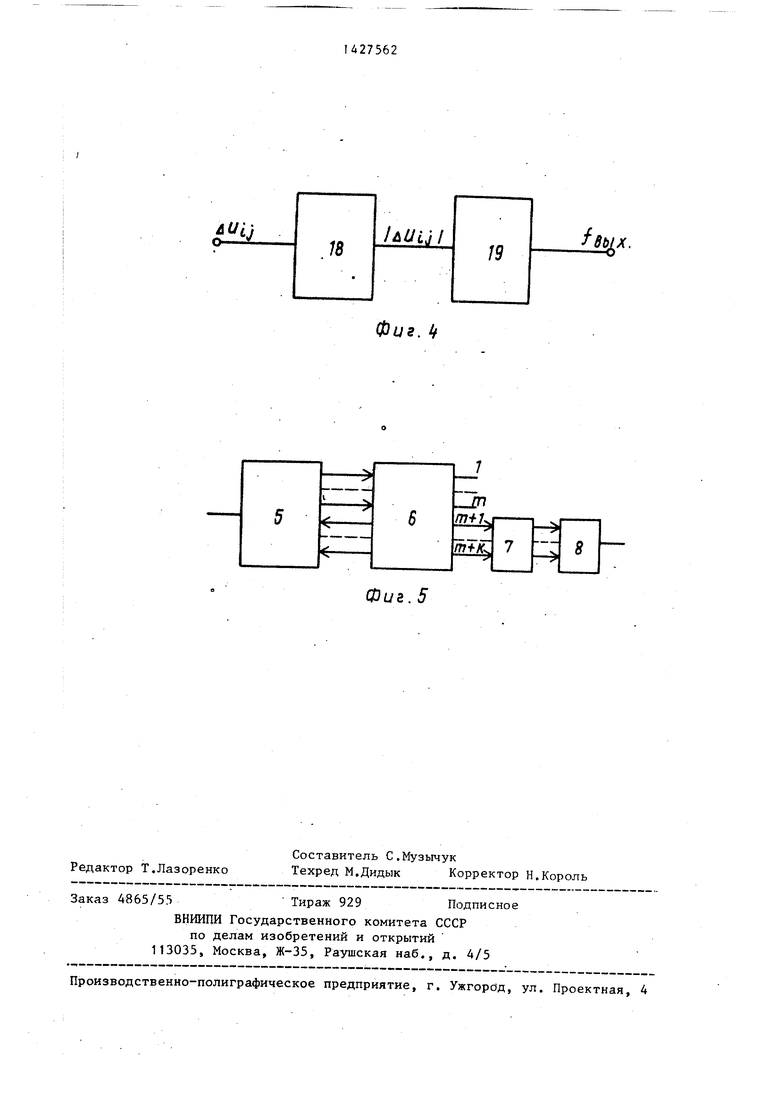

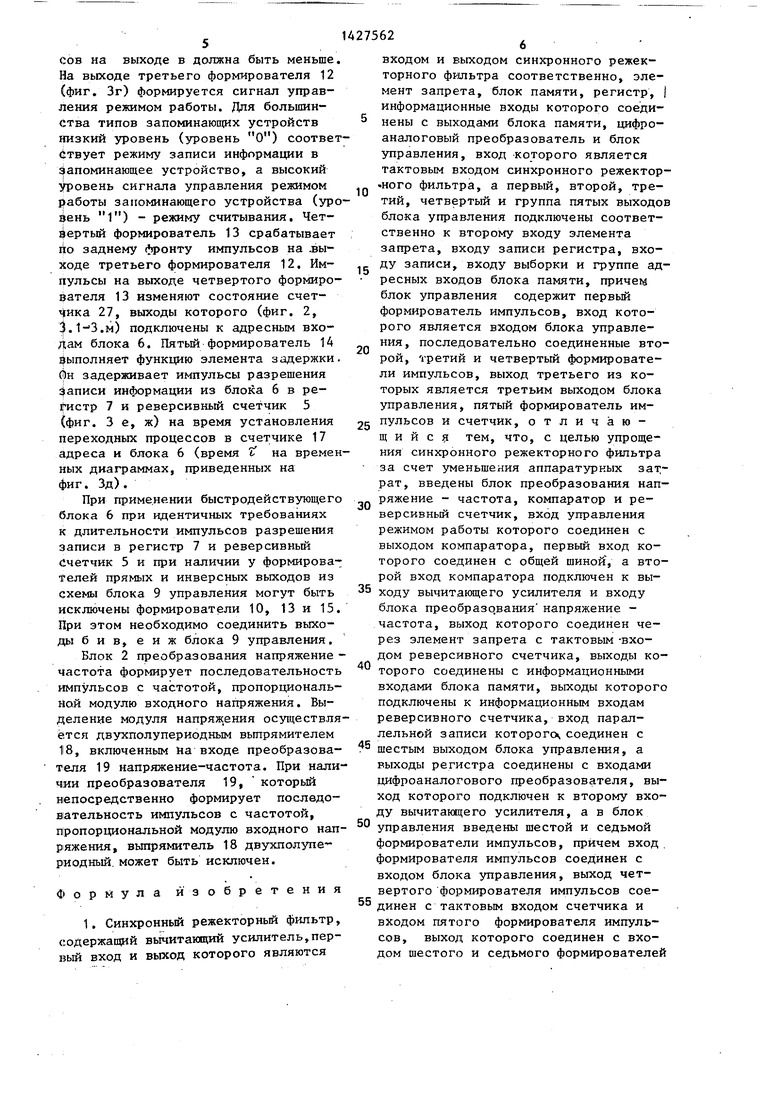

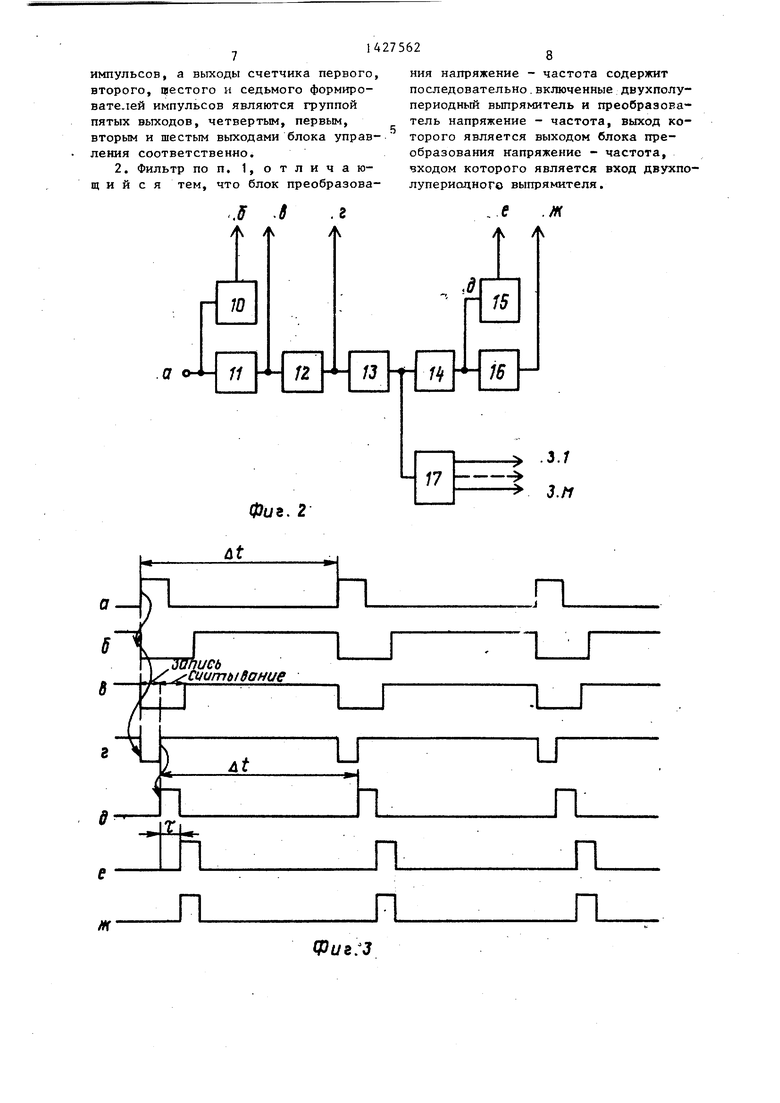

На фиг. 1 приведена структурная схема синхронного режекторного фильта на фиг. 2 - функциональная электическая схема блока управления - на иг. 3 - временные диаграммы, пояс- |j ияющие работу блока управления на иг. 4 - структурная схема блока пребразования напряжение - частота , на иг. 5 - вариант вьтолнения соединений между реверсивным счетчиком, бло- -- ком памяти, регистром и цифроана- логовым преобразователем.

Синхронный режекторный фильтр содержит вычитающий усилитель. 1, блок 2 преобразования напряжение - часто- 25 та, компаратор 3, элемент 4 запрета, реверсивный счетчик 5, блок 6 памяти, регистр 7, цифр о аналоговый прео-бразо- ватель 8 и блок 9 управления.

Блок 9 управления содержит форми- рователи 10-16 импульсов с первого по седьмой и счетчик 17.

Блок 2 преобразования напряжение - частота содержит двухполупериодный выпрямитель 18 и преобразователь 19 напряжение - частота.35

Работа синхронного режекторного фильтра основана на накоплении сигнала с частотой fj, , которая кратна частоте тактовых импульсов. Период Т„

W |п

« 1/f.o разбивается на N равных времен- ных интервалов. В каждом j-м интервале вьшолняется типовая операция синхронной фильтрации.

и: Щ:.,) + {|у«. - U(c jjjdtjk, 45 где и

- результат накопления сигнала в J-M интервале i-ro периода ,

U(L-iH - результат накопления сиг- ,- нала в J-M тактовом интервале в предыдущем (1-1)-м периоде.

At - период. следования, тактовых импульсов, причем «t

Т, /N; ,

k - коэффициент, определяющий добротность синхронного фильтра.

55

Q

j -

5

5

п

5

-

5

В предлагаемом устройстве операция интегрирования разности сигналов aUi.j Ut - U(ii.n)i осуществляется за счет П1)еобразования разностного сигнала с помощью блока 2 преобразования напряжение - частота в последовательность импульсов и усреднения указанной последовательности с помощью реверсивного счетчика 5. Реверсивный счетчик 5, кроме того, выполняет операцию суммирования результата интегрирования разностного сигнала с результатом накопления сигнала в J-M временном интервале предьщущих периодов. Таким образом, блок 2 и реверсивный счетчик 5 совмещают вьшол- нение операций интегрирования, аналого-цифрового преобразования и накопления с усреднением.

Синхронный режекторный фильтр работает следующим образом.

В течение каждого j-ro временного интервала i-ro периода Т на первый вход вычитающего усилителя 1 поступает входное напряжение U , содержащее амплитудную смесь полезного сигнала и помехи с частотой основной гармоники fp . На второй вход вычитающего усилителя 1 с выхода цифроана- логового преобразователя 8 подается сигнал компенсации . , представляющий собой результат накопления сигнала помехи в течение j-x временных интервалов за предьщущие периоды. Цифровой код П(.у)| , соответствующий значению %-т перезаписывается с j-й ячейки блока 6 в начале каясдого временного интервала в регистр 7 и реверсивный счетчик 5.

Разностный сигнал с выхода вычитающего усилителя 1 подается на вход блока 2 и на второй вход компа-, ратора 3. На выходе блока 2 формируются импульсы с частотой следования, пропорциональной модулю разностного сигнала, т.е. его абсолютной величине, которые подаются на тактовый вход реверсивного счетчика 5. При этом они суммируются или вычитаются в зависимости от знака разностного сигнала из кода, записанного в реверсивный счетчик 5 в начале j-ro временного интервала. Знак разностного сигнала определяется компаратором 3, выходной сигнал которого управляет режимом работы реверсивного счетчика 5. При положительном разностном сигнале реверсивный счетчик 5 работает

в режиме суммирования, а при отрицательном - в режиме вычитания. В конце j-ro временного-интервала в реверсивном счетчике 5 фиксируется число

Hi./

+ К

+ пну

nii-ib + а ntj n(i.- J + пнч atUi n{i-i)j +

-t-Uc.J

fo-N

где и nil - число, соответствующее накопленному значению разностного сигнала в течение j-ro временного интервала i-ro периодаJ пиЧ коэффициент преобразования бло ка 2, Ut,. - среднее значение разностного сигнала в течение j-ro временного интервала i-ro периода.

Полученное число n-j в начале ( + 1)-го временного интервала записывается в j-ю ячейку блока 6. Адрес j-й ячейки, а также сигнал выборки и управления записью-считыванием блока 6 формируются блоком 9 управления.

Для исключения возможности изменения состояния реверсивного счетчика 5 во время записи его выходного кода в блок 6, на второй вход элемента А запрета с выхода первого формирователя 11 блока 9 управления подается сигнал запрета, который запрещает прохождение импульсов на тактовый вход реверсивного счетчика 5 на время записи. После записи числа п.- с (J + 1)-й ячейки блока 6 считывается и записывается в регистр 7 и реверсивный счетчик 5 число tt-)(j-) 001 ветствующее .:сигналу, накопленному в течение (j + 1)-х временных интервалов предыдущих периодов. Далее процессы повторяются.

Если во входном сигнале синхронного режекторного фильтра имеются помехи, частота которых равна или кратна частоте F, , то в ячейках блока 6 накопятся усредненные дискретные значения помехи. Это означает, что ко второму входу вычитакщего усилителя 1 приложен сигнал, который по форме и фазе соответствует входной помехе. При этом происходит взаимная компенсация этих сигналов.

Для получения высокой добротности режекторного фильтра разрядность реверсивного счетчика 5 и блока 6 вы- брфается большей, чем разрядность резистора 7 и цифроаналогового преобразователя 8, причем входы регистра 7 подключаются к старшим разрядам выходов блока 6 (фиг, 5). Как слеДУ т из фиг. 5, к входам регистра 7 подключается К старших разрядов блока 6. Количество младших разрядов определяет добротность синхронного режекторного фильтра, которая опре-

деляется по формуле

jrNfo

(2 - 1)

R

пнч

и с

к

4KV

Uo

2025где Up - максимальное напряжение на

выходе цифроаналогового преобразователя 8, соответствующее максимальному входному коду. Если, например, N 256, f 50 Гц,

m 8, k

10, К„„ч 10 Гц/В, и,

40

10 В, то О 1050. Указанные параметры элементов синхронного режекторного фильтра могут быть легко 30 достигнуты.

Как следует из описания принципа работы синхронного режекторного фильтра на выходе цифроаналогового преобразователя 8 выделяется сигнал помехи с частотой f(; . Следовательно, выход ци1,фоаналогового преобразователя 8 может ис-1ользоваться в качестве избирательного выхода предлагаемого устройства.

Блок 9 управления работает следую- щим образом.

Тактовые импульсы (фиг. За), час- - тота которых определяет частоту ре- жекции синхронного режекторного фильт-

45 ра, подается на входы первого 10 и второго 11 формирователей. На выводе первого формирователя 1.0 (фиг. Зб) формируется импульс выборки блока 6, а на выходе второго формирователя 1

50 (фиг. Зв) - сигнал запрета, который подается на первый вход элемента 4 запрета. В течение выборки блока 6 запрещается поступление счетных импульсов на тактовый вход реверсивно55 ° счетчика 5, что исключает ошибки при считывании информации из него в - блок 6. Длительность импульсов на выходе б,определяется временными пара-. . метрами блока 6, длительность импульCOB на выходе в должна быть меньше. На выходе третьего формирователя 12 (фиг. Зг) формируется сигнал управления режимом работы. Для большинства типов запоминающих устройств Низкий уровень (уровень О) соответ- бтвует режиму записи информации в запоминающее устройство, а высокий уровень сигнала управления режимом работы запоминающего устройства (уро- йень 1) - режиму считывания. Четвертый формирователь 13 срабатывает lio заднему фронту импульсов на эы- ходе третьего формирователя 12. Импульсы на выходе четвертого формирователя 13 изменяют состояние счет- цкка 27, выходы которого (фиг. 2, 3.1-3.м) подключены к адресным входам блока 6. Пятый формирователь 14 выполняет функцию элемента задержки. ())н задерживает импульсы разрешения : аписи информации из блойа 6 в регистр 7 и реверсивный счетчик 5 (фиг. 3 е, ж) на время установления переходных процессов в счетчике 17 адреса и блока 6 (время t на временных диаграммах, приведенных на фиг. Зд).

При применении быстродействующего блока 6 при идентичных требованиях к длительности импульсов разрешения записи в регистр 7 и реверсивный Счетчик 5 и при наличии у формирователей прямых и инверсных выходов из схемы блока 9 управления могут быть исключены формирователи 10, 13 и 15. При этом необходимо соединить выходы бив, еиж блока 9 управления.

Блок 2 преобразования напряжение - частота формирует последовательность импульсов с частотой, пропорциональной модулю входного напряжения. Выделение модуля напряж,ения осугцествля- ётся двухполупериодным вьшрямителем

10

20

входом и Е1ЫХОДОМ синхронного режек торного фкшьтра соответственно, эл мент запрета, блок памяти, регистр информационные Входы которого соед нены с выходами блока памяти, цифр аналоговый преобразователь и блок управления, вход которого является тактовым входом синхронного режект «ного фильтра, а первый, второй, тр тий, четвертый и группа пятых выхо блока управления подключены соотве ственно к второму входу элемента запрета, входу записи регистра, вх

„ ду записи, входу выборки и группе ресных входов блока памяти, причем блок управления содержит первьй формирователь импульсов, вход кото рого является входом блока управления, последовательно соединенные вт рой, третий и четвертый формировате ли импульсов, выход третьего из которых является третьим выходом блок управления, пятый формирователь импульсов и счетчик, отличающий с 9 тем, что, с целью упроще ния синхронного режекторного фильтр за счет уменьшения аппаратурных за рат, введены блок преобразования на ряжение - частота, компаратор и реверсивный счетчик, вход управления режимом работы которого соединен с выходом компаратора, первый вход ко торого соединен с общей шиной , а вт рой вход компаратора подключен к вы

ходу вычитающего усилителя и входу блока преобразо.вания напряжение - частота, выход которого соединен че рез элемент запрета с тактовым -входом реверсивного счетчика, выходы к торого соединены с информационными входами блока памяти, выходы которо подключены к информационным входам реверсивного счетчика, вход параллельной записи которогоч соединен с

25

30

40

18, включенным ha входе преобразова- шестым выходом блока управления, а

0

входом и Е1ЫХОДОМ синхронного режек- торного фкшьтра соответственно, элемент запрета, блок памяти, регистр, j информационные Входы которого соединены с выходами блока памяти, цифро- аналоговый преобразователь и блок управления, вход которого является тактовым входом синхронного режектор- «ного фильтра, а первый, второй, третий, четвертый и группа пятых выходов блока управления подключены соответственно к второму входу элемента запрета, входу записи регистра, входу записи, входу выборки и группе адресных входов блока памяти, причем блок управления содержит первьй формирователь импульсов, вход которого является входом блока управления, последовательно соединенные второй, третий и четвертый формирователи импульсов, выход третьего из которых является третьим выходом блока управления, пятый формирователь импульсов и счетчик, отличающий с 9 тем, что, с целью упрощения синхронного режекторного фильтра за счет уменьшения аппаратурных затрат, введены блок преобразования напряжение - частота, компаратор и реверсивный счетчик, вход управления режимом работы которого соединен с выходом компаратора, первый вход которого соединен с общей шиной , а второй вход компаратора подключен к вы ходу вычитающего усилителя и входу блока преобразо.вания напряжение - частота, выход которого соединен через элемент запрета с тактовым -входом реверсивного счетчика, выходы которого соединены с информационными входами блока памяти, выходы которого подключены к информационным входам реверсивного счетчика, вход параллельной записи которогоч соединен с

5

0

0

шестым выходом блока управления, а

| название | год | авторы | номер документа |

|---|---|---|---|

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Режекторный фильтр | 1986 |

|

SU1417180A2 |

| РЕЛЕ ЧАСТОТЫ | 2002 |

|

RU2208864C1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| РЕЛЕ ЧАСТОТЫ | 2002 |

|

RU2208865C1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1290348A1 |

Изобретение относится к области радиотехники и м.б. использовано для подавления помех. Цель изрбрет ния - упрощение устройства за счет уменьшения аппаратурных затрат. Устройство содержит вычитающий усилитель 1, элемент 4 запрета, блок 6 памяти, регистр 7, ЦАП 8 и блок 9 управления. В устройство введены блок 2 преобразования напряжение - частота, компаратор 3, реверсивный счетчик (PC) 5, а в блок 9 еще два формирователя im- пульсов. В устройстве операции интегрирования разности сигналов осуществляется за счет преобразования разностного сигнала с помощью блока 2 в последовательность импульсов и усреднения указанной последовательности с помощью PC 5. PC 5, кроме этого, выполняет также операцию суммирования результата интегрирования. Т. обр. блок 2 и PC 5 совмещают вьтолнение операций интегрирования, аналого-цифрового преобразования и накопления с усреднением. На выходе ЦАЛ 8 вьде- ляется сигнал помехи с частотой f . S Следовательно, зыход ЦАП 8 может использоваться а качестве избирательного выхода устг-ойства. 1 з. п. ф-лы, 5 ил. (Л

теля 19 напряжение-частота. При наличии преобразователя 19, который непосредственно формирует последо- В1ательность импульсов с частотой, Пропорциональной модулю входного нап- р1яжения, выпрямитель 18 двухполупе- риодный. может быть исключен.

о р м у л а

йзобретени

0

5

выходы регистра соединены с входами цифроаналогового преобразователя, выход которого подключен к второму входу вычитагацего усилителя, а в блок управления введены шестой и седьмой формирователи импульсов, причем вход, формирователя импульсов соединен с входом блока управления, выход четвертого формирователя импульсов соединен с тактовым входом счетчика и входом пятого формирователя импульсов, выход которого соединен с входом шестого и седьмого формирователей

импульсов, а выходы счетчика первого, второго, шестого н седьмого формирователей импульсов являются группой пятых выходов, четвертым, первым, вторым и шестым выходами блока управления соответственно.

At

Шгись

читыВание

4f

т

п

Фиг:з

ния напряжение - частота содержит последовательно.включенные двухполу- периодный вьтрямитель и преобразователь напряжение - частота, выход которого является выходом блока преобразования напряжение - частота, входом которого является вход двухпо- лупериодного выпрямителя,

, е .т

.д

15

16

П

и

п

и

я

и и

Фиг. If

Фиг. 5

| Авторское свидетельство СССР № 1187242, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-30—Публикация

1987-04-24—Подача