Известны адресные системы для запоминающих устройств.

Предлагаемая адресная система для запоминающего устройства с адресным регистром и формирователями отличается от известных тем, что для новышения надежности адресный регистр подключен к формирователям через шифратор, а формирователи подключены к накопителю через магнитный матричный дешифратор.

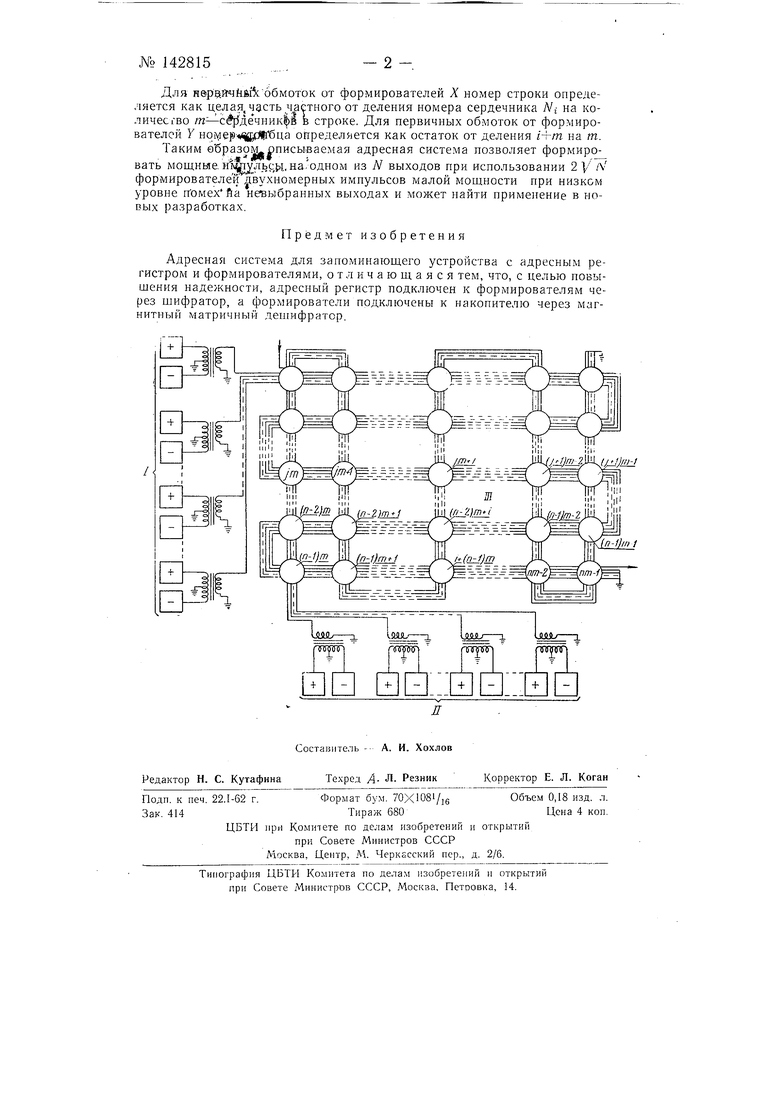

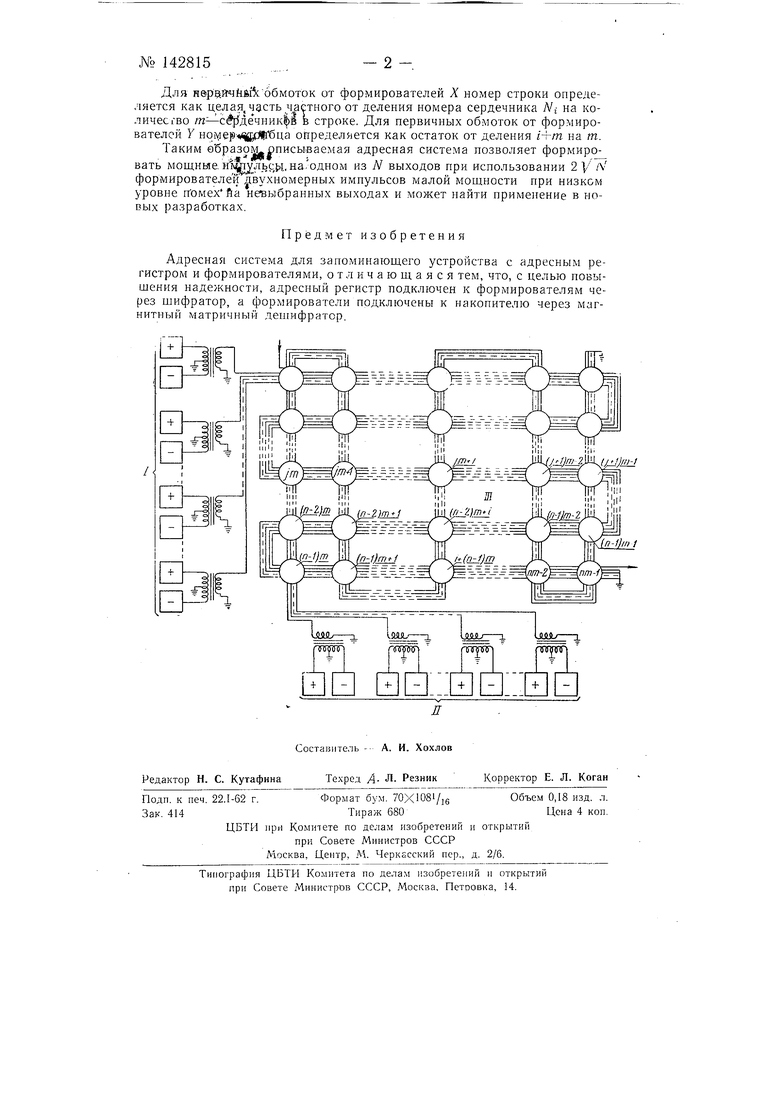

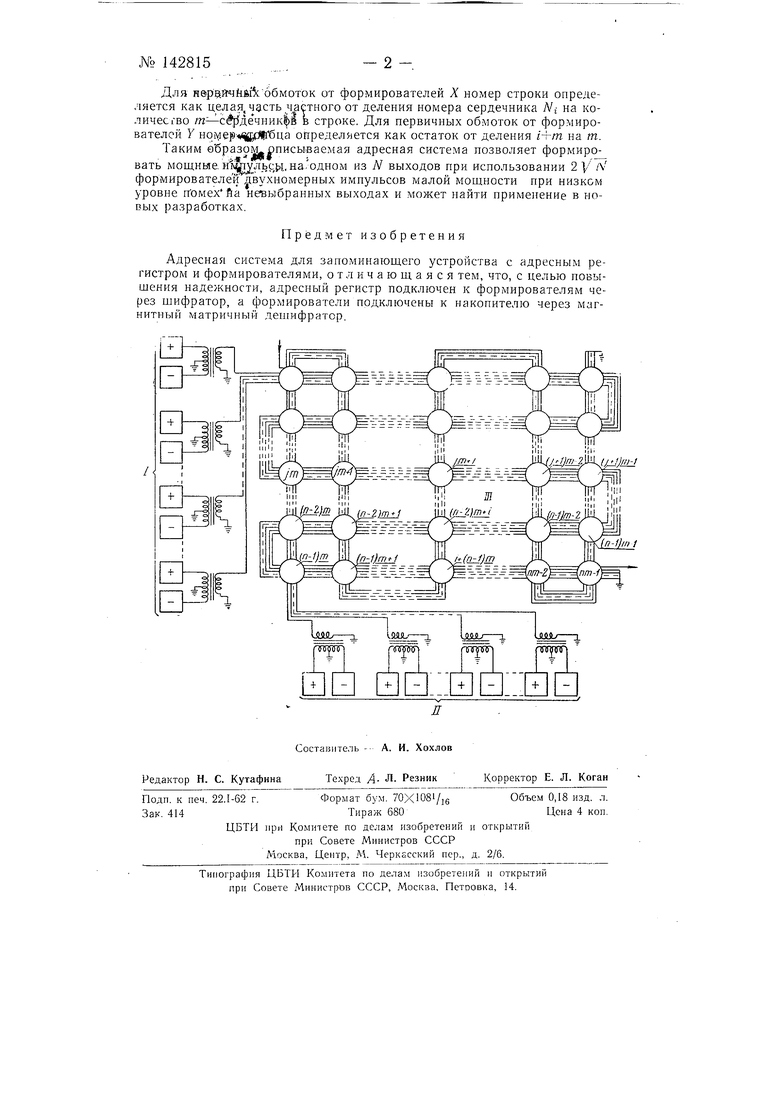

Принципиальная схема описываемой адресной системы дана на чертеже.

Адресная система состоит из адресного регистра, который через шифратор подключен к формирователям / и //, а последние подключены к запоминающему устройству через магнитный матричный дешифратор Я/. Применение шифратора обусловлено необходимостью создавать требуемые кодовые комбинации на каждую пару формирователей.

Выбор необходимого выхода производится путем перемагничивания соответствующего сердечника дешифратора ///, наступающего при совпадении суммарных токов строки и столбца, на пересечении которых находится этот выбранный сердечник. Выбор строки (или столбца) о уществляется подачей в первичные обмотки сердечников импульса тока положительной или отрицательной полярности от формирователей / и //. При этом первичные обмотки скоммутированы так, что при одной из возможных комбинаций пар формирователей выбирается только одна строка (столбец), а в других строках (столбцах) токи формирователей компенсируют друг друга. Такое построение адресной системы по ззоляет построить дещифратор на Л выходов при использовании 9 N пар формирователей, причем для перемагннчивания одного сердечника суммируется мощность 2 1/ Лформирователей.

Кроме того, в описываемой адресной системе имеется возможность коммутации первичных обмоток сердечников не только в виде матрицы, т. е. по столбцам и строкам, но и последовательно от 0-го до выхода. При этом первичнгзте обмотки как от формирователей / (А ), так и от формирователей // (У) обходят последовательно все сердечники от 0-го до Л/-ГО .при соответствующем направлении включения этих обмоток.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| ДВУХКОМПОНЕНТНЫЙ МАТРИЧНЫЙ ПРЕОБРАЗОВАТЕЛЬ МАГНИТНОГО ПОЛЯ | 2004 |

|

RU2290654C2 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Устройство для диагностирования троированных дискретных схем автоматики | 1990 |

|

SU1772783A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| Блок адресной выборки для запоминающего устройства | 1980 |

|

SU982083A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

Авторы

Даты

1961-01-01—Публикация

1959-06-15—Подача