ЧШг.} I 1-

Изобретение относится к автоматике и может быть использовано в системах i управления для контроля синхронизма частот.

Цель изобретения - повышение точности определения состояния синхронизма,

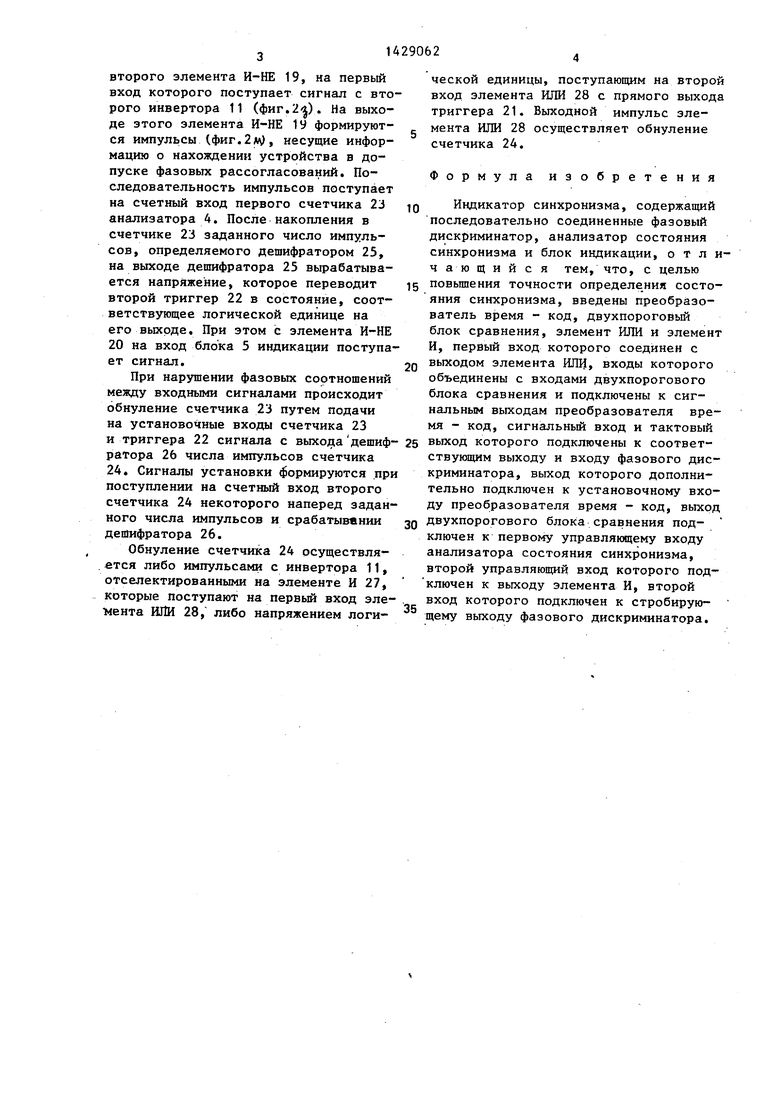

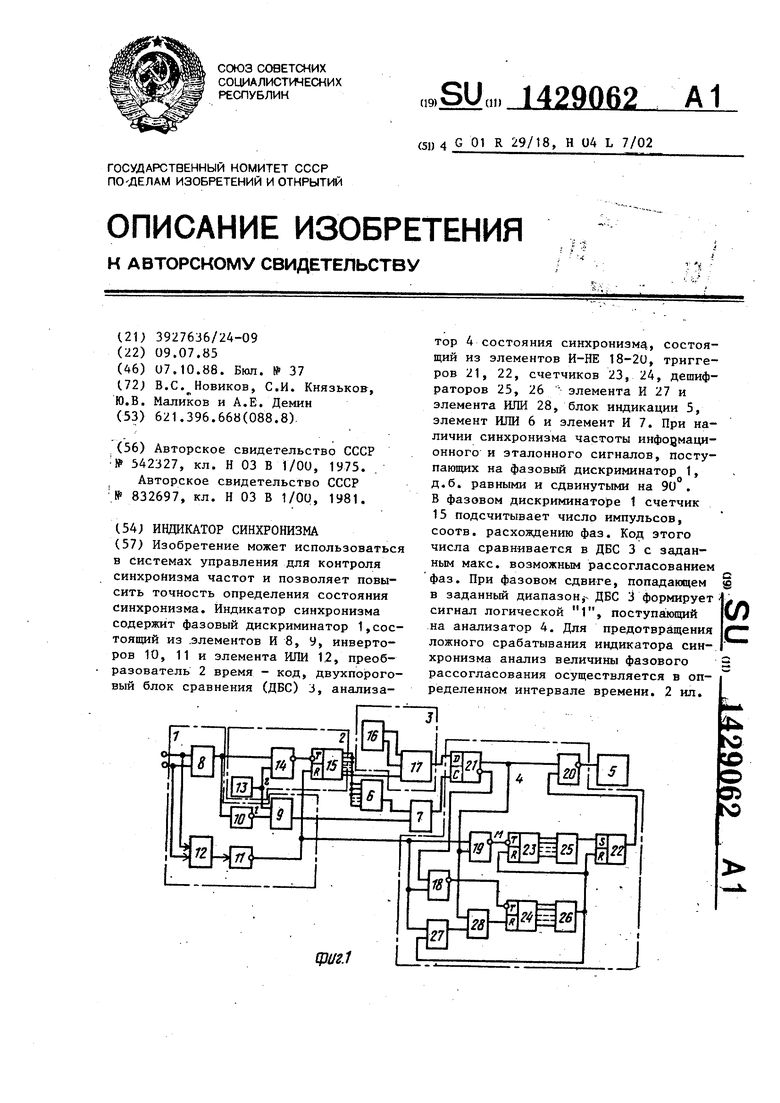

1- -На фиг. 1 представлена структурная электрическая схема индикатора синх- ронизма; на фиг. 2 - временные диаграммы работы устройства.

Индикатор синхронизма содержит фазовьм дискриминатор 1, преобразователь 2 время - код, двухпороговый блок 3 сравнения, анализатор 4 состояния синхронизма, блок 5 индикации, элемент ИЛИ 6 и элемент И 7.

Фазовый дискриминатор 1 содержит первый-и второй элементы И 8 и 9, первый и второй инверторы 10 и 11 и элемент ИЛИ 12. Преобразователь 2 время - код содержит генератор 13 тактовых импульсов элемент И-НЕ 14 и счетчик 15. Двухпороговый блок 3 срав нения содержит схему 16 формирования порогов и схему 17 сравнения.

Анализатор 4 состояния синхронизма содержит первый, второй и третий элементы И- НЕ 18-20, первый и второй триггеры 21 и 22, первый и второй счетчики 23 и 24, первый и второй дешифраторы 25 и 26, элемент И 27 я элемент ИЛИ 28.

Индикатор синхронизма работает еледунмцим образом.

Информационный и эталонный сигналы f и fg (.фиг. 2а,б ) поступают на соответствующие входы первого элемента И 8, а также на соответствукщие входы элемента ШШ;12 фазового дискримина-- тора 1. При наличии синхронизма частоты fy, и f g равны и сдвинуты на УО . На выходе первого элемента И 8 фазового дискриминатора образуются импуль сы (фиг.2б), которые поступают на - первый вход элемента И-й Е 14 преобразователя 2. На второй вход элемента И-НЕ 14 поступают тактовые импульсы с генератора 13 преобразователя 2 (фиг.2г). С вьпсода элемента И-НЕ 14 отселектированные импульсы (фиг.2д) подаются на счетный вход счетчика 15, который псщсчитывает число импульсов и хранит его до момента прихода на его установочный вход напряжения с , выхода элемента ИЛИ 12 фазового дне- криминатора, предварительно проинвер- тированного вторым инвертором 11

g

5

0 5

0

Qз Q .

5

(фиг.2г). При этом счетчик 15 устанавливается в состояние О, а двоичный код числа импульсов с выхода счетчика 15 поступает на схему 17 сравнения двухпорогового блока 3 сравнения, на которую со схемы 16 формирования порогов поданы два значения пороговых величин в двоичном коде. Максимальное число импульсов счета достигается при сдвиге фазы одного из сигналов относительно центрального положения на +90 , минимальное - при сдви- / ге фазы на -90. В соответствии с заданным максимально -возможным рассогласованием фаз установлены нижний и верхний пороги на схеме 16 формирования порогов 5 которые подаются на схему 17 сравнения.

При фазовых сдвигах входных сигналов, попадающих в заданный порогами диапазон, схема 17 сравнения формирует напряжение логической единицы, которое поступает на информационный вход триггера 21 анализатора 4 и переписывается на его выход (фиг.2л) синхроимпульсами генератора 13, поступающими с выхода элемента И 1 (фиг.2к) и отселектированными вторым , элементом И 9 (фиГв2 к) по стробу с первого инвертора 10 (фиг,2е) и на элементе И 7 с-элемента ИЛИ 6 (фиг, 2н. Начало импульса строба элемента ИЛИ 6 формируется первым импульсом счета в счетчике 15 преобразователя 2, Конец строба совпадает с. началом установочного импульса с выхода, второго инвертора 11 (фиг.2). При отсутствии на синхровходе триггера 21 импульсов считывания на прямом выходе этого триггера запоминается напряжение, соответствующее входному на момент последнего импульса считывания. Напряжение логической единицы триггера 21 поступает на первьй вход Третьего элемента И-НЕ 20.

Для предотвращения ложного срабатывания индикатора синхронизма и по- вышения .точности определения состояния синхронизма в индикаторе синхронизма предусмотрен анализ величины фазового рассогласования на некото- ром интервале времени, в течение которого схема сравнения выдает решения о нахождении фазового сдвига в пределах выставленного диапазона. Для этого с прямого выхода триггера 21 анализатора 4 напряжение логической единицы подается на второй вход

второго элемента И-НЕ 19, на первый вход которого поступает сигнал с второго инвертора 11 (фигЛ-). На выходе этого элемента И-НЕ 1У формируются импульсы (фиг.2AVj несущие информацию о нахождении устройства в допуске фазовых рассогласований. Последовательность импульсов поступает на счетный вход первого счетчика 23 анализатора 4. После накопления в счетчике 23 заданного число импульсов, определяемого дешифратором 25, на выходе дешифратора 25 вырабатывается напряжение, которое переводит второй триггер 22 в состояние, соответствующее логической единице на его выходе. При этом с элемента И-НЕ 20 на вход блока 5 индикации поступает сигнал.

При нарушении фазовых соотношений между входными сигналами происходит обнуление счетчика 23 путем подачи

Индикатор синхронизма, содержащий последовательно соединенные фазовый дискриминатор, анализатор состояния синхронизма и блок индикации, отли чающийся тем, что, с целью повьшения точности определения состояния синхронизма, введены преобразователь время - код, двухпороговый блок сравнения, элемент ИЛИ и элемент И, первый вход которого соединен с выходом элемента ИЛИ, входы которого объединены с входами двухпорогового блока сравнения и подключены к сигнальным выходам преобразователя время - код, сигнальный вход и тактовый

на установочные входы счетчика 23 и триггера 22 сигнала с выхода дешиф- 25 выход которого подключены к соответ- ратора 26 числа импульсов счетчика ствуклцим выходу и входу фазового дис- 24. Сигналы установки формируются при поступлении на счетный вход второго счетчика 24 некоторого наперед заданного числа импульсов и срабатывании зо дешифратора 26.

Обнуление счетчика 24 осуществляется либо импульсами с инвертора 11, отселектироваиными на элементе И 27, которые поступают на первьй вход эле35

криминатора, выход которого дополнительно подключен к установочному входу преобразователя время - код, выход двухпорогового блока сравнения подключен к первому управляющему входу анализатора состояния синхронизма, второй управляющий вход которого подключен к выходу элемента И, второй вход которого подключен к стробирую35

хента ИЛИ 28, либо напряжением логи- щему выходу фазового дискриминатора.

ческой единицы, поступающим на второй вход элемента ИЛИ 28 с прямого выхода триггера 21. Выходной импульс элемента ИЛИ 28 осуществляет обнуление счетчика 24.

Формула изобретения

Индикатор синхронизма, содержащий последовательно соединенные фазовый дискриминатор, анализатор состояния синхронизма и блок индикации, отличающийся тем, что, с целью повьшения точности определения состояния синхронизма, введены преобразователь время - код, двухпороговый блок сравнения, элемент ИЛИ и элемент И, первый вход которого соединен с выходом элемента ИЛИ, входы которого объединены с входами двухпорогового блока сравнения и подключены к сигнальным выходам преобразователя время - код, сигнальный вход и тактовый

выход которого подключены к соответ- ствуклцим выходу и входу фазового дис-

выход которого подключены к соответ- ствуклцим выходу и входу фазового дис-

криминатора, выход которого дополнительно подключен к установочному входу преобразователя время - код, выход вухпорогового блока сравнения подключен к первому управляющему входу анализатора состояния синхронизма, второй управляющий вход которого подключен к выходу элемента И, второй вход которого подключен к стробирующему выходу фазового дискриминатора.

. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Преобразователь кода в скорость вращения вала | 1988 |

|

SU1599991A1 |

| Устройство синхронизации по групповому сигналу в многоканальных системах связи | 1982 |

|

SU1107306A1 |

| Устройство формирования синхронизирующих последовательностей | 1982 |

|

SU1166331A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Цифровой частотно-фазовый дискриминатор | 1987 |

|

SU1494204A2 |

| Устройство для синхронизации кодовых комбинаций,ограниченных стандартными паузами | 1977 |

|

SU660289A2 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство фазирования регенераторов цифрового сигнала | 1978 |

|

SU786036A1 |

Изобретение может использоваться в системах управления для контроля синхронизма частот и позволяет повысить точность определения состояния синхронизма. Индикатор синхронизма содержит фазовый дискриминатор 1,состоящий из .элементов И 8, У, инверторов 10, 11 и элемента ИЛИ 12, преобразователь 2 время - код, двухпо рого- вый блок сравнения (ДБС) 3, анализатор 4 состояния синхронизму, состоящий из элементов И-НЕ 18-20, триггеров 21, 22, счетчиков 23, 24, дешифраторов 25, 26 элемента И 27 и элемента ИЛИ 28, блок индикации 5, элемент ИЛИ 6 и элемент И 7. При наличии синхронизма частоты инфодмаци- онного и эталонного сигналов, поступающих на фазовый дискриминатор 1, д.б. равными и сдвинутыми на 90 , В фазовом дискриминаторе 1 счетчик 15 подсчитывает число импульсов, соотв. расхождению фаз. Код этого числа сравнивается в ДБС 3 с заданным макс, возможным рассогласованием фаз. При фазовом сдвиге, попадающем в заданньм диапазон,- ДБС 3 формирует сигнал логической 1, поступалщий на анализатор 4. Для предотвращения ложного срабатывания индикатора син-. хронизма анализ величины фазового рассогласования осуществляется в определенном интервале времени. 2 нл. /)

LJ

L

li

и к

я

п

.2

И

illlilllllllllllimillllllHIIII

JL

JL

| Устройство для индикации синхронизма | 1975 |

|

SU542327A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Индикатор синхронизма | 1979 |

|

SU832697A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-07—Публикация

1985-07-09—Подача