(54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1374398A2 |

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1684906A1 |

| Цифровой генератор периодических функций | 1987 |

|

SU1441372A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1774464A1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1525694A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1210198A1 |

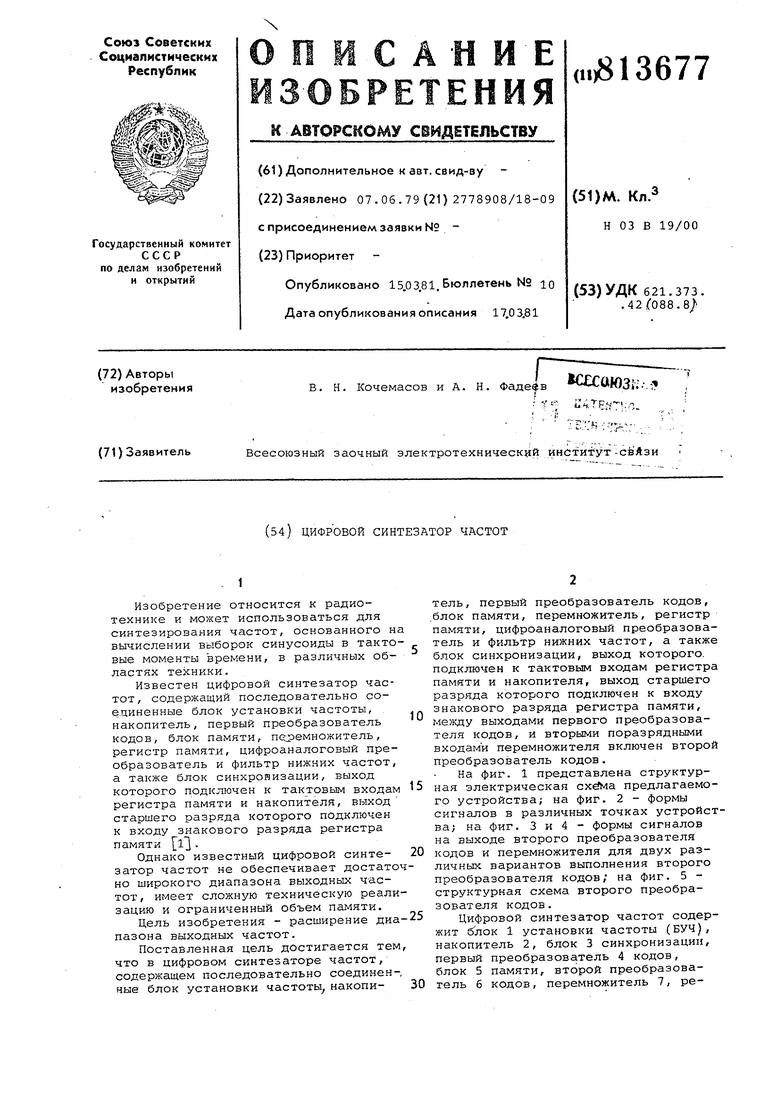

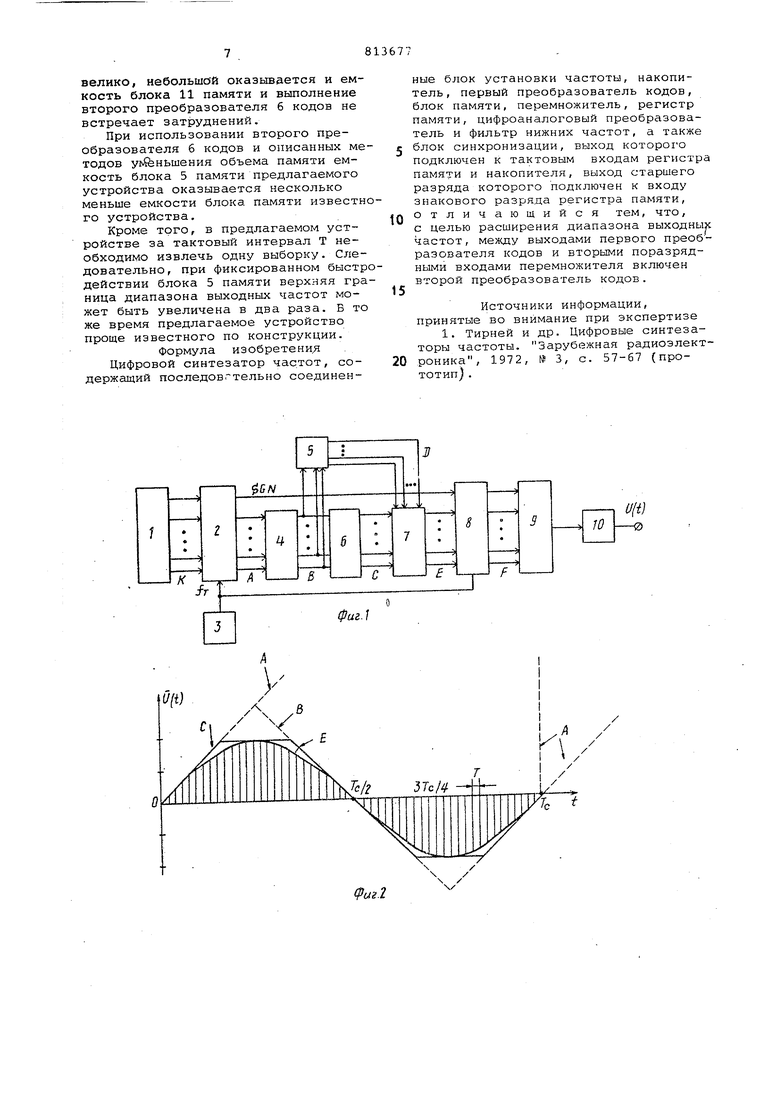

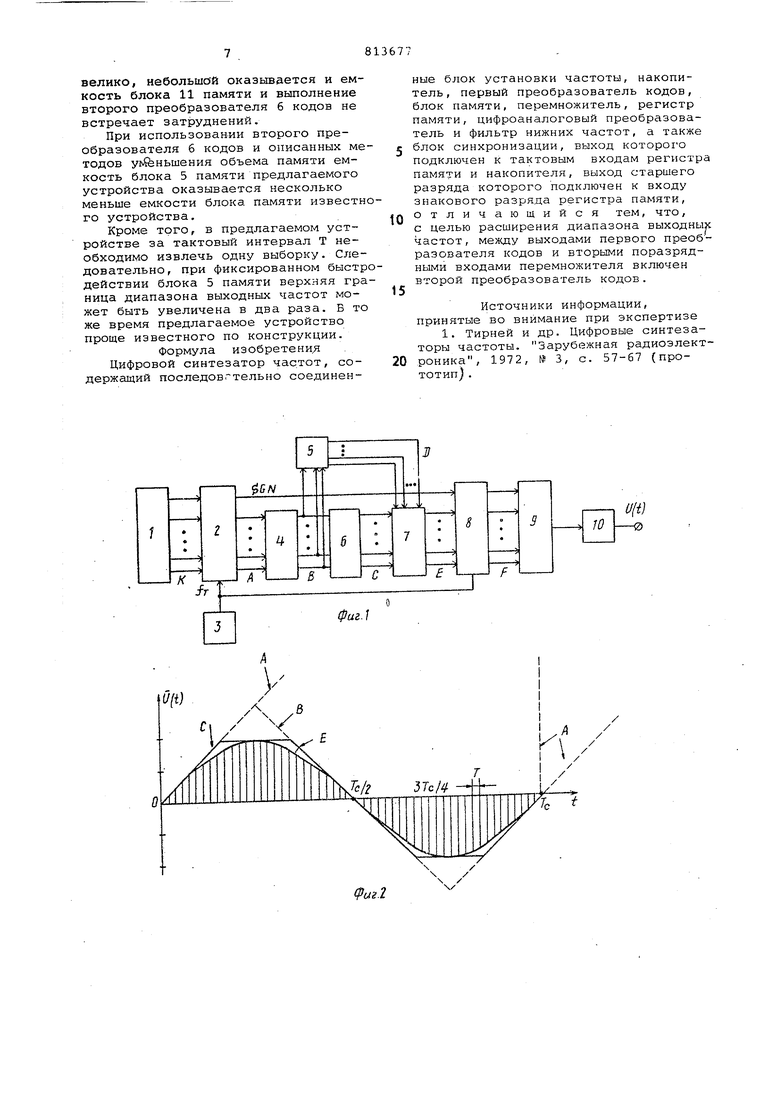

Изобретение относится к радиотехнике и может использоваться для синтезирования частот, основанного н вычислении выборок синусоиды в такто вые моменты времени, в различных областях техники. Известен цифровой синтезатор частот, содержащий последовательно соединенные блок установки частоты, накопитель, первый преобразователь кодов, блок памяти, пе ремножитель, регистр памяти, цифроаналоговый преобразователь и фильтр нижних частот а также блок синхронизации, выход которого подключен к тактовым входа регистра памяти и накопителя, выход старшего разряда которого подключен к входу знакового разряда регистра памяти 1 . Однако известный цифровой синтезатор частот не обеспечивает достато но широкого диапазона ВЫХОДНЕ ГХ частот, имеет сложную техническую реал зацию и ограниченный объем памяти. Цель изобретения - расширение ди пазона выходных частот. Поставленная цель достигается тем что в цифровом синтезаторе частот, содержащем последовательно соединен ные блок установки частоты накопитель, первый преобразователь кодов, блок памяти, перемножитель, регистр памяти, цифроаналоговый преобразователь и фильтр нижних частот, а также блок синхронизации, выход которого. подключен к тактовым входам регистра памяти и накопителя, выход старшего разряда которого подключен к входу знакового разряда регистра памяти, между выходами первого преобразователя кодов, и вторыми поразрядными входами перемножителя включен второй преобразователь кодов. На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - формы сигналов в различных точках устройства; на фиг. 3 и 4 - формы сигналов на выходе второго преобразователя кодов и перемножителя для двух различных вариантов выполнения второго преобразователя кодов; на фиг. 5 структурная схема второго преобразователя кодов. Цифровой синтезатор частот содержит блок 1 установки частоты (БУЧ), накопитель 2, блок 3 синхронизации, первый преобразователь 4 кодов, блок 5 памяти, второй преобразователь 6 кодов, перемножитель 7, реРистр 8 памятн, цифpoaнaJrIoгoвый преобразователь 9 (ЦАП), фильтр 10 нижних частот (ФНЧ).

Цифровой синтезатор частот работает следующим образом.

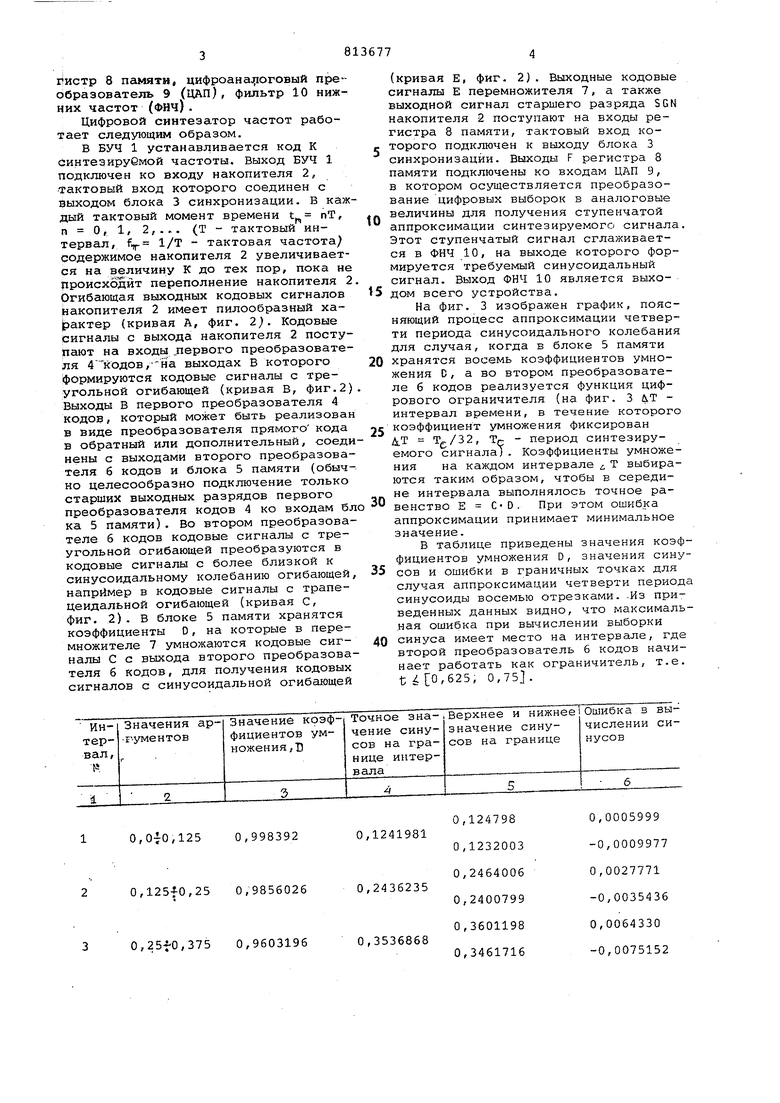

В БУЧ 1 устанавливается код К синтезируемой частоты. Выход БУЧ 1 подключен ко входу накопителя 2, тактовый вход которого соединен с выходом блока 3 синхронизации. В каждый тактовый момент времени t пТ, п О, 1, 2, (т - тактовый интервал, f 1/т - тактовая частота содержимое накопителя 2 увеличивает° Д° ПОР пока не происходит переполнение накопителя 2 Огибающая выходных кодовых сигналов накопителя 2 имеет пилообразный ха|рактер (кривая А, фиг. 2). Кодовые сигналы с выхода накопителя 2 поступают на входы .первого преобразователя 4 кодов, выходах В которого формируются кодовые сигналы с треугольной огибающей (кривая в, фиг.2) Выходы В первого преобразователя 4 кодов, который может быть реализован в виде преобразователя прямого кода в обратный или дополнительный, соединены с выходами второго преобразователя б кодов и блока 5 памяти (обычно целесообразно подключение только старших выходных разрядов первого преобразователя кодов 4 ко входам бл ка 5 памяти). Во втором преобразователе б кодов кодовые сигналы с треугольной огибающей преобразуются в кодовые сигналы с более близкой к синусоидальному колебанию огибающей, например в кодовые сигналы с трапецеидальной огибающей (кривая С, фиг. 2). В блоке 5 памяти хранятся коэффициенты О, на которые в перемножителе 7 умножаются кодовые сигналы С с выхода второго преобразователя б кодов, для получения кодовых сигналов с синусоидальной огибающей

0,0-J-0,125 0,998392 0,1241981

2 0,,25 0,9856026 0,2436235

3 0,25fO,375 0,9603196 0,3536868

(кривая Е, фиг. 2). Выходные кодовые сигналы Е перемножителя 7, а также выходной сигнал старшего разряда SGN накопителя 2 поступают на входы регистра 8 памяти, тактовый вход которого подключен к выходу блока 3 синхронизации. Выходы F регистра 8 памяти подключены ко входам ЦАП 9, в котором осуществляется преобразование цифровых выборок в аналоговые величины для получения ступенчатой аппроксимации синтезируемого сигнала Этот ступенчатый сигнал сглаживается в ФНЧ 10, на выходе которого формируется требуемый синусоидальный сигнал. Выход ФНЧ 10 является выходом всего устройства.

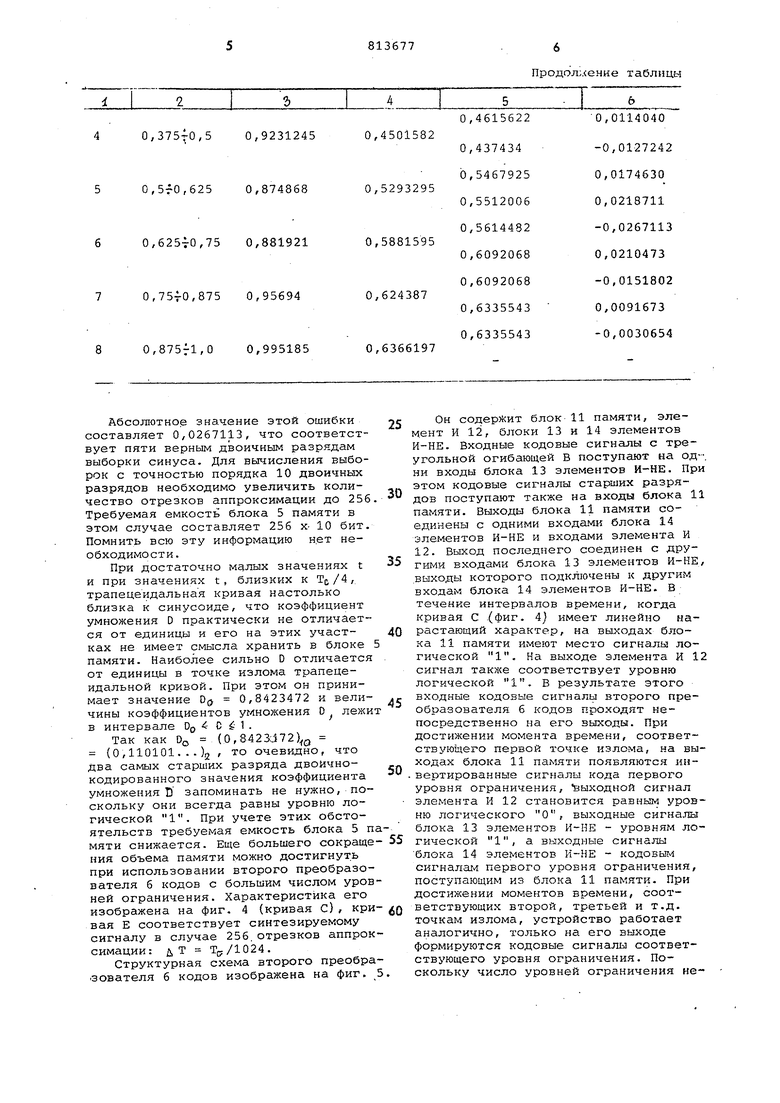

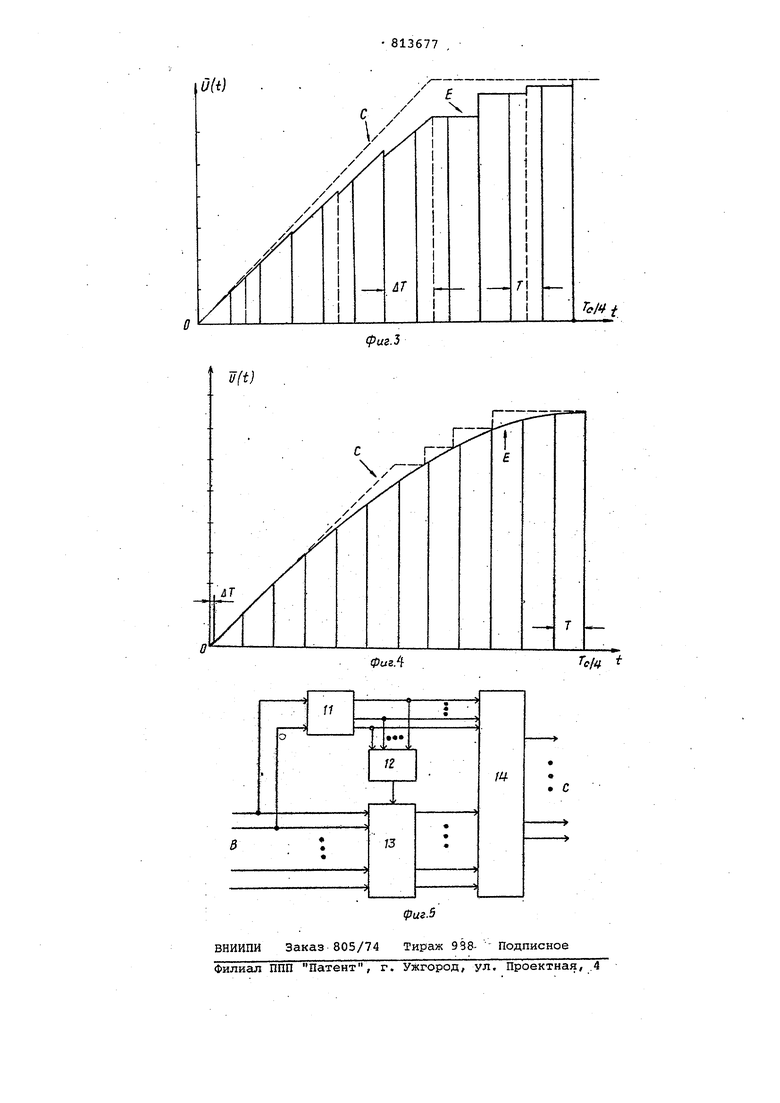

На фиг. 3 изображен график, поясняющий процесс аппроксимации четверти периода синусоидального колебания для случая, когда в блоке 5 памяти хранятся восемь коэффициентов умножения D, а во втором преобразователе б кодов реализуется функция цифрового ограничителя (на фиг. 3 й,т интервал времени, в течение которого коэффициент умножения фиксирован Д.Т , Тг; - период синтезируемого сигнала). Коэффициенты умножения на каждом интервале Т выбираются таким образом, чтобы в середине интервала выполнялось точное равенство Е C-D. При этом ошибка аппроксимации принимает минимальное значение.

В таблице приведены значения коэффициентов умножения D, значения синусов и ошибки в граничных точках для случая аппроксимации четверти период синусоиды восемью отрезками. .Из приведенных данных видно, что максимальная ошибка при вычислении выборки синуса имеет место на интервале, где второй преобразователь 6 кодов начинает работать как ограничитель, т.е. t 0,625, 0,75.

0,0005999

-0,0009977

0,0027771

-0,0035436

0,0064330

-0,0075152

Абсогаотное значение этой ошибки составляет 0,0267113, что соответствует пяти верным двоичным разрядам выборки синуса. Для вЕлчисления выборок с точностью порядка 10 двоичных разрядов необходимо увеличить количество отрезков аппроксимации до 256. Требуемая емкость блока 5 памяти в этом случае составляет 256 х- 10 бит. Помнить всю эту информацию нет необходимости.

При достаточно малых значениях t и при значениях t, близких к Ti/4,. трапецеидальная кривая настолько близка к синусоиде, что коэффициент умножения D практически не отличается от единицы и его на этих участках не имеет смысла хранить в блоке 5 памяти. Наиболее сильно D отличается от единицы в точке излома трапецеидальной кривой. При этом он принимает значение 0 0,8423472 и величины коэффициентов умножения О лежит в интервале Dp С - 1 .

так как DO {0,8423J72)Q {0,110101. .. )2 , то очевидно, что два самых старших разряда двоичнокодированного значения коэффициента умножения Б запоминать не нужно, поскольку они всегда равны уровню логической 1. При учете этих обстоятельств требуемая емкость блока 5 памяти снижается. Еще большего сокращения объема памяти можно достигнуть при использовании второго преобразователя 6 кодов с большим числом уровней ограничения. Характеристика его изображена на фиг. 4 (кривая С), кривая Е соответствует синтезируемому сигналу в случае 256.отрезков аппроксимации: дТ Тр/1024.

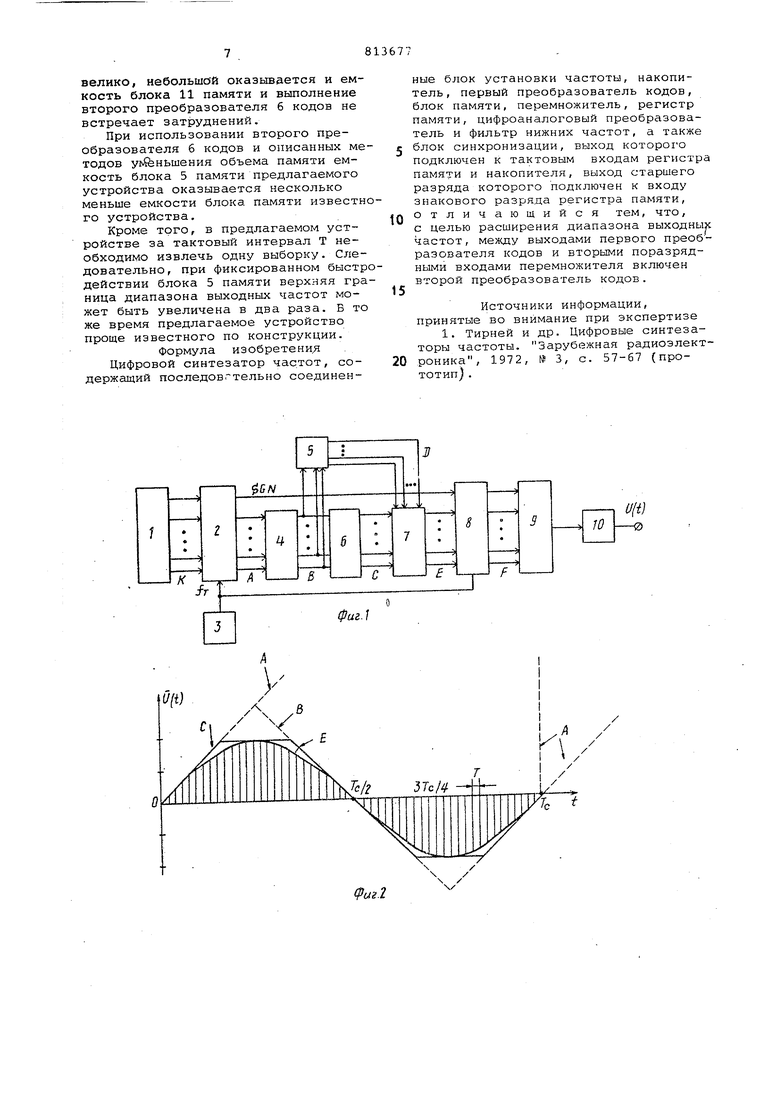

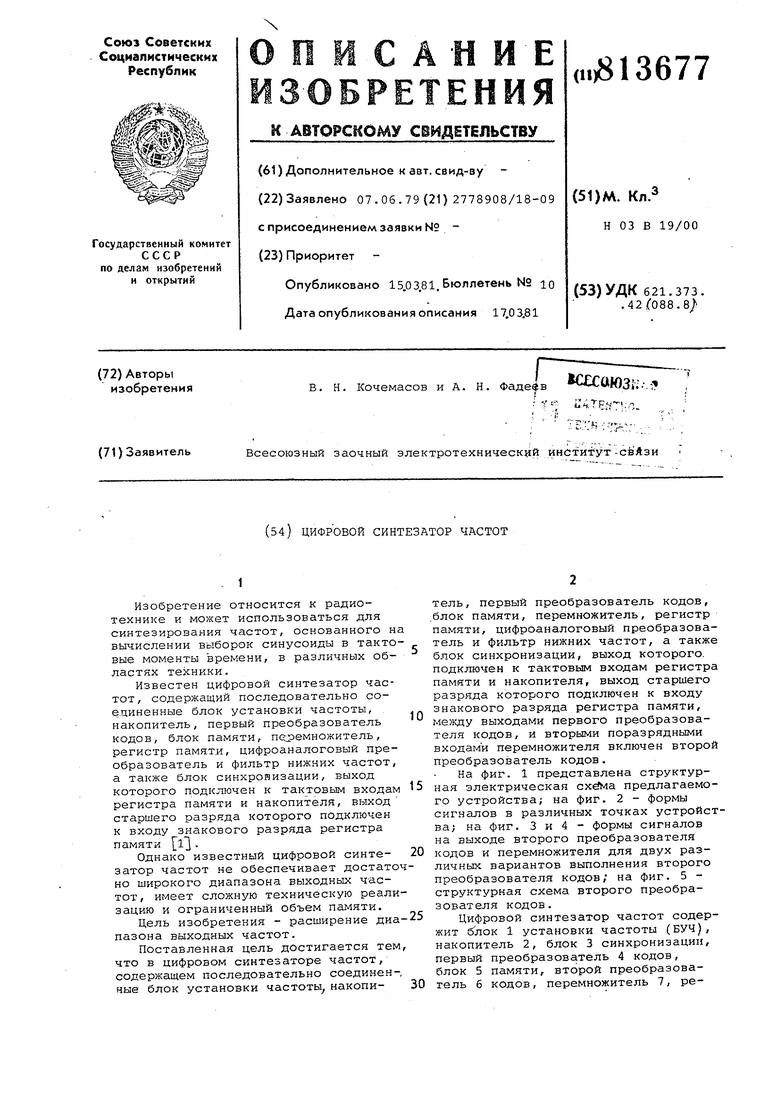

Структурная схема второго преобразователя 6 кодов изображена на фиг. 5

Продол;.ение таблицы

Он содержит блок 11 памяти, элемент И 12, блоки 13 и 14 элементов И-НЕ. Входные кодовые сигналы с треугольной огибающей В поступают на одни входы блока 13 элементов И-НЕ. При этом кодовые сигналы старших разрядов поступают также на входы блока 11 памяти. Выходы блока 11 памяти соединены с одними входами блока 14 элементов И-НЕ и входами элемента И 12. Выход последнего соединен с другими входами блока 13 элементов И-НЕ выходы которого подключены к другим входам блока 14 элементов И-НЕ. В течение интервалов времени, когда кривая С .(фиг. 4} имеет линейно нарастающий характер, на выходах блока 11 памяти имеют место сигналы логической 1. На выходе элемента И 1 сигнал также соответствует уровню логической 1. В результате этого входные кодовые сигналы второго преобразователя 6 кодов проходят непосредственно на его выходы. При достижении момента времени, соответствующего первой точке излома, на выходах блока 11 памяти появляются ин. вертированные сигналы кода первого уровня ограничения, выходной сигнал элемента И 12 становится равным уровню логического О, выходные сигна,пы блока 13 элементов И-НЕ - уровням логической 1, а выходные сигналы блока 14 элементов И-НЕ - кодов-оп cигнaлaгvI первого уровня ограничения, поступающим из блока 11 памяти. При достижении моментов времени, соответствующих второй, третьей и т.д. точкам излома, устройство работает аналогично, только на его выходе формируются кодовые сигналы соответствующего уровня ограничения. Поскольку число уровней ограничения невелико, небольшой оказывается и емкость блока 11 памяти и выполнение второго преобразователя 6 кодов не встречает затруднений.

При использовании второго преобразователя б кодов и описанных методов y feньшeния объема памяти емкость блока 5 памяти предлагаемого устройства оказывается несколько меньше емкости блока, памяти известного устройства.

Кроме того, в предлагаемом устройстве за тактовый интервал Т необходимо извлечь одну выборку. Следовательно, при фиксированном быстродействии блока 5 памяти верхняя граница диапазона выходных частот может быть увеличена в два раза. В то же время предлагаемое устройство проще известного по конструкции. Формула изобретения

Цифровой синтезатор частот, содержащий последовгтельно соединенные блок установки частоты, накопитель, первый преобразователь кодов, блок памяти, перемножитель, регистр памяти, цифроакалоговый преобразователь и фильтр нижних частот, а также блок синхронизации, выход которого подключен к тактовым входам регистра памяти и накопителя, выход старшего разряда которого подключен к входу знакового разряда регистра памяти. Отличающийся тем, что,

0 с целью расширения диапазона выходных частот, между выходами первого преобразователя кодов и вторыми поразрядными входами перемножителя включен второй преобразователь кодов.

5

Источники информации, принятые во внимание при экспертизе

«г7

U(i)

У

Авторы

Даты

1981-03-15—Публикация

1979-06-07—Подача