fW

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код по модулю К | 1989 |

|

SU1732472A1 |

| Устройство для преобразования количества единиц двоичного кода в код по модулю К | 1987 |

|

SU1527714A1 |

| Устройство для умножения по модулю К | 1989 |

|

SU1691834A1 |

| Преобразователь кодов | 1986 |

|

SU1361722A1 |

| Преобразователь кодов | 1986 |

|

SU1361723A1 |

| Устройство для контроля параллельного двоичного кода по модулю К | 1986 |

|

SU1361557A1 |

| Устройство для свертки двоичного кода в код по модулю К | 1986 |

|

SU1425845A1 |

| Устройство для контроля параллельного двоичного кода по модулю К | 1986 |

|

SU1425676A1 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения устройств передачи и переработки дискретной информации. Цель изобретения - сокращение количества оборудования. Преобразователь содержит двоичный сумматор 1, многопороговый блок 2 и приоритетный блок 3. Двоичньй код С поступает на входы сумматора 1, а также на входы блока 2. При этом на J-M выходе блока 2 появляется единичный сигнал, если сумма входных кодов больше или равна j К. Сигналы с выходов блока 2 поступают на дходы блока 3, ас блока 3 - на втору} группу входов сумматора 2, причем значение формируемого кода таково, что сигнал на выходах суммы сумматора 1 равен С mod к . 4 ИЛ.

Изобретение относится к вьгчисли- те|льной технике и может быть исполь- зс|вано при построении систем передачи и переработки дискретной информации. Цель изобретения - сокращение ко- лЦчества оборудования.

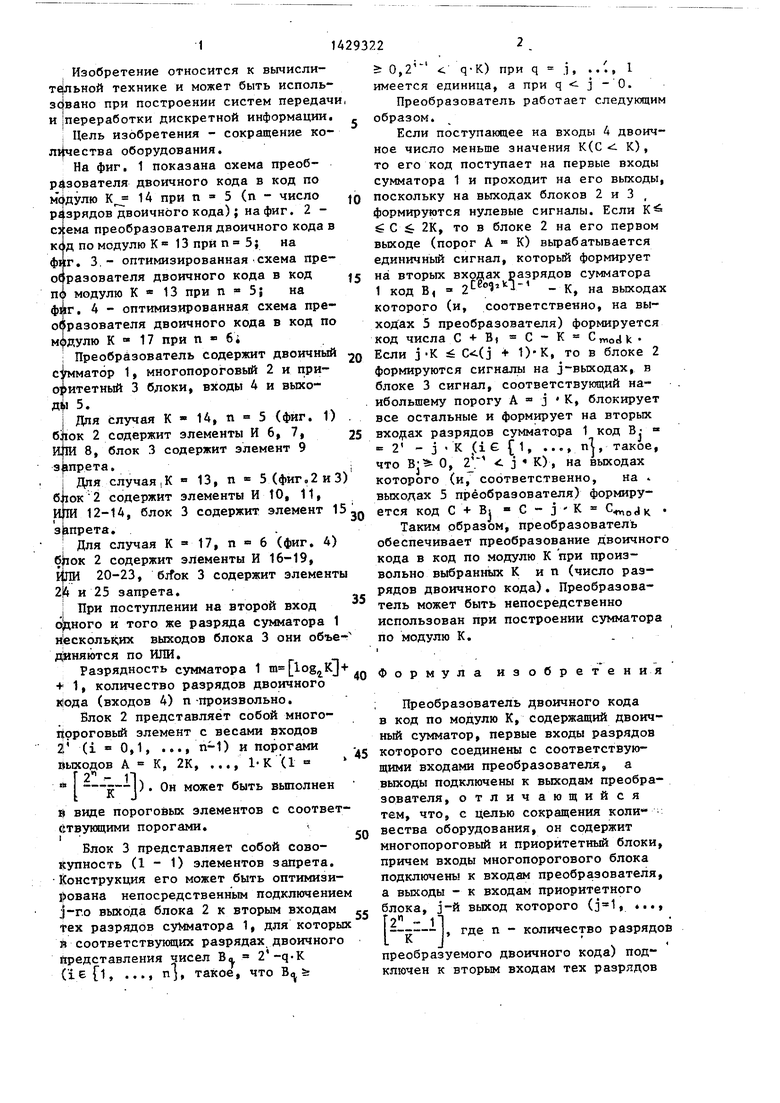

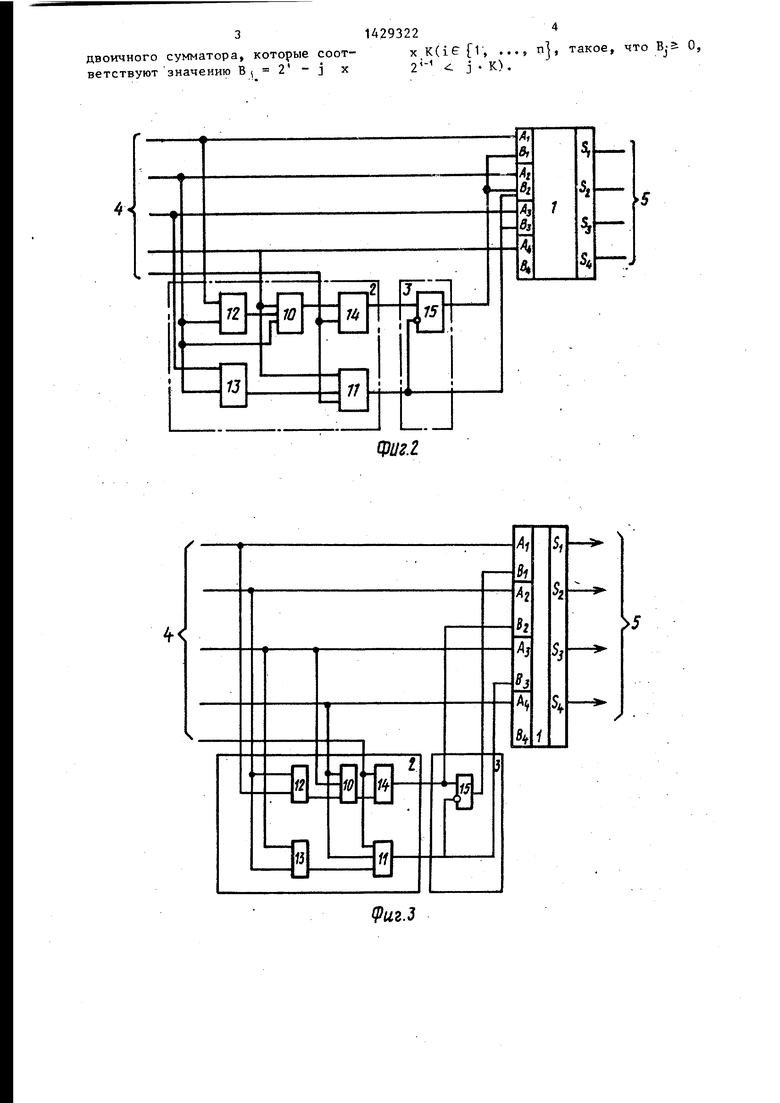

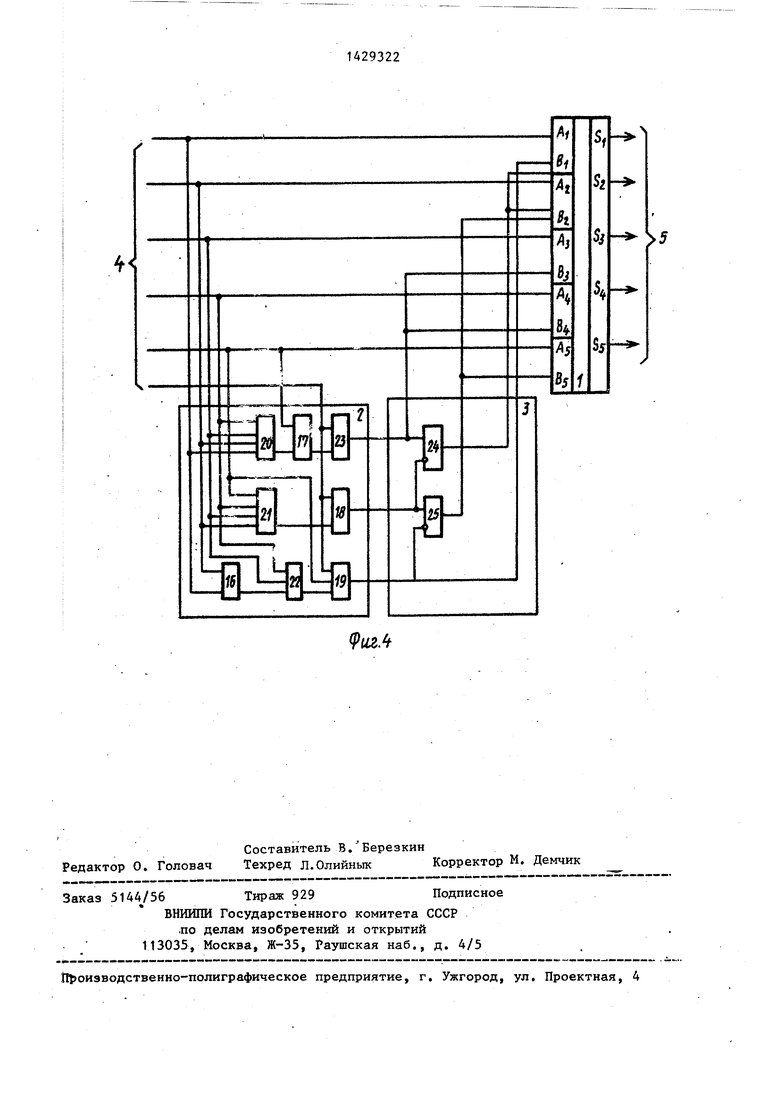

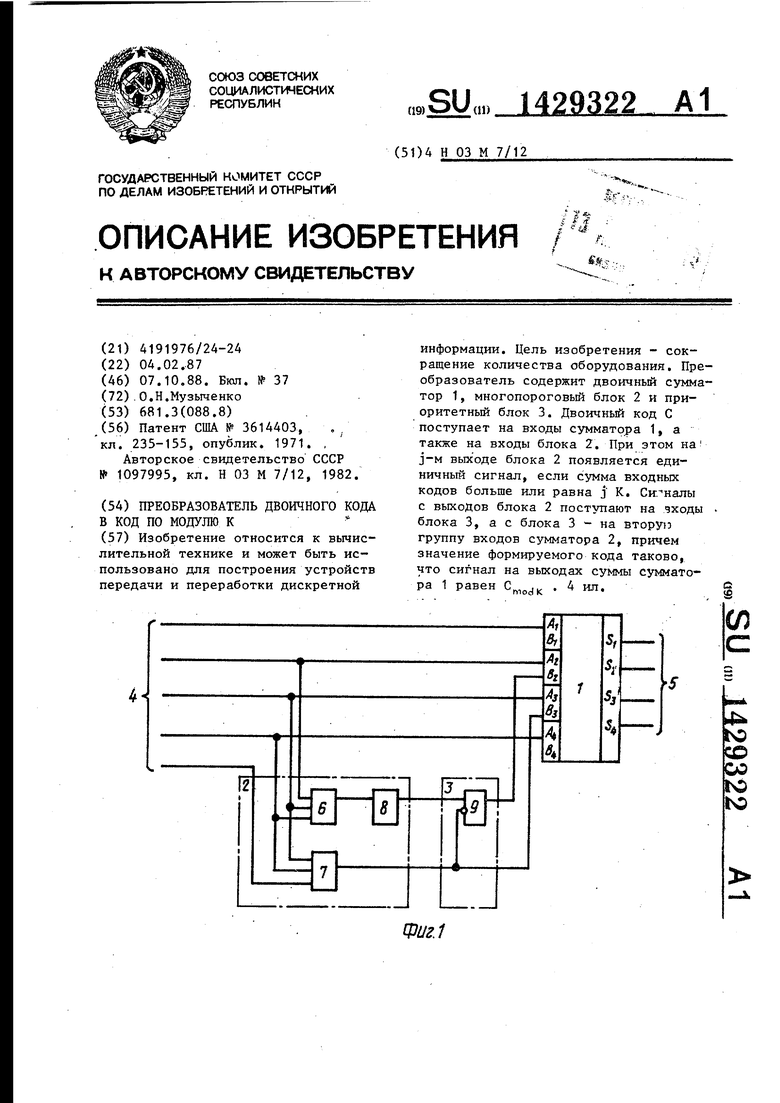

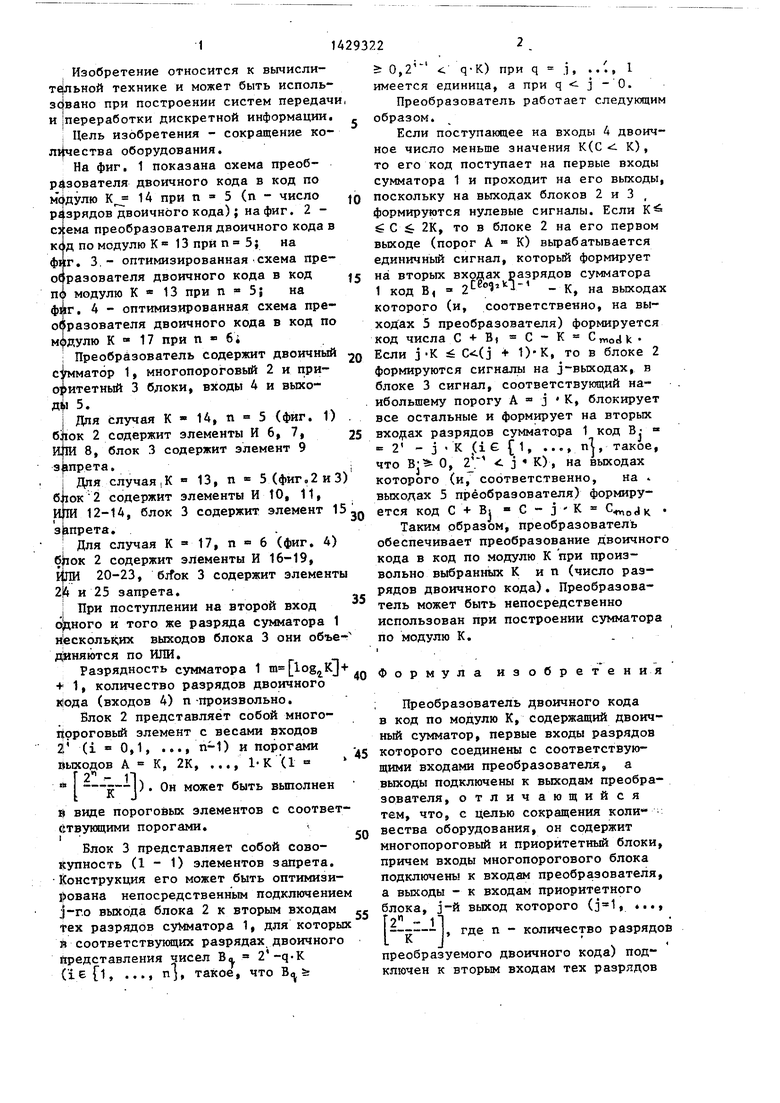

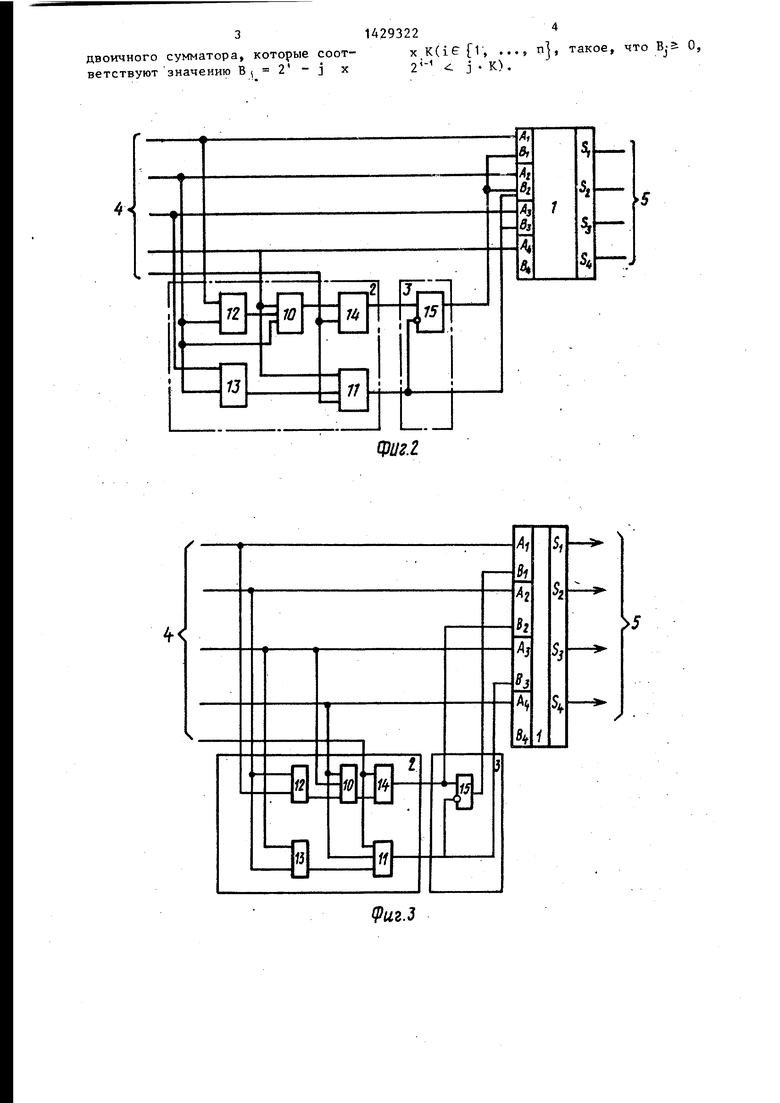

На фиг. 1 показана схема преоб- р зователя двоичного кода в код по К 1А при п « 5 (п - число рг.зрядов двоичного кода); на фиг, 2 - С}:ема преобразователя двоичного кода в КС1Д по модулю К 13 при п 5; на фиг. 3.- оптимизированная схема пре- оСфазователя двоичного кода в код п модулю К 13 при п 5; на фиг. А оптимизированная схема преобразователя двоичного кода в код по модулю К 17 при п 6i

; Преобразователь содержит двоичный сумматор 1, многопороговый 2 и при- о итетный 3 блоки, входы 4 и выхо- 5.

i Дпя случая К 14, п 5 (фиг. 1) блок 2 содержит элементы И 6, 7, ИТИ 8, блок 3 содержит элемент 9 з.шрета.

Для случая |К « 13, п 5() содержит элементы И 10, 11, Ита 12-14, блок 3 содержит элемент 15 запрета.

Для случая К 17, п 6 (фиг. 4) бЬок 2 содержит элементы И 16-19, фм 20-23, 6jfoK 3 содержит элементы 2J4 и 25 запрета.

1 При поступлении на второй вход и того же разряда сумматора 1 н ескольких выходов блока 3 они объедяняются по ИЛИ.

Разрядность сумматора 1 1, количество разрядов двоичного (входов 4) п -произвольно.

Блок 2 представляет собой много- Пороговый элемент с весами входов 2 (i 0,1, ..., п-1) и порогами К, 2К, ..., 1-К U

И виде пороговых элементов с соответбтвующими порогами.

I

Блок 3 представляет собой совокупность (1 - 1) элементов запрета. Конструкция его может быть оптимизи- 1} ована непосредственным подключением j-ro выхода блока 2 к вторым входам tex разрядов су1иматора 1, для которых и соответствующих разрядах двоичного Представления чисел В« 2 -q.K - такое, что В

выходов А

Он может быть вьтолнен

(ie 1, .... n.

o

5

0

5

0

5

i 0, q-K) при q j, ... , 1 имеется единица, а при q j - 0.

Преобразователь работает следующим образом.

Если поступающее на входы 4 двоичное число меньше значения К(С « К), то его код поступает на первые входы сумматора 1 и проходит на его выходы, поскольку на выходах блоков 2 и 3 , формируются нулевые сигналы. Если К ё С jt 2К, то в блоке 2 на его первом выходе (порог А К) вырабатывается единичный сигнал, который формирует на вторых входах разрядов сумматора 1 код В, - К, на выходах которого (и, соответственно, на выходах 5 преобразователя) формируется код числа С + В С - К . Если j-К : C c(j + 1) К, то в блоке 2 формируются сигналы на j-выходах, в блоке 3 сигнал, соответствующий наибольшему порогу А j К, блокирует все остальные и формирует на вторых Bxofl(ax разрядов сумматора 1 код В: 2 -j K(, ...,пЯ, такое, что В О, 2. j К), на выходах которого (и, соответственно, на . выходах 5 преобразователя) формируется код С + В - С - 3 К

Таким образом, преобразователь обеспечивает преобразование двоичного кода в код по модулю К при произвольно выбранных К и п (число разрядов двоичного кода). Преобразователь может быть непосредственно использован при построении сумматора по модулю К.

40 Формула изобретения

5

0

5

; Преобразователь двоичного кода в код по модулю К, содержащий двоичный сумматор, первые входы разрядов которого соединены с соответствующими входами преобразователя, а выходы подключены к выходам преобразователя, отличающийся тем, что, с целью сокращения коли- вества оборудования, он содержит многопороговый и приоритетный блоки, причем входы многопорогового блока подключены к входам преобразователя, а выходы - к входам приоритетного блока, j-й выход которого (, ..,

F2 ll -L где n - количество разрядов

L J

преобразуемого двоичного кода) подключен к вторым входам тех разрядов

31А29322

двоичного сумматора, которые соот- x,K(ie 1, ..., п}, такое, что Bj& О,

- : 2- j . К).

ветствуют значению В 2 - J

4-

фцг.г

5

(Риг.з

5

te4

| Патент США № 3614403, , , кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| , Авторское свидетельство СССР № 1097995, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-07—Публикация

1987-02-04—Подача