.J

Фиг.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем передачи и переработки дискрет- ной информадаи.

Цель изобретения - расширение области применения устройства за счет возможности получения произвольного значения модуля

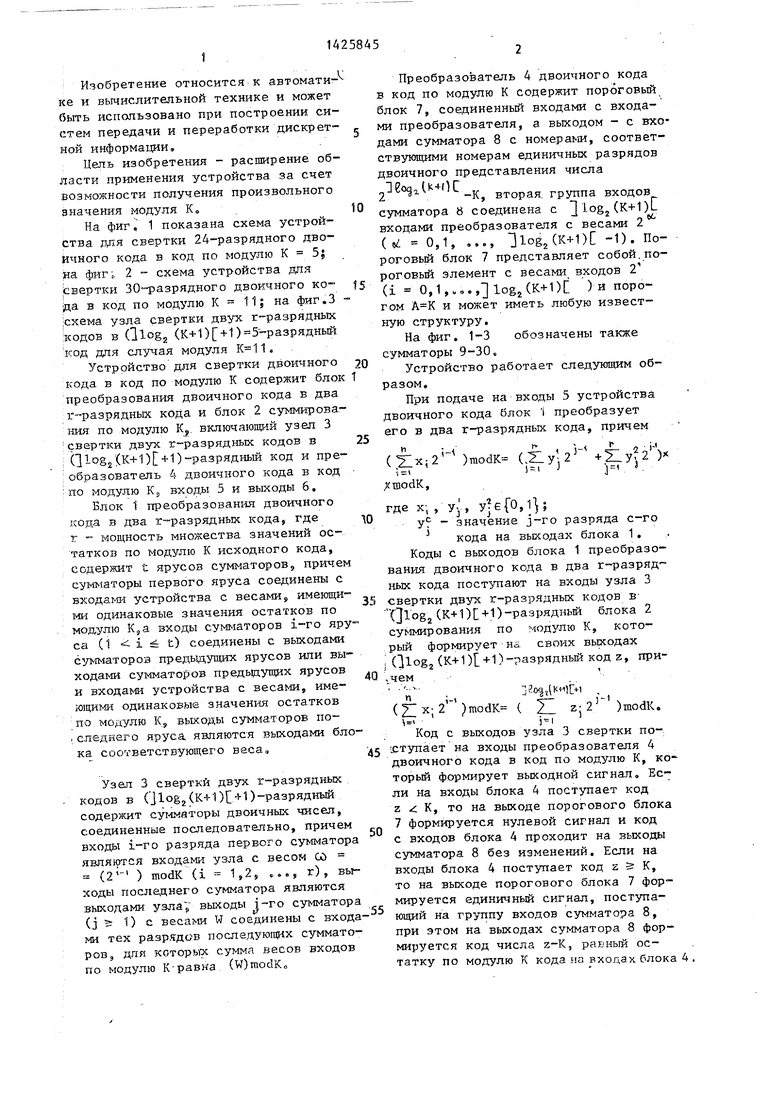

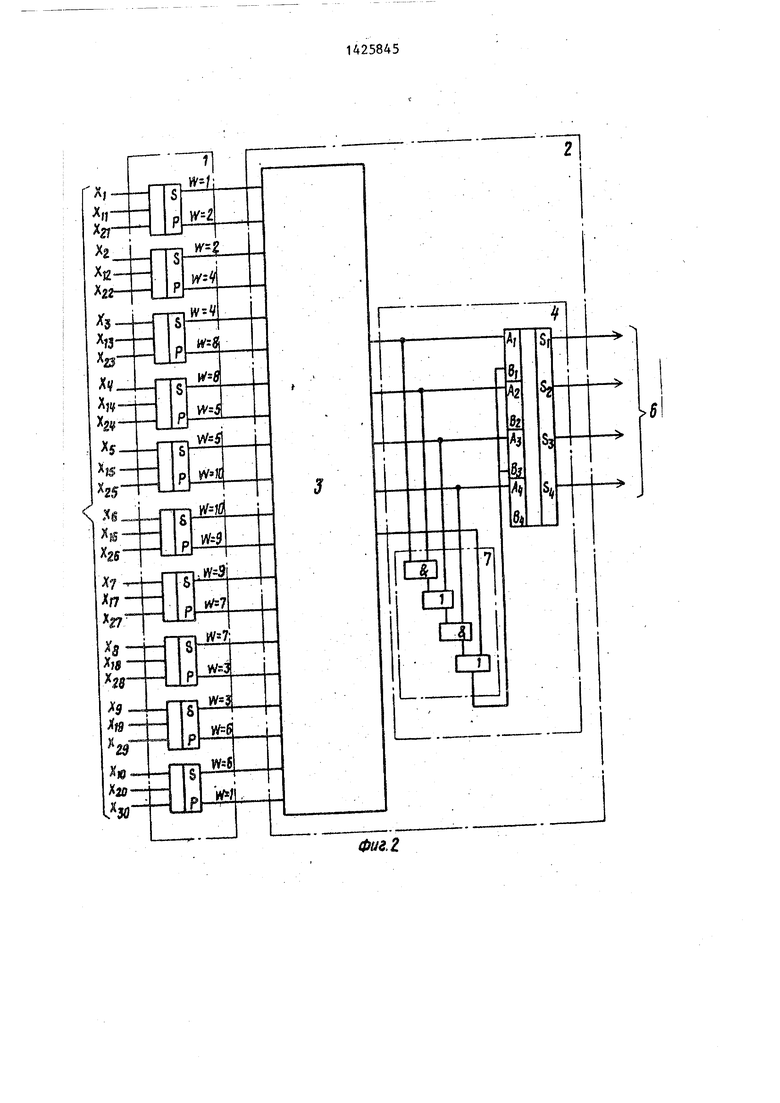

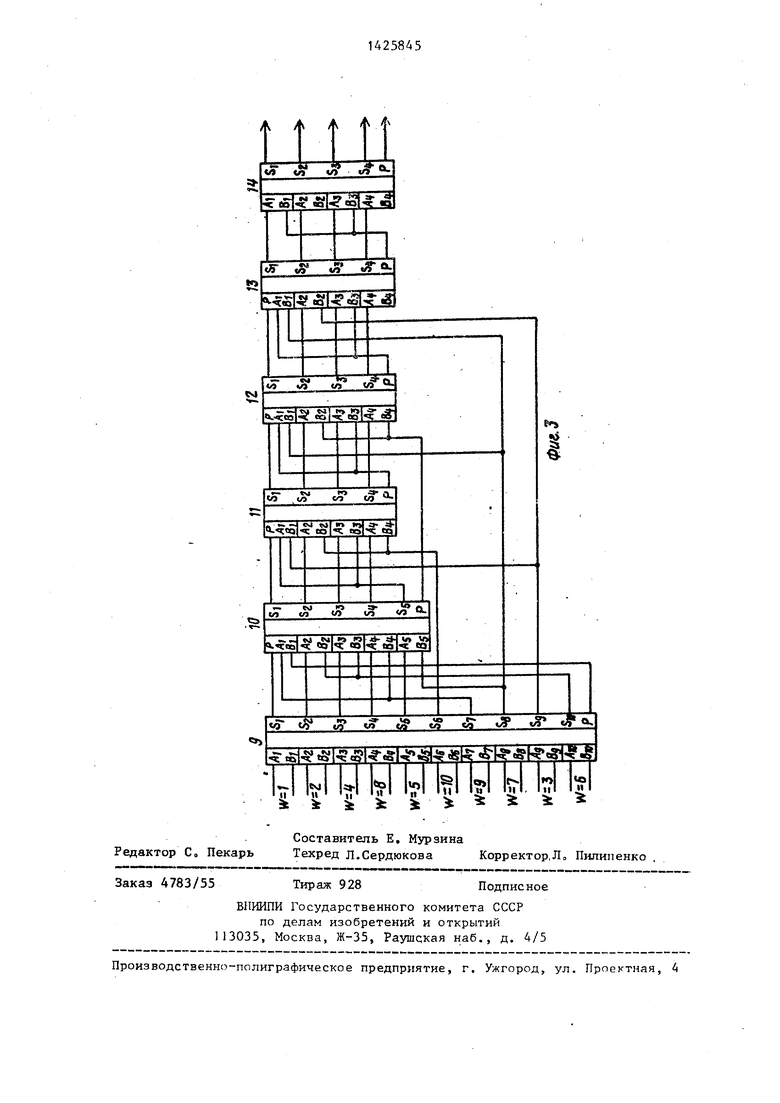

На фиг, 1 показана схема устройства дня свертки 24 разрядного двоичного кода в код по модулю К 5; на фиг;, 2 схема устройства для свертки 30-разрядного двоичного ко- да в код по модулю К 11; на фиг.З ::скема узла свертки двух г-разрядных :1содов в (llogg (К+1)+1)5 разрядный код для случая модуля , .

Устройство для свертки двоичного кода в код по модулю К содержит блок преобразования двоичного кода в два Г разрядньпс кода и блок 2 суммирова- lOM по модулю Kj, включающий узел 3 свертки двух г-разрядных кодов в

; Qlog2 |(K+1) + 1)-разрядный код и преобразователь 4 двоичного кода в код :по модулю Кэ входы 5 и выходы 6.

БЛОК 1 преобразования двоичного кода в два г разрядных кода, где

т - мощность множества значений остатков по модулю К исходного кода, содержит t ярусов сумматоров, причем сумматоры первого яруса соединены с входами устройства с весами, имеющи- одинаковые значения остатков по модулю входы сумматоров i-ro яруса (1 i t) соединены с выходами сумматоров предыдущих ярусов или выходами сумматоров предьдущих ярусов и входами устройства с весами, име ющими одинаковые значения остатков по модулю К, выходы сумматоров по- ,следнего яруса являются выходами блока соответствующего веса,

Узел 3 свертки двух г-разрядных кодов в ( jlogJ,())-paзpядный содержит сут-ьматоры двоичных чисел, соединенные последовательно, причем входы i-ro разряда первого сумматора входами узла с весом СО (2- ) modK (i 1,2, ..,, г), вь ходы последнего сумматора являются выходами узла7 выходы сумматор (J 5: 1) с W соединены с входми тех разрядов последующих сумматоров, длк которых сумма весов входов по модулю К равна, (W)raodK

Преобразователь 4 двоичного кода в код по модулю К содержит пороговый блок 7, соединенный входами с входами преобразователя, а выходом - с входами сумматора 8 с номерами, соответ- ствуюпщми номерам едиштеных разрядов двоичного представления числа

(|с4(1С ..

2 .-К, вторая, группа входов

сумматора 8 соединена с 3 ) -- входами преобразователя с весами 2 (4i 0,1, ,.., llogjCK+DC -1). Пороговый блок 7 представляет собой.пороговый элемент с весами входов 2 (i 0,1,.,., log CK+Dt ) и порогом и может иметь любую известную структуру.

На фиг. 1-3 обозначены также сумматоры 9-30.

Устройство работает следующим образом.

При подаче на входы 5 устройства двоичного кода блок I преобразует его в два г-разрядных кода, причем

(х;2 - )TnodK ( +,

i() (

/modK,

,

5

0

где x; , Уу, ,

у - значение j-ro разряда с-го

кода на выходах блока 1. Коды с выходов блока 1 преобразования двоичного кода в два г-разряд-- ных кода пост ппают на входы узла 3 свертки двух г-разрядных кодов в- Cjlogj (К+1)11+1)разрядньй блока 2 суммирования по модулю К, который формирует на своих вькодах , Qlogj ()t + 1)paзpядньй код z, при- ,чем ,

п . ,.Дни)ия ,

(ZIx;2 )modK ( 21 )modK. ,

Код с выходов узла 3 свертки по- iCTynaeT на входы преобразователя 4 двоичного кода в код по модулю К, который формирует выходной сигнал. Если на входы блока 4 поступает код Z К, то на выкоде порогового блока 7 формируется нулевой сигнал и код с входов блока 4 проходит на выходы сумматора 8 без изменений. Если на входы блока 4 поступает код z г К, то на выходе порогового блока 7 формируется единичный сигнал, поступающий на группу входов сумматора 8, при этом на выходах сумматора 8 формируется код числа Z-K, равный остатку по модулю К кода на входах блока 4

Пусть, например, единичные сигналы поданы на входы х, х, х, х,

х, 15 2- устройства для свертки двоичного кода в код по модулю К Зг изображенного на фиг, 2, Это вызывает единичные сигналы на выходах и переноса сумматоров 15, 22, выходах суммы сумматоров 16-21 и 23, выходах переноса сутчматоров 24--26, выходах суммы сумматоров 27-29 и выходе суммы и выходе переноса сумматора 30 блока 1 пре образов ния двоичного кода в два г раэрядных (). Коды с выходов блока 1 поступают на входы сумматора 9 узла 3 свертки двух г-разрядкых кодов в (. К.+ )1 + разрядный, что вызывает единичные сигналы, на его выходах s, и р, при этом единичные сигналы появляются на выходах суммы Sj сумматоров 10 и 11с Код с выходов сумматора 11 поступает на входы преобразователя 4 двоичного кода в код по модулю К, поскольку он меньше К, то единичньй сигнал с выхода Sj сумматора 11 проходит на. выход Sj сумматора 8, Прн этом на выходах 6 устройства появляется код числа 2, равный остатку по модулю 5 входного кода

Таким образом, устройство обеспечивает свертку, любого двоичного кода

в том числе и ненат; рального, в код по любому модулю к,

5 ормула изобретения

Устройство для свертки двоичного кода в код по модулю К, содержащее блок преобразования двоичного кода

в два г-разрядных кода (г - мощность множества значений остатков по модулю К исходного кода) и блок суммирования по модулю К, выходы которого являются выходами устройства, а вхо™

ды подключены к выходам блока преобразования двоичного кода в два г-раз- рядных кода, входы которого соединены с входами устройства, отличающееся тем, что, с целью расширения области применения устройства за счет возможности использования произвольного значения- К, блок суммирования по модулю К содержит узел свертки двух г-разрядных кодов в Qlog (К+1))

разрядньй код и преобразователь двоичного кода в код по модулю К, вы- ходы которого являются выходами блока суммирования по модулю К, р. входы соединены с выходами узла

свёртки двух г-разрядных кодов в

(Jlogj(K+1)C +1)-разрядный код, вхо- ды которого являются входами блока суммирования МО модулю К,

-5

Фиг.1

11Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код по модулю К | 1989 |

|

SU1732472A1 |

| Преобразователь двоичного кода | 1986 |

|

SU1476614A1 |

| Устройство для преобразования количества единиц двоичного кода в код по модулю К | 1987 |

|

SU1527714A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ K | 1991 |

|

RU2020760C1 |

| Устройство для умножения по модулю К | 1989 |

|

SU1691834A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691844A1 |

| Устройство для контроля параллельного двоичного кода по модулю К | 1986 |

|

SU1425676A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771659A1 |

| Преобразователь двоичного кода в код по модулю | 1980 |

|

SU902013A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении систем передачи и переработки дискретной информации. Цель изобретения - расширение области применения устройства за счет возможности получения произвольного значения модуля К. Устройство содержит блок 1 преобразования двоичного кода в два г-разряд ных кода и блок 2 суммирования по моду- лю К, содержащий узел 3 свертки двух г-разрядных кодов в (jlog (К+1) + 1)- .разрядньй код и преобразователь двоичного кода в код по модулю К, входы 5 и выходы 6. 3 ил.

.«

.

«S .g .

Сч|

-iii Ы ,

«/ t/a M

. .gl

L

.r- «y-

to сУ со oj

IH -H «il i)l a- 1 | -4tp|- оэК

t- eo V a

.

I

v

Г «si-g tSf dsfe г

|уууы1|11|1 1,||1

tn

« t

д- y g

| Устройство для подсчета числа двоичных единиц | 1980 |

|

SU966700A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| - Журавлев Ю.П | |||

| и др | |||

| Надежность и контроль ЭВМ | |||

| - М.гСоветское радио, ,1978, Со 113-114, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-23—Публикация

1986-06-12—Подача