11

СЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Преобразователь двоичного кода в код по модулю К | 1989 |

|

SU1732472A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1569996A1 |

Изобретение относится к автоматике и вычислительной технике. Использование его в системах передачи и обработки дискретной информации позволяет повысить надежность устройства, которое содержит блок 2 весового суммирования, сумматор 3 и пороговый блок 5. Благодаря введению многоканального преобразователя 1 параллельного кода в последовательности импульсов, сумматора 4, блока 6 формирования вычетов и запоминающего блока 7 исключается блок свертки числа разрядов прототипа и упрощается блок весового суммирования. 2 ил.

:л ю

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи и обработки дискретной информа- дни.

Цель изобретения - новышение на- дежности устройства.

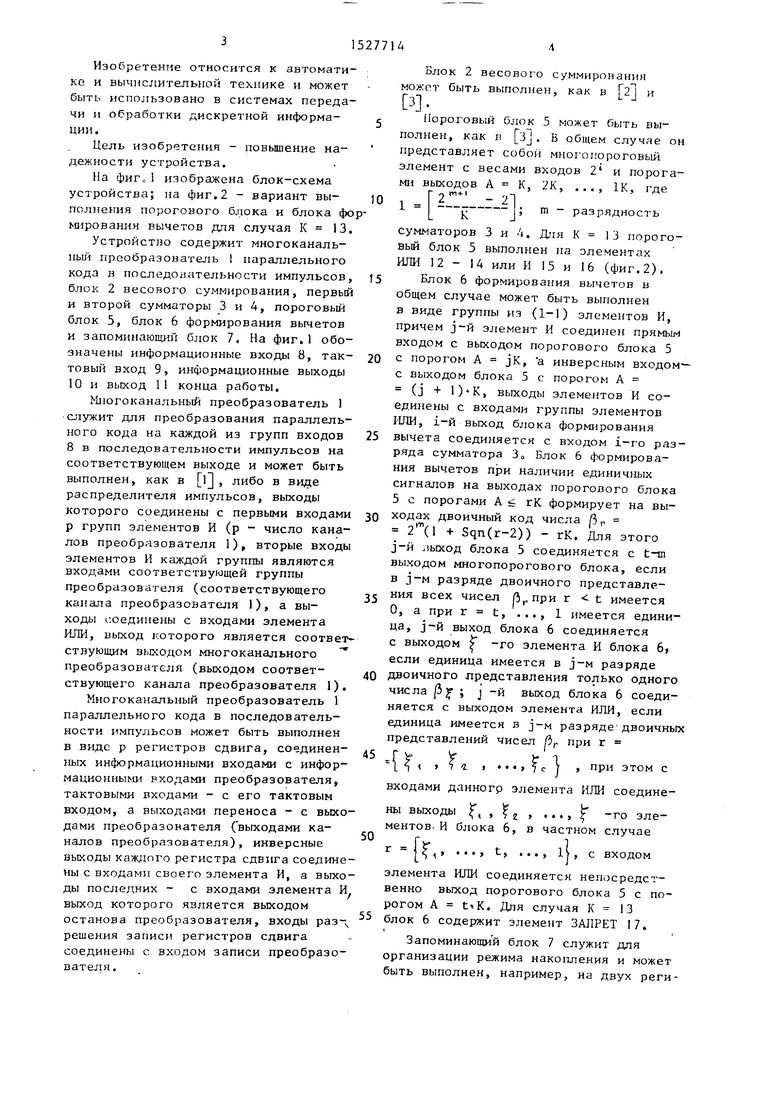

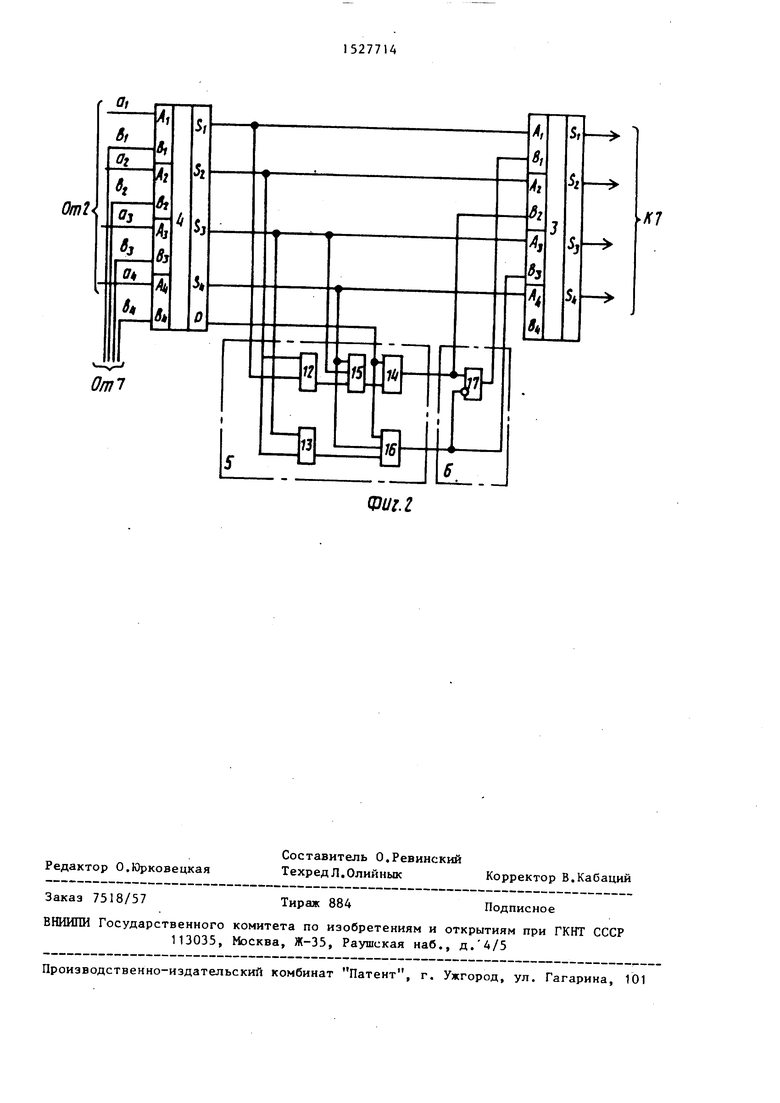

На фиг о I изображена блок-схема устройства; на фиг.2 - вариант вы- полнения порогового блока и блока фомирования вычетов для случая К 13.

Устройство содержит многоканаль- ньш преобразователь 1 параллельного кода в иоследолательности импульсов, блок 2 весового суммирования, первый и второй сумматоры 3 и 4, пороговый блок 5, блок 6 формирования вычетов и запоминающий блок 7. На фиг.1 обозначены информационные входы 8, так- товый вход 9, информационные выходы 10 и выход 11 конца работы.

Многоканальный преобразователь 1 служит для преобразования параллельного кода на каждой из групп входов 8 в последовательности импульсов на соответствующем выходе и может быть выполнен, как в ij либо в виде распределителя импульсов, выходы которого соединены с первыми входами р групп элементов И (р - число каналов преобразователя 1), вторые входы элементов И каждой группы являются входами соответствующей группы преобразователя (соответствующего канала преобразователя 1), а выходы соединены с входами элемента ИЛИ, выход jroTOporo является соответствующим выходом многоканального преобразователя (выходом соответ- ствующего канала преобразователя 1).

Многоканальный преобразователь 1 параллельного кода в последовательности импульсов может быть выполнен в виде р регистров сдвига, соединен- ных информационными входами с информационными входами преобразователя, тактовыми входами - с его тактовым входом, а выходами переноса - с выходами преобразователя ( выходами ка- налов преобразователя), инверсные выходы каждого регистра сдвига соединены с входами своего элемента И, а выходы последних - с входами элемента И выход которого является выходом останова преобразователя, входы разрешения записи регистров сдвига соединены с входом записи преобразователи .

г

5 0

5 О Q

5

БЛОК 2 весового суммирования может быть выполнен, как в Г21 и

Пороговый блок 5 может быть выполнен, как в 3J . В общем случае он представляет собой многогюроговый элемент с весами входов 2 и порогами выходов А К, 2К, ..., 1К, где

г 2-- 2-1 -1- - г:; m - разрядность

сумматоров 3 и 4. Для К 13 пороговый блок 5 выполнен на элементах ИЛИ 12 - 14 или И 15 и 16 (фиг.2).

Блок 6 формирования вычетов в общем случае может быть выполнен в виде группы из (1-1) элементов И, причем j-й элемент И соединен прямым входом с выходом порогового блока 5 с порогом А JK, а инверсным входом- с выходом блока 5 с порогом А (J + 1)К выходы элементов И соединены с входами группы элементов ИЛИ, i-й выход блока формирования вычета соединяется с входом i-ro разряда сумматора 3 Блок 6 формирования вычетов при наличии единичных сигналов на выходах порогового блока 5 с порогами А ё гК формирует на выходах двоичный код числа р г (1 + Sqn(r-2)) - гК. Для этого j-й лыход блока 5 соединяется с t-m выходом многопорогового блока, если в J-M разряде двоичного представления всех чисел г t имеется О, а при г t, ..., 1 имеется единица, j-й выход блока 6 соединяется с выходом -го элемента И блока 6, если единица имеется в J-M разряде двоичного лредставления только одного числа Р ; J й выход блока 6 соединяется с выходом элемента ИЛИ, если единица имеется в J-M разряде двоичных представлений чисел р при г

1 а fc j , при этом с входами данногр элемента ИЛИ соединены выходы , , Z , ..., -го элементов, и блока 6, в частном случае

г 1, ..., tК, с входом

элемента ИЛИ соединяется непосредственно выход порогового блока 5 с порогом А . Для случая К 13 блок 6 содержит элемент ЗАПРЕТ 17.

Запоминающий блок 7 служит для организации режима накопления и может быть выполнен, например, на двух реги51

страх памяти, причем информационные входы блока 7 соединены с информационными входами первого регистра памяти, информационные выходы которого соединены с информационными входами второго регистра памяти, выходами которого являются выходы блока 7, вход разрешения записи первого регистра памяти, являющийся тактовым вхо- дом блока, соединен с входом инвертора, выход которого соединен С входом разрешения записи второго регист памяти. Блок 7 может быть выполнен и на одном регистре памяти, информац онные входы которого являются входам блока 7, а выходы являются выходами блока 7, Вход разрешения записи регистра через элемент задержки соединен с тактовым входом блока 7, при этом вход разрешения записи регистра памяти выполнен импульсным. Устройство работает следующим

.образомо

В исходном состоянии многоканаль- ный преобразователь 1 параллельного кода в последовательности импульсов и запоминающий блок 7 сброшены. Входной код подан иа входы 8. Если многоканальный преобразователь 1 вьшолнен на регистрах сдвига, то входной код записан в них.

На тактовый вход 9 устройства подаются тактовые импульсы. При этом многоканальный преобразователь 1 преобразует количество единичных сигналов на информационных входах 8 в соответствующее число импульсов на i-M выходе (выходе i-ro канала преобразователя 1). Импульсы с выходов многоканального преобразователя 1 на каждом такте (синхронно с тактовыми импульсами) поступают на входы блока 2, который формирует на своих выходах двоичньш код их числа (по модулю К), поступающий на.входы сумматора А, к содержимому которого при этом прибавляется значение остатка по модулю К кода на выходах блока 2. Блоки 5 и 6

и сумматор 3 служат для полной свертки кода по модулю К. Работа продолжается таким образом до окончания преобразо-. вания входного кода преобразователем 1, при этом он самоблокируется и далее импульсов на своих информационных выходах не формирует, на его выходе останова появляется единичньй сигнал.

46

поступающий на выход 11 конца работы устройства, свидетельствуя об окончании цикла работы. Результат снимается с выходов 10.

В устройстве оптимизации разрядности кода на выходах блока подсчета единиц осуществляется выбором каналь- ности преобразователя параллельного кода в последовательности импульсов, что позволяет исключить полностью блок свертки числа разрядов кода и упростить блок весового суммирования.

Формула изобретения

д 0

5 о

,

5

0

5

Устройство для преобразования ко- jin4ecTBa единиц двоичного кода в код по модулю К, содержащее блок весового суммирования, пороговьо блок, входы которого объединены с соответствующими парными входами первого сумматора, отличающееся тем, что, с целью повышения надежности устройства, Б него введены второй сумматор, блок формирования вычетов, запоминающий блок и многоканальный преобразователь параллельного кода в последовательное- ти импульсов, информационные входы которого являются одноименными входами устройства, а тактовый вход объединен с тактовь:м входом запоминающего блока и является тактовым входом устройства, информационные выходы многоканального преобразователя параллельного кода в последовательности импульсов соединены с соответствующими входами блока весового суммирования, выходы которого подключены к первым входам второго сумматора, выходы которого соединены с соответствующими входами порогового блока, выходы которого подключены к соответствующим входам блока формирования вычетов, выходы которого соединены с соответствующими вторыми входами первого сумматора, выходы первого сумматора подключены к информационным входам запоминающего блока, выходы которого соединены с соответствующими вторыми входами второго сумматора и являются информационными выходами устройства, выход окончания работы многоканального преобразователя паралле-льного кода в последовательности импульсов является выходом конца работы устройства.

Omt

Редактор О.Юрковецкая

Составитель О.Ревинский Техред Л.Олийнык

Заказ 7518/57

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

К7

Фип

Корректор В.Кабаций

Подписное

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сер.; Общие вопросы радиоэлектроники, 198, № 12, с | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-07—Публикация

1987-12-08—Подача