О Од 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383494A1 |

| Вычитающий декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383492A1 |

| Синхронный делитель частоты на 10 | 1985 |

|

SU1338061A1 |

| Синхронный делитель частоты на 47 | 1990 |

|

SU1714806A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| Счетчик импульсов для семисегментных индикаторов | 1988 |

|

SU1580550A1 |

| Синхронный делитель частоты на 9 | 1986 |

|

SU1378055A1 |

| Делитель частоты на 10 | 1986 |

|

SU1403364A1 |

| Синхронный делитель частоты | 1986 |

|

SU1406785A1 |

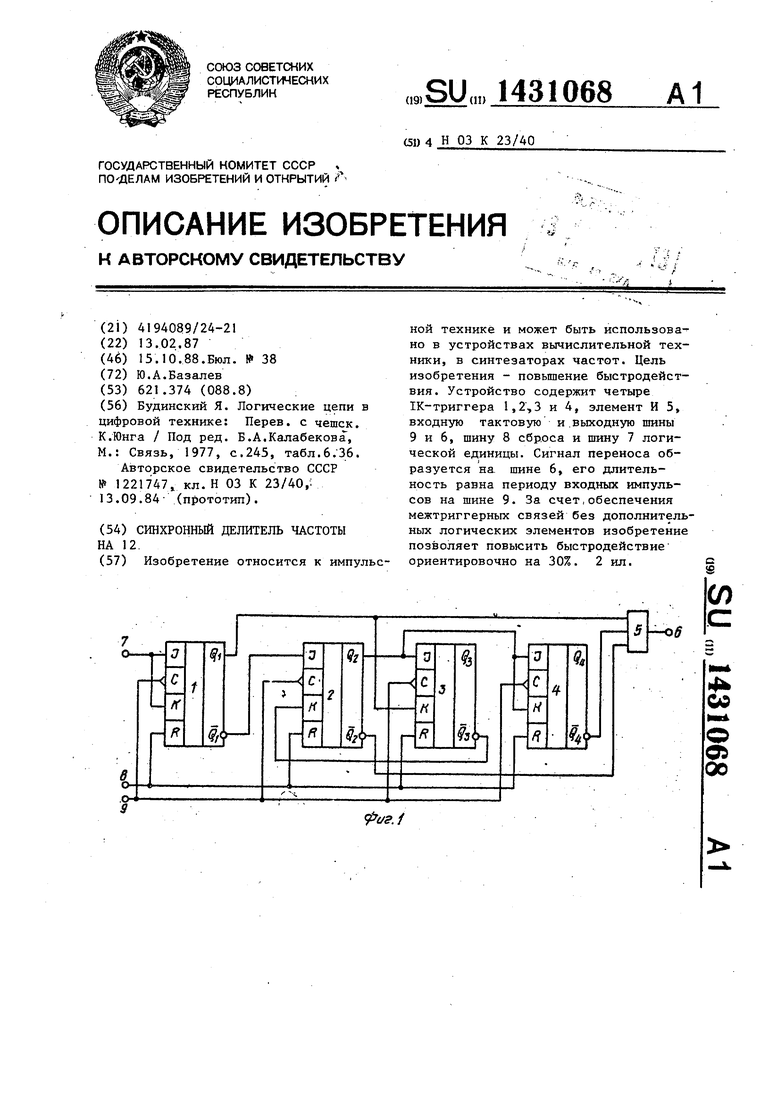

Изобретение относится к импульсной технике и может быть использова- но в устройствах вычислительной техники, в синтезаторах частот. Цель изобретения - повышение быстродействия. Устройство содержит четыре 1К-триггера 1,2,3 и 4, элемент И 5, входную тактовую и.выходную шины 9 и 6, шину 8 сброса и шину 7 логической единицы. Сигнал переноса образуется на. шине 6, его длительность равна периоду входных импульсов на шине 9. За счет,обеспечения межтриггерных связей без дополнительных логических элементов изобретение позволяет повысить быстродействие ориентировочно на 30%. 2 ил. с е

.1

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники, в синтезаторах частот.

Цель изобретения - повышение быстродействия (ориентировочно на за счет обеспечения межтриггерных связей без дополнительных логических элементов.

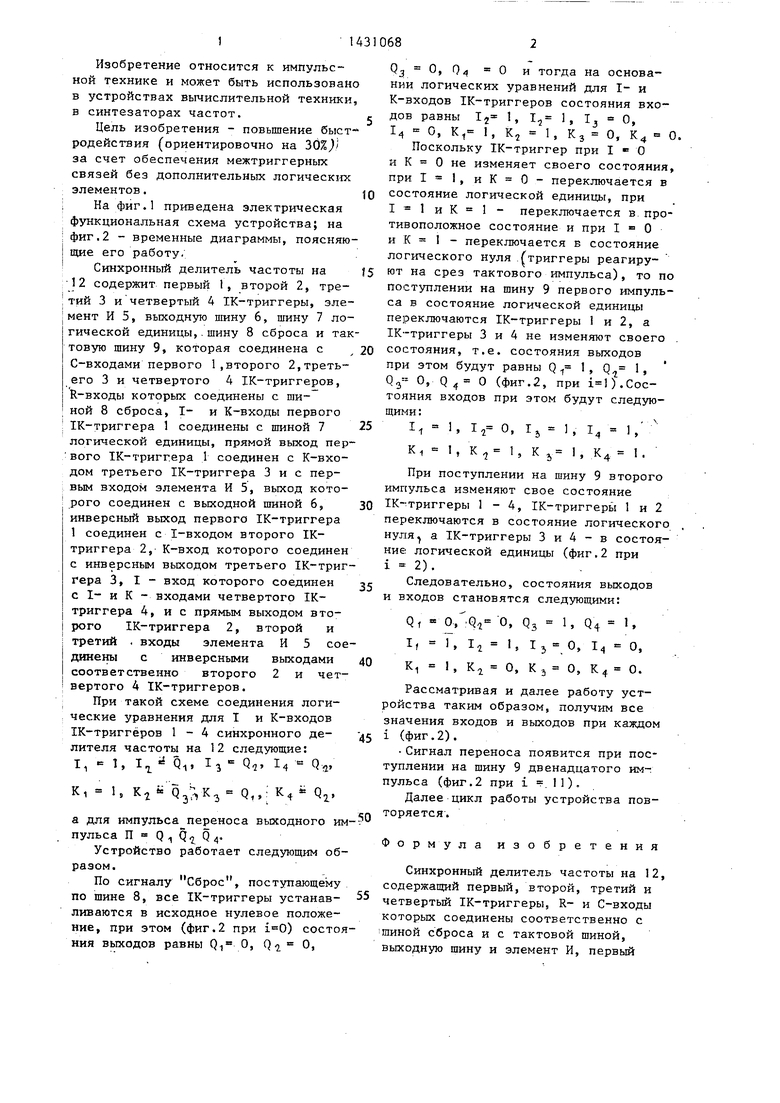

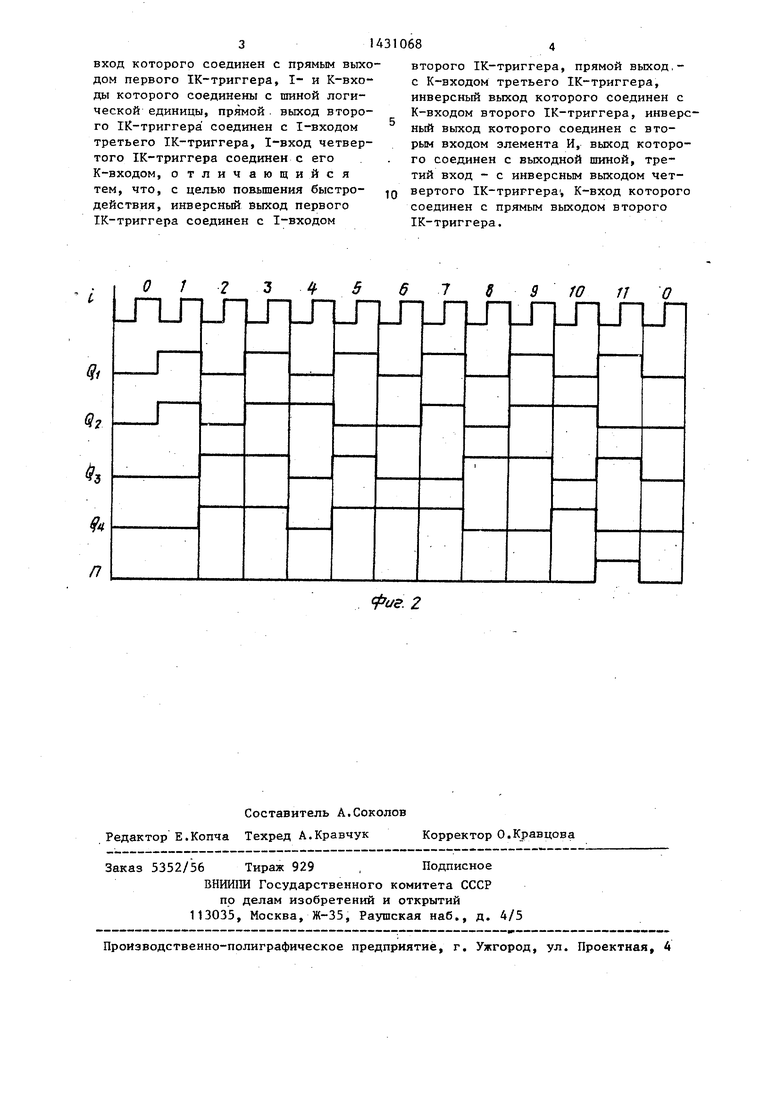

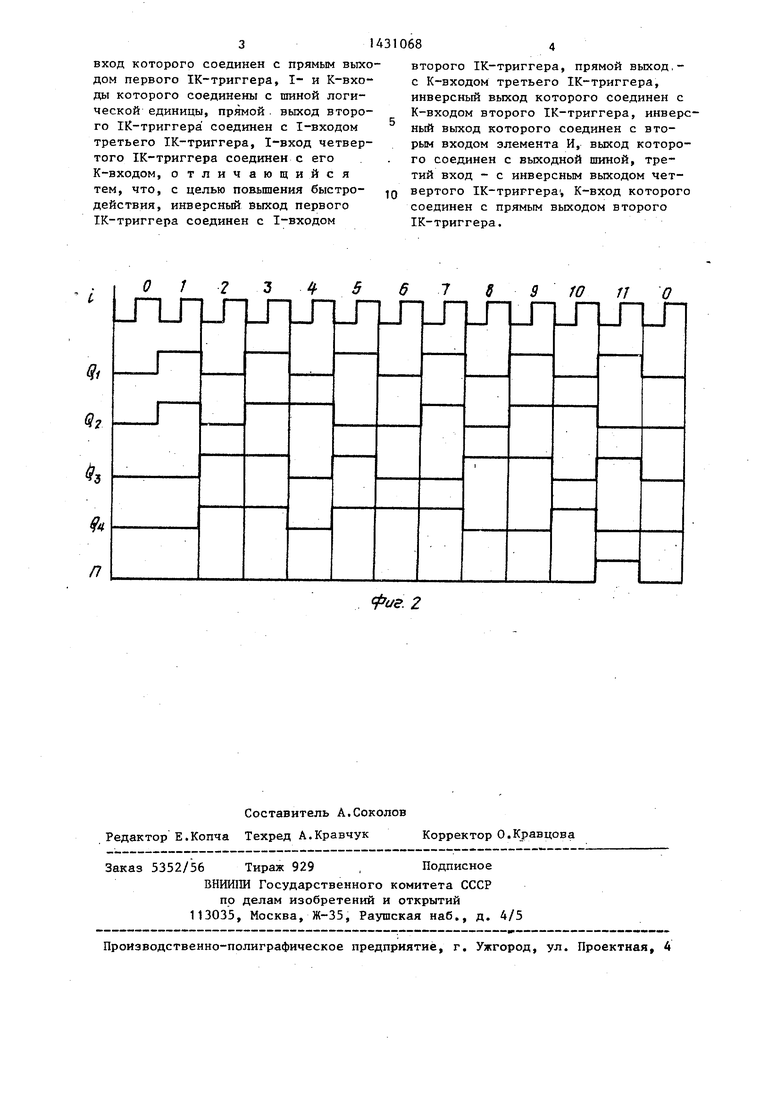

; На фиг.1 приведена электрическая функциональная схема устройства; на ; фиг.2 - временные диаграммы, поясняю- 1 щие его работу.;

Синхронный делитель частоты на 12 содержит первый I, второй 2, тре- :тий 3 и четвертый 4 1К-триггеры, эле- :мент И 5, выходную шину 6, шину 7 ло- iгической единицы,.шину 8 сброса и так Ютовую шину 9, которая соединена с С-входами первого 1.второго 2,третьего 3 и четвертого 4 1К-триггеров, I R-входы которых соединены с ши- I ной 8 сброса, I- и К-входы первого : 1К-триггера 1 соединены с шиной 7 логической единицы, прямой выход пер- вого 1К-тригг.ера 1 соединен с К-вхо дом третьего 1К-триггера 3 и с пер- ; вым входом элемента И 5, выход кото- : рого соединен с выходной шиной 6, I инверсный выход первого 1К-триггера 1 соединен с 1-входом второго IK- триггера 2, К-вход которого соединен с инверсным выходом третьего 1К-триг- гера 3, I - вход которого соединен с I- и К - входами четвертого IK- триггера 4, и с прямым выходом второго 1К-триггера 2, второй и третий . входы элемента И 5 соединены с инверсными выходами соответственно второго 2 и чет- вертого Д 1К-триггеров.

При такой схеме соединения логи- : ческие уравнения для I и К-входов 1К-триггёров 1 - 4 синхронного де- лителя частоты на 12 следующие:

Т, - 1, 1 Qi, 1э Q. 14 Qft к, - 1, к Q,,; Q,

а для импульса переноса выходного им пульса .

Устройство работает следующим образом.

По сигналу Сброс, поступающему по шине 8, все 1К-триггеры устанав- ливаются в исходное нулевое положение, при этом (фиг.2 при ) состояния выходов равны Q О, Q . О,

Qj О, 0 0 и тогда на основании логических уравнений для I- и К-входов 1К-триггеров состояния входов равны 12 1, 1-2 1, Ij О, 1 О, К, 1, Kj 1, Кз О, К4

Поскольку 1К-триггер при I О и К О не изменяет своего состояния при I 1, и к о - переключается в состояние логической единицы, при I 1 и К I - переключается в, противоположное состояние и при I О и К 1 - переключается в состояние логического нуля (триггеры реагируют на срез тактового импульса), то п поступлении на шину 9 первого импульса в состояние логической единицы переключаются 1К-триггеры i и 2, а 1К-триггеры 3 и 4 не изменяют своего состояния, т.е. состояния выходов при этом будут равны Q 1, Q 1, QS О Q 4 ° о (фиг.2, при ).Состояния входов при этом будут следующими :

1 1, 1 О, Ij 1, 1/ 1,

Ki 1, К, 1, К j 1, К .

При поступлении на шину 9 второго импульса изменяют свое состояние ТК-триггеры 1-4, 1К-триггерь1 1 и 2 переключаются в состояние логическог нуля а 1К-триггеры 3 и 4 - в состояние логической единицы (фиг,2 при i 2).

Следовательно, состояния выходов и входов становятся следующими:

Qf 0, :Q О, РЗ 1, Q4 Ь I, 1, 1 1, IJ О, 1 О, К, I, К. О, К J О, К4 О.

Рассматривая и далее работу устройства таким образом, получим все значения входов и выходов при каждом i (фиг.2).

Сигнал переноса появится при поступлении на шину 9 двенадцатого импульса (фиг.2 при i . 11).

Далее цикл работы устройства повторяется.

Формула изобретения

Синхронный делитель частоты на 12 содержащий первый, второй, третий и четвертьй ТК-триггеры, R- и С-входы которых соединены соответственно с шиной сброса и с тактовой шиной, выходную шину и элемент И, первый

вход которого соединен с прямым выходом первого 1К-триггера, I- и К-вхо- ды которого соединены с шиной логической единицы, пр51мой . выход второго 1К-триггера соединен с 1-входом третьего 1К-триггера, 1-вход четвертого 1К-триггера соединен с его К-входом, отличающийся тем, что, с целью повышения быстродействия, инверсный выход первого 1К-триггера соединен с 1-входом

1

Q з

4

п

второго 1К-триггера, прямой выход,- с К-входом третьего 1К-триггера, инверсный выход которого соединен с К-входом второго 1К-триггера, инверсный выход которого соединен с вторым входом элемента И, выход которого соединен с выходной шиной, третий вход - с инверсным выходом четвертого 1К-триггера , К-вход которого соединен с прямым выходом второго 1К-триггера.

фиг. 2

| Будинский Я | |||

| Логические цепи в цифровой технике: Перев | |||

| с чешек | |||

| К.Юнга / Под ред | |||

| Б.А.Калабекова, М.: Связь, 1977, с.245, табл.6.36 | |||

| Синхронный делитель частоты на 12 | 1984 |

|

SU1221747A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-15—Публикация

1987-02-13—Подача