(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты | 1986 |

|

SU1406787A1 |

| Синхронный делитель частоты | 1986 |

|

SU1374425A1 |

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383494A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1330757A1 |

| Синхронный делитель частоты | 1986 |

|

SU1354415A1 |

| Синхронный делитель частоты на 9 | 1986 |

|

SU1378055A1 |

| Счетчик импульсов для семисегментных индикаторов | 1988 |

|

SU1580550A1 |

| Синхронный делитель частоты | 1986 |

|

SU1322470A1 |

| Синхронный делитель частоты на 47 | 1990 |

|

SU1714806A1 |

| Синхронный делитель частоты на 12 | 1987 |

|

SU1431068A1 |

Изобретение может быть использовано в цифровых синтезаторах частоты. Делитель частоты на 10 содержит эле- мент И 5, выходную шину 6, IК-тригге- ры 1-4, входную шину 7 и шину 8 сброса. Введение новых электрических свя зей между функциональными элементами повьш1ает надежность функционирования делителя частоты на 10 и расширяет длительность выходного импульса. 2ил.

со

00

CfJuS.i

Изобретение относится к импульсно технике и может быть использовано в Цифровых синтезаторах частоты.

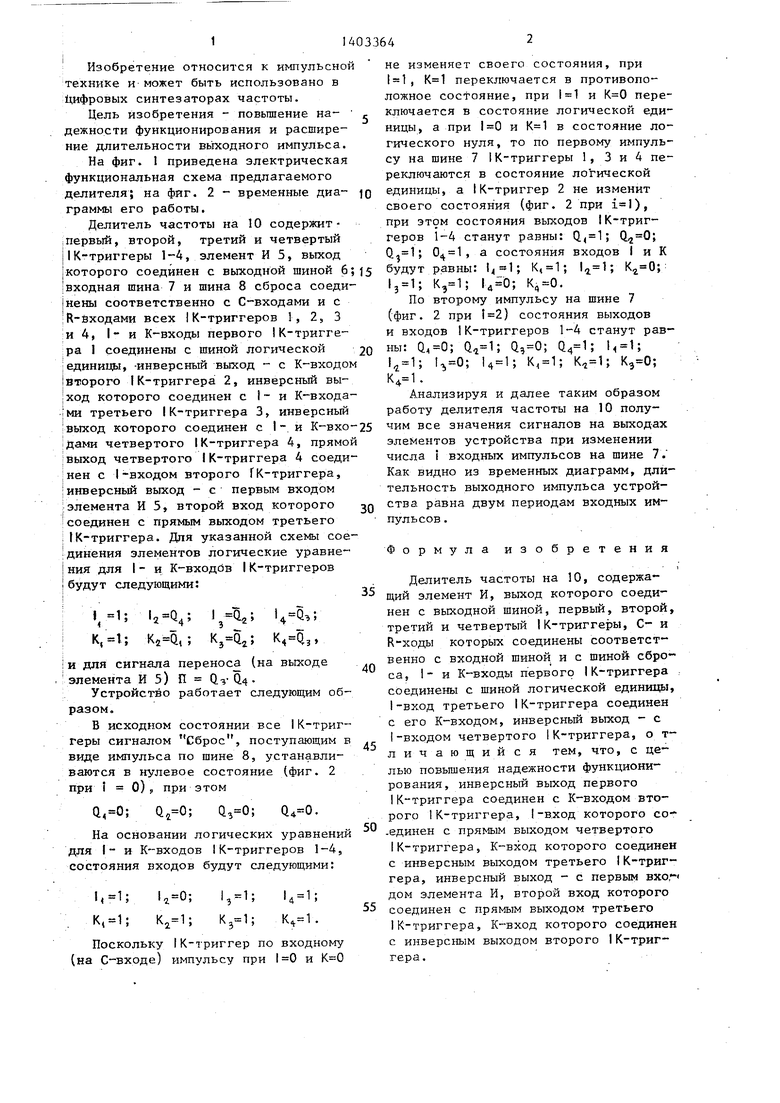

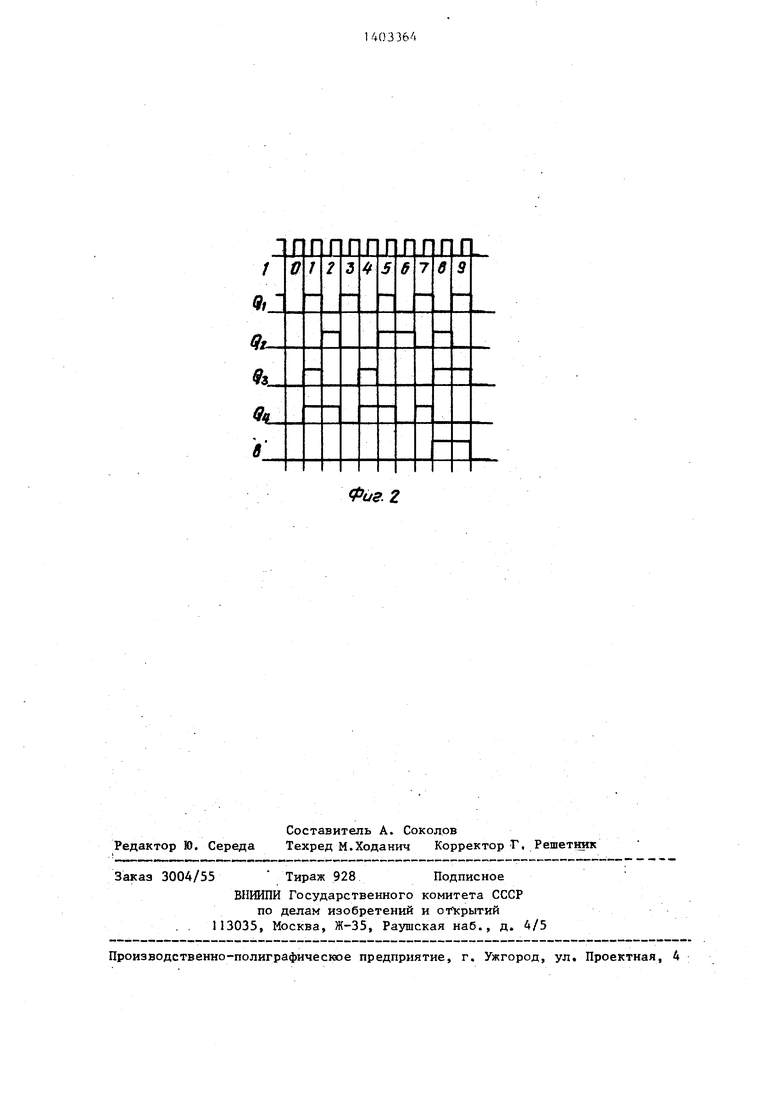

Цель изобретения - повьшение на- дежности функционирования и расширение длительности вь гходного импульса. На фиг. 1 приведена электрическая функциональная схема предлагаемого делителя; на фйг. 2 - временные диа- граммы его работы.

Делитель частоты на 10 содержит- iпервый, второй, третий и четвертый jlK-триггеры 1-4, элемент И 5, выход которого соединен с выходной шиной 6 Iвходная шина 7 и шина 8 сброса соединены соответственно с С-входами и с ;К-входами всех IК-триггеров 1, 2, 3 ;И 4, 1-й К-входы первого 1К-тригге- ра 1 соединены с шиной логической |единищ, -инверсный выход - с К-входо второго IК-триггера 2, инверсный вы- |ход которого соединен с 1 и К-входа {ми третьего IК-триггера 3, инверсный 1выход которого соединен с I-. и К-вхо :Дами четвертого IК-триггера 4, прямо (выход четвертого IК-триггера 4 соеди ;нен с 1-входом второго ГК-триггера, I инверсный выход - с первым входом Jэлемента И 5, второй вход которого соединен с прямым выходом третьего I1К-триггера. Для указанной схемы сое |динения элементов логические уравне- Iния для I - и К-входов IК-триггеров I будут следующими:

; ,; ,; I K,t; , ; K,Q,,; 0,,,

I и для сигнала переноса (на выходе

элемента И 5) П (1э- 4Устройстао работает следующим образом.

В исходном состоянии все IК-триг- геры сигналом Сброс, поступающим в виде импульса по шине 8, устанавливаются в нулевое состояние (фиг. 2 при i 0)J при этом

а,0; Q; .

На основании логических уравнений для I- и К-входов IК-триггеров 1-4, состояния входов будут следующими:

1,1; 1,1; Kj-ij К I j .

Поскольку 1К-триггер по входному (на С-входе) импульсу при и

, Q

i5 0 5 0

.

.j-

50

5

не изменяет своего состояния, при , переключается в противоположное состояние, при и переключается в состояние логической единицы, а при и в состояние логического нуля, то по первому импульсу на шине 7 1К-триггеры 1, 3 и 4 переключаются в состояние логической единицы, а IК-триггер 2 не изменит своего состояния (фиг. 2 при ), при этом состояния выходов IК-триггеров 1-4 станут равны: (14 1; 0.1; 0 1, а состояния входов I и К будут равны: К, 1; (.Q; 1з и К, 1; К,-0.

По второму импульсу на шине 7 (фиг. 2 при ) состояния выходов и входов К-триггеров 1-4 станут равны: Q,0; 0.}; 1 1; 14 1; К, 1; .

Анализируя и далее таким образом работу делителя частоты на 10 получим все значения сигналов на выходах элементов устройства при изменении числа i входных импульсов на шине 7. Как видно из временных диаграмм, длительность выходного импульса устройства равна двум периодам входных импульсов.

Формула изобретения

Делитель частоты на 10, содержащий элемент И, выход которого соединен с выходной шиной, первый, второй, третий и четвертый 1К-триггеры, С- и которых соединены соответственно с входной шиной и с шиной сбро са, 1- и К-входы первого IК-триггера , соединены с шиной логической единицы, I-вход третьего IК-триггера соединен с его К-входом, инверсный выход - с I-входом четвертого IК-триггера, о т- личающийся тем, что, с целью пoвьшJeния надежности функционирования, инверсный выход первого 1К-триггера соединен с К-входом второго 1 К-триггера, I-вход которого со- -единен с прямым выходом четвертого К-триггера, К-вход которого соединен с инверсным выходом третьего IК-триггера, инверсный выход - с первым вхог дом элемента И, второй вход которого соединен с прямым выходом третьего 1К-триггера, К-вход которого соединен с инверсным выходом второго IК-триггера.

Фи5. 2

| Справочник по интегральным микросхемам | |||

| Под ред | |||

| Б.В | |||

| Тарабрина | |||

| М.: Энергия, 1980, с | |||

| Приспособление для укладки спичечных или т.п. коробок рядами | 1925 |

|

SU699A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Синхронный делитель частоты на 10 | 1985 |

|

SU1338061A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-15—Публикация

1986-11-10—Подача