сл

с

Изобретение относится к цифровой технике и может быть использовано, например, при построении хронизаторов, цифровых синтезаторов частоты, электромузыкальных инструментов.

Известен делитель частоты на 47, построенный по безвентильной схеме, который содержит девять триггеров 1.

Недостатками данного делителя являются сложность схемы, низкая надежность и стабильность из-за большого количества элементов, а также медленная скорость работы, так как он является асинхронным.

Наиболее близким к предлагаемому по технической сущности является синхронный делитель частоты, содержащий первый, второй, третий, четвертый, пятый и шестой К-триггеры, С- и R-входы которых соединены соответственно с входной шиной и шиной сброса, первый и второй элементы И, выходы которых соединены соответственно с - и К-входами четвертого 1К-триггера, третий элемент И, выход которого соединен с К-входом пятого 1К-триггера, первый вход с прямым выходом первого К-триггера, вход которого соединен с прямым выходом второго 1К-триггера, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый элементы И, инверсный выход шестого Ктриггера соединен с первым входом четвертого элемента И, выход которого соединен с 1-входом пятого 1К-триггера, второй входс вторым входом третьего элемента И, с первым входом первого элемента И, с первым входом пятого элемента И, с инверсным выходом третьего 1К-триггера и с первым входом шестого элемента И, выход которого соединен с первым входом седьмого элемента И, выход которого подключен к 1-входу второго К-триггера и с первым входом второго элемента И, второй вход которого соединен с прямым выходом третьего 1К-триггера и с первыМ входом восьмого элемента И, выход которого соединен с К-входом второго 1К-триггера, второй вход - с прямым выходом первого 1К-триггера, с первыми входами девятого и десятого элементов И, с вторым входом пятого элемента И, выход которого соединен с I- и К-входами шестого К-триггера, третий вход-с инверсным выходом пятого 1К-триггера, прямой выход которого соединен с вторым входом первого элемента И, четвертый вход - с третьими входами третьего и четвертого элементов И и с инверсным выходом четвертого 1К-триггера, прямой выход которого соединен с вторым входом седьмого элемента И и с вторым входом девятого элемента И, выход которого соединен с 1-входом третьего 1К-триггера, К-8код

которого соединен с выходом десятого элемента И, второй вход которого соединен с вторым 8ХОДОР.1 шестого элемента И и с инверсным выходом второго 1К-триггера 2.

Недостатком данного делителя явпяетС5 низкая надежность ы устойчивость работы из-за сложности схемы.

Целью изобретения является повышение надежности и устойчивости работы делителя за счет упрощения схемы.

Поставленная цель достигается тем, что в делитель частоты, содержащий первый, второй, третий, четвертый, пятый, шестой 1К-триггеры, С- и R-входы которых соединены соответственно с входной шиной и шиной сброса, первый, второй элементы И, выходь которых соединены с К-входами соответственно шестого и пятого 1К-триггероа, а первые входы - с прямым выходом

первого 1К-триггера, третий элемент И, выход которого соединен с i-входом четвертого 1К-триггера, выход первого элемента И соединен с 1-входом шестого 1К-триггера, выходы которого являются выходными шинами устройства, введены первый и второй элементы ИЛИ, выходы которых соединены с К-входами соответственно третьего и второго К-триггеров, прямой выход третьего 1К-триггера соединен с первым входом второго элемента ИЛИ и i-входом первого 1Ктриггера и вторым входом второго элемента И Л И, а К-вход-с инверсным выходом третьего 1К-триггера, i-вход которого соединен с прямым выходом второго 1К-триггера и первым входом первого элемента ИЛИ, второй, третий и четвертый входы которого соединены с инверсными выходами соответственно шестого, пятого и четвертого 1К-триггеров, К-вход четвертого К-триггера соединен с

выходом третьего элемента И, первый вход которого соединен с прямым выходом первого 1К-триггера, а второй - с инверсным выходом второго 1К-триггера и вторыми входами пераого и второго элементов И, прямой выход пятого К-триггера соединен с третьим входом первого элемента И, четвертый вход которого соединен с прямым выходом четвертого 1К-триггера и третьим входом второго элемента И, выход которого

соединен с 1-входом пятого 1К-триггера.

При такой схеме соединения логические уравнения для - и К-входов Escex триггеров будут следующими;

И Оз; t2 t-Qi; 1з Q2; А ts Qi Q2Q4; Ki Оз; K2 6i453; Кл K In.Ks le.

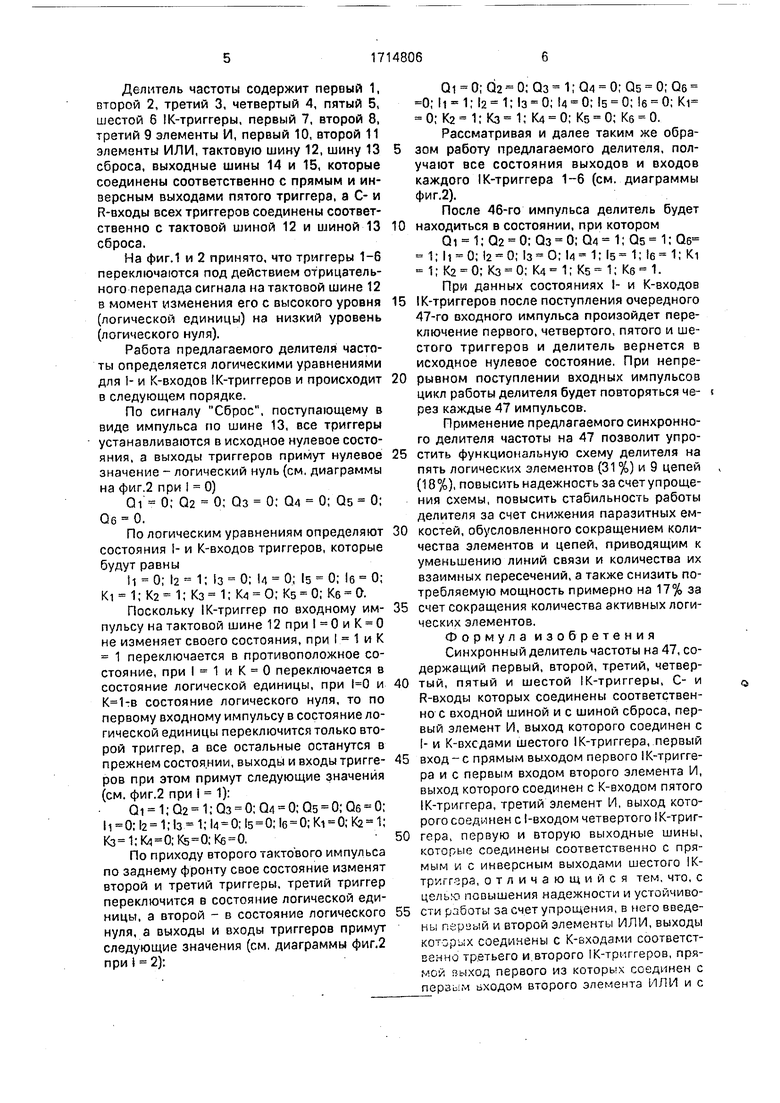

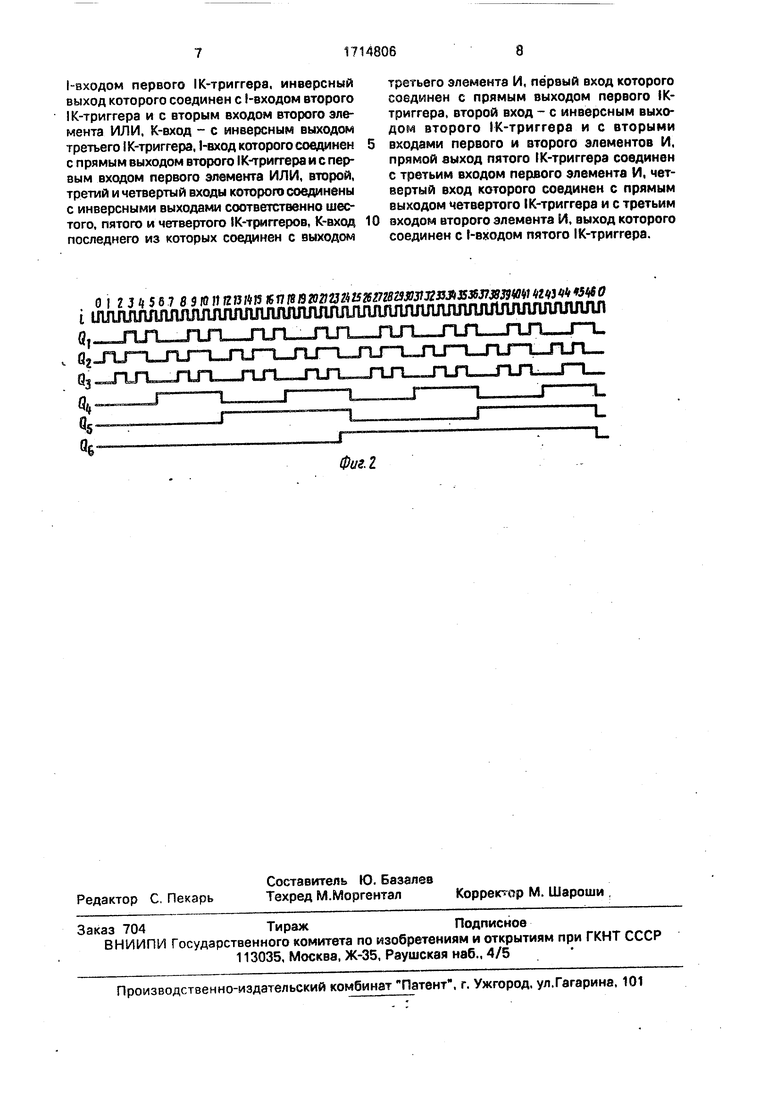

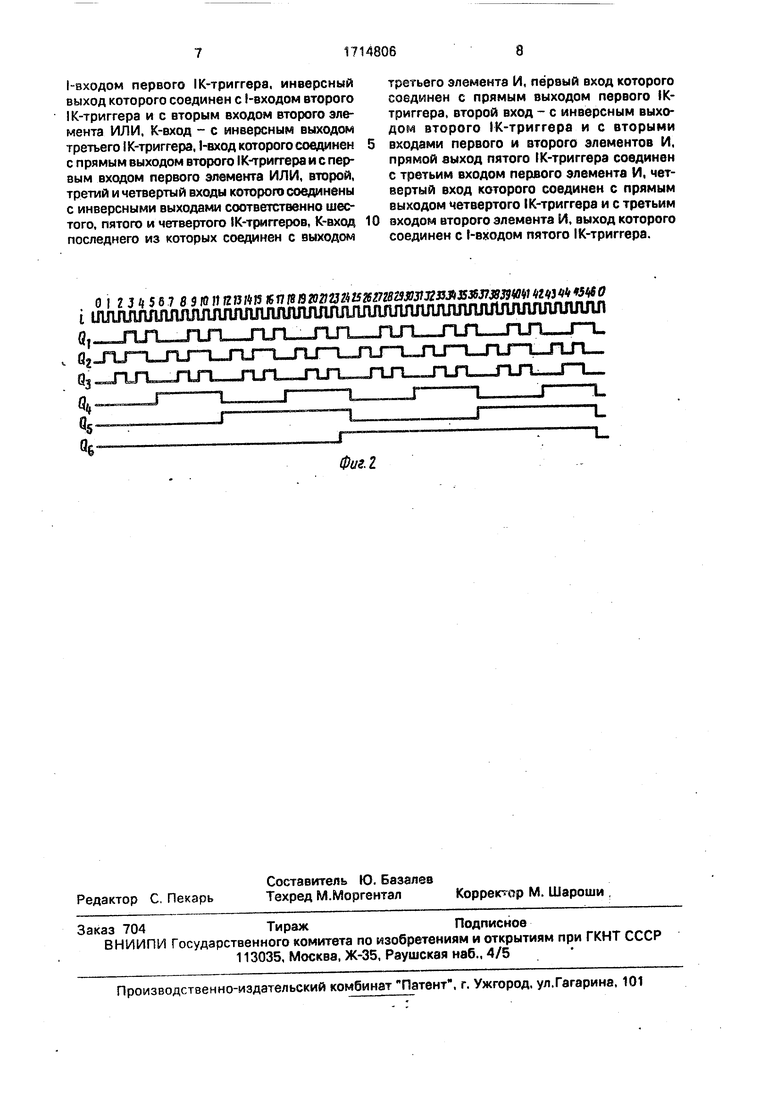

Ha фиг.1 представлена схема предлагаемого делителя частоты: на фиг.2 - диаграмма его работы,

Делитель частоты содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5, шестой 6 1К-триггеры, первый 7, второй 8, третий 9 элементы И, первый 10, второй 11 элементы ИЛИ, тактовую шину 12, шину 13 сброса, выходные шины 14 и 15, которые соединены соответственно с прямым и инверсным выходами пятого триггера, а С- и R-входы всех триггеров соединены соответственно с тактовой шиной 12 и шиной 13 сброса.

На фиг.1 и 2 принято, что триггеры 1-6 переключаются под действием отрицательного перепада сигнала на тактовой шине 12 в момент изменения его с высокого уровня (логической единицы) на низкий уровень (логического нуля).

Работа предлагаемого делителя частоты определяется логическими уравнениями для 1- и К-входов 1К-триггеров и происходит в следующем порядке.

По сигналу Сброс, поступающему в виде импульса по шине 13, все триггеры устанавливаются в исходное нулевое состояния, а выходы триггеров примут нулевое значение - логический нуль (см. диаграммы на фиг.2 при 1 0)

QI 0: Q2 0; Оз 0: Q 0; Qs 0; Об 0.

По логическим уравнениям определяют состояния I- и К-входов триггеров, которые будут равны

ti 0; l2 1; 1з 0: U 0; Is 0; 1б 0; Ki 1; К2 1: Кз 1; К4 О: Кб 0; Кб О.

Поскольку 1К-триггер по входному импульсу на тактовой шине 12 при I О и К О не изменяет своего состояния, при I 1 и К 1 переключается в противоположное состояние, при 1 1 и К О переключается в состояние логической единицы, при и состояние логического нуля, то по первому входному импульсу в состояние логической единицы переключится только второй триггер, а все остальные останутся в прежнем состоянии, выходы и входы триггеров при этом примут следующие значения (см. фиг.2 при i 1):

Qi 0;Q4 0;Q5 0;Q6 0: 0;Ki 0;K2 1; .

По приходу второго тактового импульса по заднему фронту свое состояние изменят второй и третий триггеры, третий триггер переключится в состояние логической единицы, а второй - в состояние логического нуля, а выходы и входы триггеров примут следующие значения (см. диаграммы фиг.2 при t 2);

Qi 0; Q2 0; Оз 1; Q4 0; Qs 0; Об 0;li 1; 0; l4 0;ls 0; б 0; Ki 0; K2 1; Кз 1; K4 0; KB 0; Кб 0.

Рассматривая и далее таким же образом работу предлагаемого делителя, получают все состояния выходов и входов каждого 1К-триггера 1-6 (см. диаграммы фиг.2).

После 46-го импульса делитель будет

0 находиться в состоянии, при котором

Qi 1; 02 0:03 0; 1; li 0; l2 0; l4 1; 15 1; 1б 1; Ki 1; К2 0; Кз 0; К4 1; Ks 1; Кб 1.

При данных состояниях I- и К-входов

5 1К-триггеров после поступления очередного 47-го входного импульса произойдет переключение первого, четвертого, пятого и шестого триггеров и делитель вернется в исходное нулевое состояние. При непре0 рывном поступлении входных импульсов цикл работы делителя будет повторяться че- t рез каждые 47 импульсов.

Применение предлагаемого синхронного делителя частоты на 47 позволит упростить функциональную схему делителя на пять логических элементов (31 %) и 9 цепей (18 %), повысить надежность за счет у прощения схемы, повысить стабильность работы делителя за счет снижения паразитных емкостей, обусловленного сокращением количества элементов и цепей, приводящим к уменьшению линий связи и количества их взаимных пересечений, а также снизить потребляемую мощность примерно на 17% за

5 счет сокращения количества активных логических элементов.

Формула изобретения Синхронный делитель частоты на 47, содержащий первый, второй, третий, четвертый, пятый и шестой 1К-триггеры, С- и R-входы которых соединены соответственно с входной шиной и с шиной сброса, первый элемент И, выход которого соединен с I- и К-вхсдами шестого 1К-триггера, первый

5 вход-с прямым выходом первого 1К-триггера и с первым входом второго элемента И, выход которого соединен с К-входом пятого 1К-триггера, третий элемент И, выход которого соединен с 1-входом четвертого 1К-триг0 гера, первую и вторую выходные шины, которые соединены соответственно с прямым и с инверсным выходами шестого 1Ктриггера, отличающийся тем, что, с цельна повышения надежности и устойчивости работы за счет упрощен 1я, в него введены первый и второй элементы ИЛИ, выходы которих соединены с К-входами соответстsaHHO третьего и.второго 1К-триггеров, прямой выход первого из которых соединен с первым входом второго элемента ИЛИ и с

1-8ХОДОМ первого 1К-триггвра, инверсный выход которого соединен с 1-входом второго I К-триггера и с вторым входом второго элемента ИЛИ. К-вход - с инверсным выходом третьего 1К-триггера, 1-«ход которого соединен с прямым выходом второго 1К-триггера и с первым входом первого элемента ИЛИ, второй, третий и четвертый входы которого соединены с инверсными выходами соответственно шестого, пятого и четвертого 1К-триггеров, К-вход последнего из которых соединен с выходом

третьего элемента И, первый вход которого соединен с прямым выходом первого 1Ктриггера, второй вход - с инверсным выходом второго 1К-триггера и с вторыми

входами первого и второго элементов И, прямой зыход пятого 1К-триггера соединен с третьим входом первого элемента И, четвертый вход которого соединен с прямым выходом четвертого I К-триггера и с третьим

входом второго элемента И, выход которого соединен с 1-входом пятого 1К-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты | 1986 |

|

SU1374425A1 |

| Делитель частоты | 1989 |

|

SU1676096A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1330757A1 |

| Вычитающий декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383492A1 |

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383494A1 |

| Синхронный делитель частоты на 12 | 1987 |

|

SU1431068A1 |

| Синхронный делитель частоты | 1989 |

|

SU1676097A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

| Делитель частоты | 1985 |

|

SU1338062A1 |

Изо:6ретение относится к цифровой технике и может быть использовано, например, при построении хронизаторов, цифровых синтезаторов частоты. Цель изобретения - повышение надежности и устойчивости работы за счет упрощения - достигается введением первого 10 и второго 11 элементов ИЛИ. Устройство также содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5. шестой 6 IK-триггеры, первый 7. второй 8. третий 9 элементы И, тактовую шину 12, шину 13 сброса и выходные шины 14 и 15.2 ил.

01 г J i 5 б 7 8 3 К II ЙВ;415 «ni8eff2 2J 4Z5 7 aj JfJ UA«J6J7J WWM««««4eO

i 1ши1шшлш1Ш1шг1гпллшг11Г1Шшлллшгплш1Шшлллшшлл

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев И.Н | |||

| и др | |||

| Микроэлектронныесхемы цифровых устройств | |||

| - М.: Сов.радио,1975.С | |||

| Регулятор давления для автоматических тормозов с сжатым воздухом | 1921 |

|

SU195A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-02-23—Публикация

1990-01-17—Подача