СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| Синхронный делитель частоты | 1986 |

|

SU1374425A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1330757A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

| Делитель частоты | 1985 |

|

SU1338062A1 |

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Делитель частоты на 11 | 1987 |

|

SU1522398A1 |

| Синхронный делитель частоты на 17 | 1985 |

|

SU1285593A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

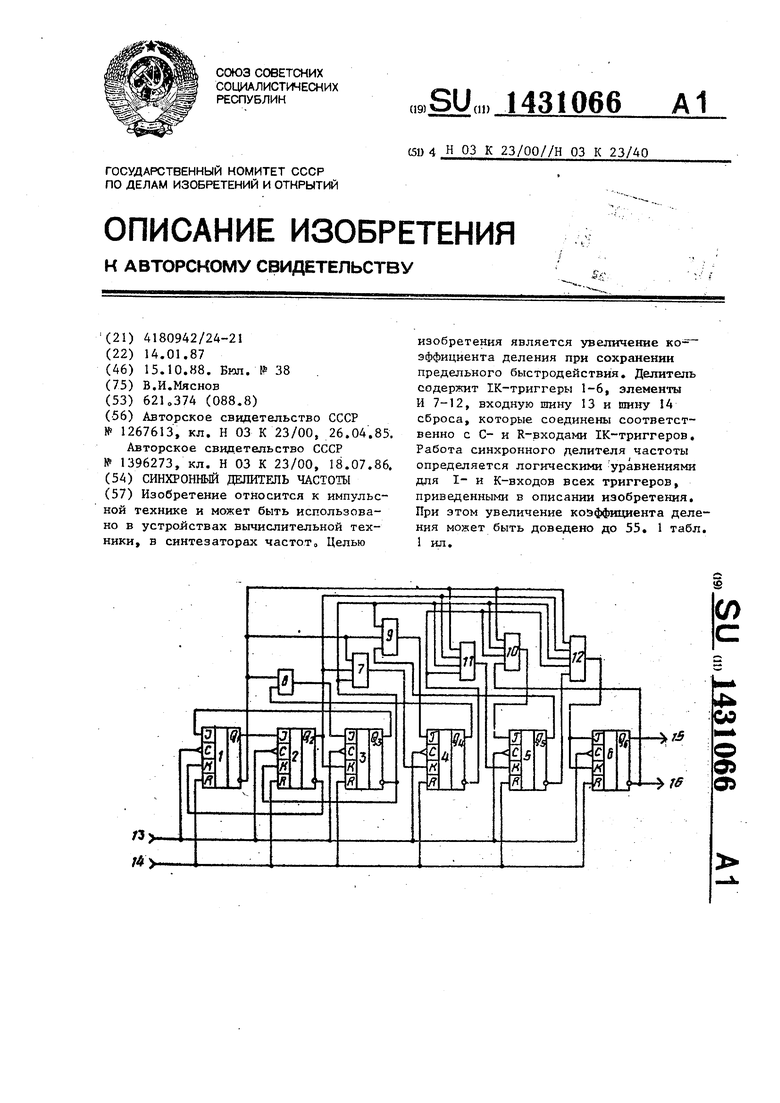

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники, в синтезаторах частот. Целью изобретения является увеличение коэффициента деления при сохранении предельного быстродействия. Делитель содержит 1К-триггеры 1-6, элементы И 7-12, входную шину 13 и шину 14 сброса, которые соединены соответственно с С- и R-входами 1К-триггеров. Работа синхронного делителя частоты определяется логическими уравнениями для I- и К-входов всех триггеров, приведенными в описании изобретения. При этом увеличение коэффициента деления монет быть доведено до 55. 1 табл. 1 ил.

5 fff

о а

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники, в синтезаторах частот

Цель изобретения - увеличение коэффициента деления (до 55) при сохранении предельного быстродействия,

На чертеже приведена электрическая функциональная схема синхронного делителя частоты.

Синхронный делитель частоты содержит первьш, 1, второй 2, третий 3, четвертый 4, пятый 5 и шестой 6 IK- триггеры, первый 7, второй 8, третий 9, четвертый 10, пятый 11 и шестой 12 элементы И, входную шину 13 и шину 14 сброса, которые соединены соответственно с С- и R-входами первого 1 второго 2, третьего 3, четвертого 4, пятого 5 и шестого 1К-триггеров,

1-вход первого 1К-триггера 1 соединен с прямым выходом третьего IK- триггера 3, К-вход - с инверсным выходом второго 1К-триггера 2, 1-вход которого соединен с прямым выходом первого 1К-триггвра I, 1-вход третьего 1К-триггера 3 соединен с выходом второго элемента И 8, К-вход - с прямым выходом второго 1К-триггера 2, с третьим входом первого элемента И 7, с четвертым входом пятого элемента И 11 и с пятым входом шестого элемента И 12. К-вход второго 1К-триггера 2 соединен с инверсным выходом третье го 1К-триггера 3, с вторым входом первого элемента И 7 и с первыми входами третьего 9, четвертого 10, пятого 11 и ше стого 12 элементов И. I- и К-входы четвертого К-триггера 4 сое- динены с выходами соответственно третьего и первого элементов И 9 и 7, I- и К-входы пятого 1К-триггера 5 соединены с выходами соответственно четвертого и пятого элементов И 10 и 11, 1-й К-входы шестого 1К-триг- гера fi соединены с выходом шестого элемента И 12, второй вход которого соединен с инверсным выходом пятого 1К-триггера 5, прямой вькод которого соединен с вторым входом третьего элемента И 9.Прямой выход четвертого 1К-триггера 4 соединен с первым входом второго элемента И 8, второй вход которого соединен с инверсным выходом первого 1К-триггера 1, с первым входом первого элемента И 7, с третьими входами третьего 9 и пятого 11 элементов И и с четвертыми входами чет

вертого 10 и шестого 12 элементов И, Инверсный выход четвертого 1К-тригге- ра 4 соединен с третьими входами четвертого 10 и шестого 1 2 элементов И и вторым входом пятого элемента И 11. Инверсный выход шестого 1К-триггера 6 соединен с вторым входом четвертого элемента И 10. Первой 15 и второй 16 выходными шинами устройства являются соответственно прямой и инверсный выходы шестого 1К-триггера 6.

При указанной схеме соединения элементов синхронного делителя частоты логические уравнения для I- и К-вхо- дов всех его 1К триггеров следующие:

0

О 0

QaJ Q,r

3 QiQ4;

2

К, - Q,; KI Qj; Kj Кф QiQiQ3; KS QjQjQaQ.; K I..

5

14 QiQaQ If QiQ3Q4Qfc;« i Q,QaQ3Q4Q55

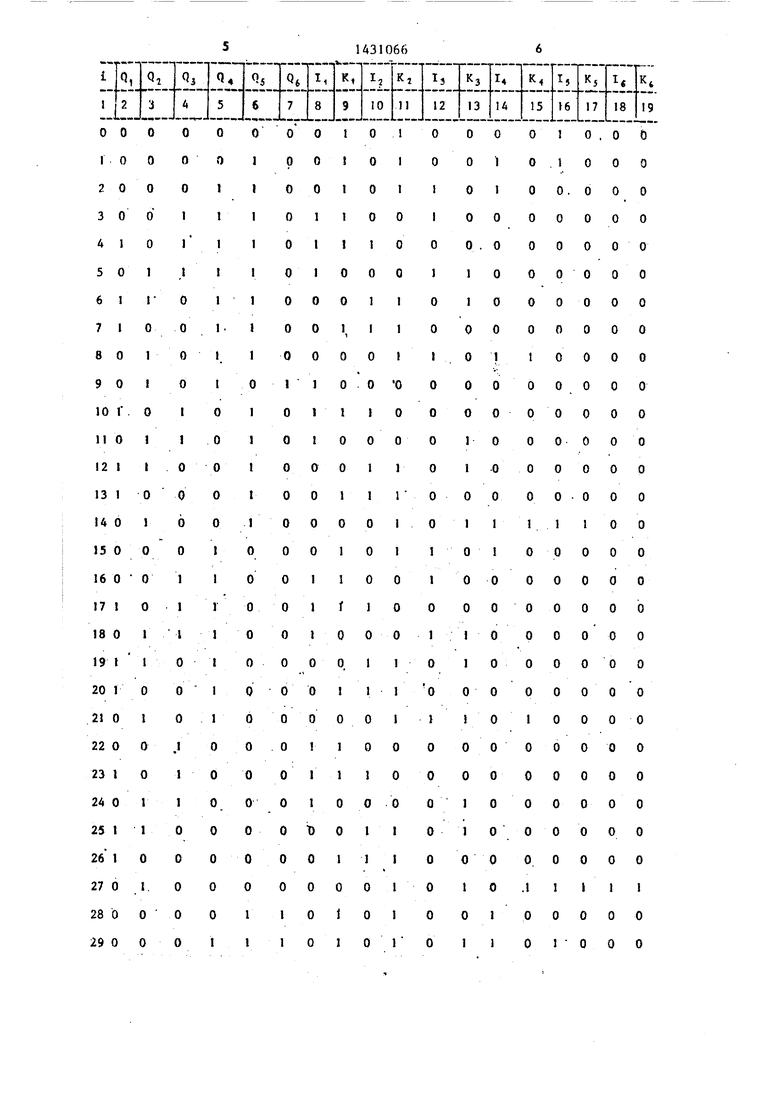

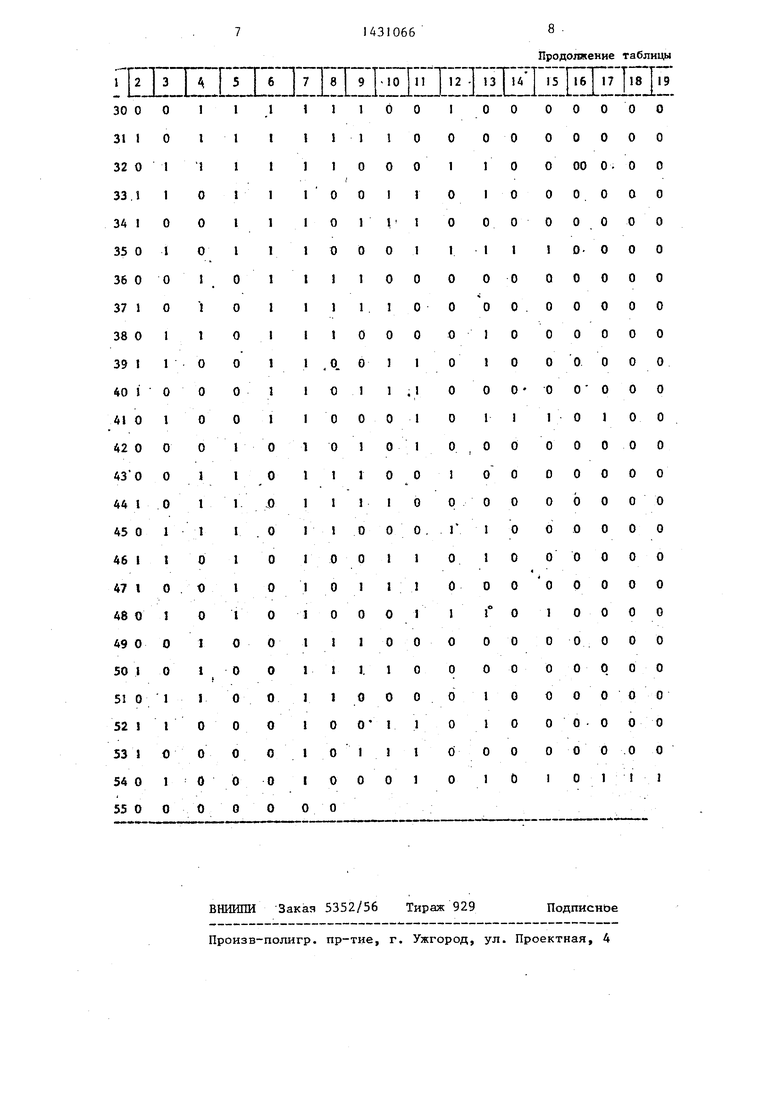

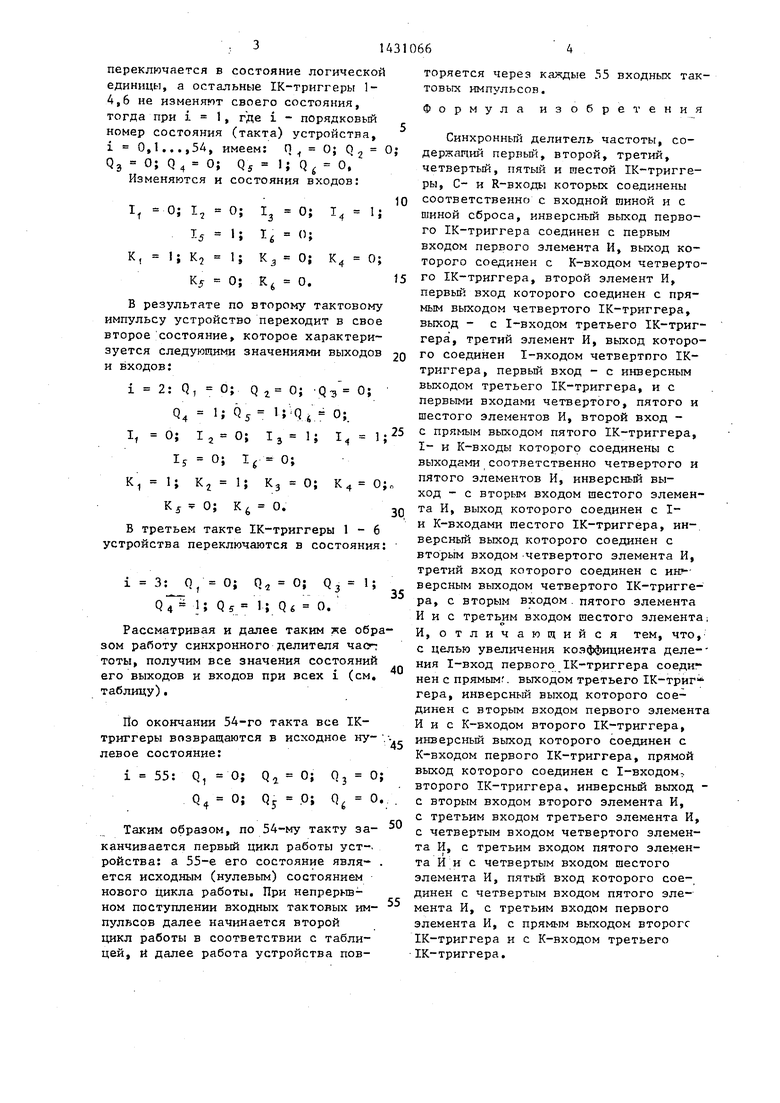

Работа синхронного делителя частоты, определяемая логическими уравнениями для I-- и К-входов всех его 1К-триггеров, проходит в следующем порядке.

По сигналу Сброс, поступающему в виде импульса по шине 14 1К-тригге- ры 1 - 6 устанавливаются в исходное нулевое состояние, после чего состояния выходов будут равны

Q 0; Qi 0; Q О; Q : 0; Q О; Q О.

На основании логических уравнений для I- и К-входов 1К-триггеров 1-6 состояния I- и К-входов следующие:

Ii Qj О; la Q 1 Q; .

1э QiQ4 0 i4 QiQ3Qi o; If j i K, Q 1;

Ka Qs 1; Кз Q, 0; 4 Q.QaQa 0; Kj QiqjQ3Q 0;

i QtQ K i 0.

Поскольку IK-триггер no последую- ще1му входному тактовому импульсу на шине 13 при I О и не изменяет своего состояния, при I 1 и - переключается в противоположное состояние, при I 1 и К О - переключается в состояние логической единицы, а при в состояние логического нуля, то по первому так- тоному импульсу только 1К-триггер 5 .

переключается в состояние логическор единицы, а остальные 1К-триггеры 1- 4,6 не изменяют своего состояния, тогда при , где i - порядковый номер состояния (такта) устройства, i 0,1... ,54, имеем: П О; Q j О,- РЗ О; Q О; QS If Q О, Изменяются и состояния входов:

10

1 0; I, 0; 1 О; 1 I;

Ij 1; f-i О; К, 1; к, 1; К 0; К 0;

% 0; К О. 15

В результате по второму тактовому импульсу устройство переходит в свое второе состояние, которое характеризуется следующими значениями выходов 20 и входов:

i 2: Q, 0; Q . 0; Q О;

Q4 1; 5 0;. I, О; Ij О; 1з 1; I, 1;

Ij О; 1 0;

К, 1; К 1; Кз О; К4 0;„ К 0; К 0.30

Б третьем такте 1К-триггеры 1 - 6 устройства переключаются в состояния:

1 3: Q/ О; Q 0; Q 1; Q7 1; Qs 1; Q« 0.

Рассматривая и далее таким же образом работу синхронного делителя част;

тоты, получим все значения состояний

/ 40 его выходов и входов при всех i Сем,

таблицу).

По окончании 54-го такта все IK- триггеры возвращаются в исходное ну- .- 4

левое состояние:

1 55: Q, 0; Q 0; Qj О;

Q 0; Qy .0; Q О.. .

Таким образом, по 54-му такту за- канчивается первый цикл работы уст-, ройства: а 55-е его состояние явля- . ется исходным (нулевым) состоянием нового цикла работы. При непрерьт- ном поступлении входных тактовых импульсов далее начинается второй цикл работы в соответствии с таблицей, и далее работа устройства пов,-

10

15

20

0

5

0

5

.

торяется через каждые 55 входных тактовых импульсов.

Формула изобретения

Синхронный делитель частоты, со- держапий первый, второй, третий, четвертый, пятый и тестой 1К-тригге- ры. С- и R-входы которых соединены соответственно с входной шиной и с шиной сброса, инверсный выход первого 1К-триггера соединен с первым входом первого элемента И, выход которого соединен с К-входом четвертого 1К-триггера, второй элемент И, первый вход которого соединен с прямым выходом четвертого 1К-триггера, выход - с 1-входом третьего 1К-триг- гера, третий элемент И, выход которого соединен 1-вкодом четвертого IK- триггера, первый вход - с инверсным выходом третьего 1К-триггера, и с первыми входами четвертого, пятого и шестого элементов И, второй вход - с прямым выходом пятого 1К-триггера, I- и К-входы которого соединены с выходами соответственно четвертого и пятого элементов И, инверсньй выход - с вторым входом шестого элемента И, выход которого соединен с I- и К-входами шестого 1К-триггера, инверсный выход которого соединен с вторым входом -четвертого элемента И, третий вход которого соединен с версным выходом четвертого 1К-тригге- ра, с вторым входом . пятого элемента И и с третьим входом шестого элемента; И, отличающийся тем, что, с целью увеличения коэффициента деле- ния 1-вход первого 1К-триггера соединен с прямымг. выходом третьего ХК-триг гера, инверсный выход которого соединен с вторым входом первого элемента И и с К-входом второго 1К-триггера, инверсный выход которого соединен с К-входом первого 1К-триггера, прямой выход которого соединен с 1-входом второго 1К-триггера, инверсный выход - с вторым входом второго элемента И, с третьим входом третьего элемента И, с четвертым входом четвертого элемента И, с третьим входом пятого элемента И и с четвертым входом шестого элемента И, пятый вход которого соединен с четвертым входом пятого элемента И, с третьим входом первого элемента И, с прямым выходом второгс 1К-триггера и с К-входом третьего 1К-триггера.

00 10 о 00

О О

1 О

О 1

|О

1

I

О1

Оi Г.О

1О1

2II

31О

4О1

5ОО

6О О

71О

8ОI

9I1

01О ОI

2ОО

31О

4О1

511 б 1О

7ОI.

8ОО

9ОО

О

О

О

1

Г

I

О

о

о

о

I

1

о

о

6

о

1

1

I

о

о

о

.1

1

1

о

о

о

о

о

о

о

1

1

1

I

1

I

I

о

о

о

о

о

I

1

1

1

I

1

1

о

о

о

о

о

о

о

I

о

1

I

1

1

1

1

I

1

о

1

J

1

1

1

о

о

о

о

о

о

о

о

о

о

о

о

о

1

1

оо

оо

оо

о1

о о

оо

оо

0о

11 оI оt оо оо оо оо о1 о1 оI оо оо оо

0

оI

о1

оъ

оо

оо

1о 1о

о о о о

1

оо

о1

оо

0о

1I оо

01

11 оо

1о

1о

г1

оо

01

11 оо

1о

1

оо

01

11

0о

1о

1о

I

I

1

о

о

о

1

1

I

о

о

о

1

I

1

1

о

о

о

1

1

I

о

о

о

I

I

I

1

1

о о I I

о 1

о о I

о о о о о о I 1

о 1

о о I о о о о о о о о

оо

о

о1

0о о . о

1о

1о

оо

о1

оо

0о

1о

1о

0о

11

0

оо

оо

10

1о

оо

о

оо

оо

1о

1о

о 1

о

о

о

i о 0. о 000 000 о 00

000

000

1о о

о 00

00 о

о 00

000

о 00 11 1

00о 000 000 000 000 000

1о о

000 000 000 00 о 000

л 1 I

1

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

оо

0о

1I оо оо

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-15—Публикация

1987-01-14—Подача