Изобретение относится к импульсной технике и может быть использовано в синтезаторах частот.

Цель изобретения - повышение быстродействия .

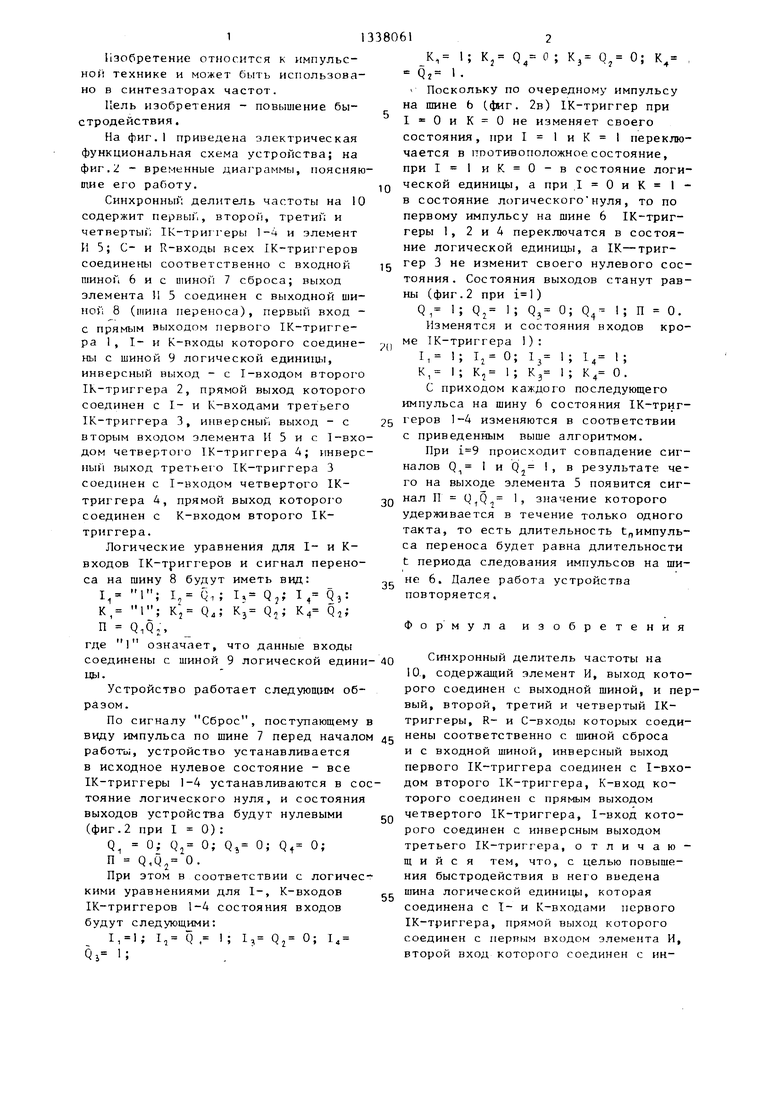

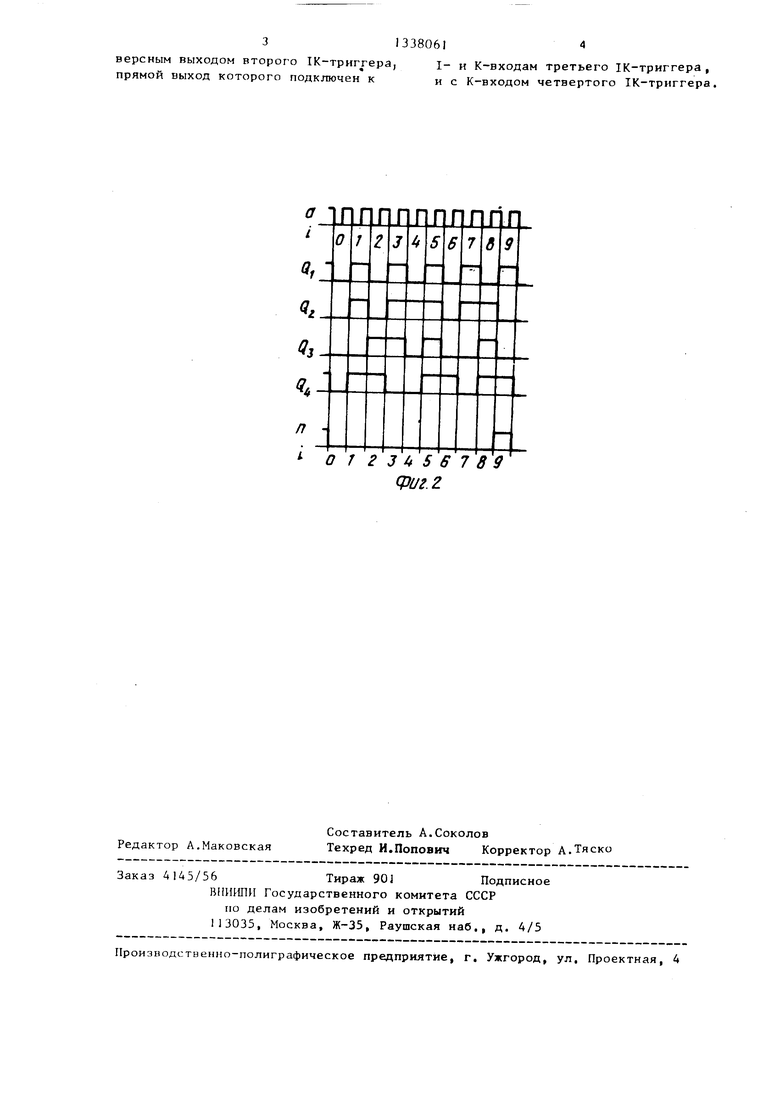

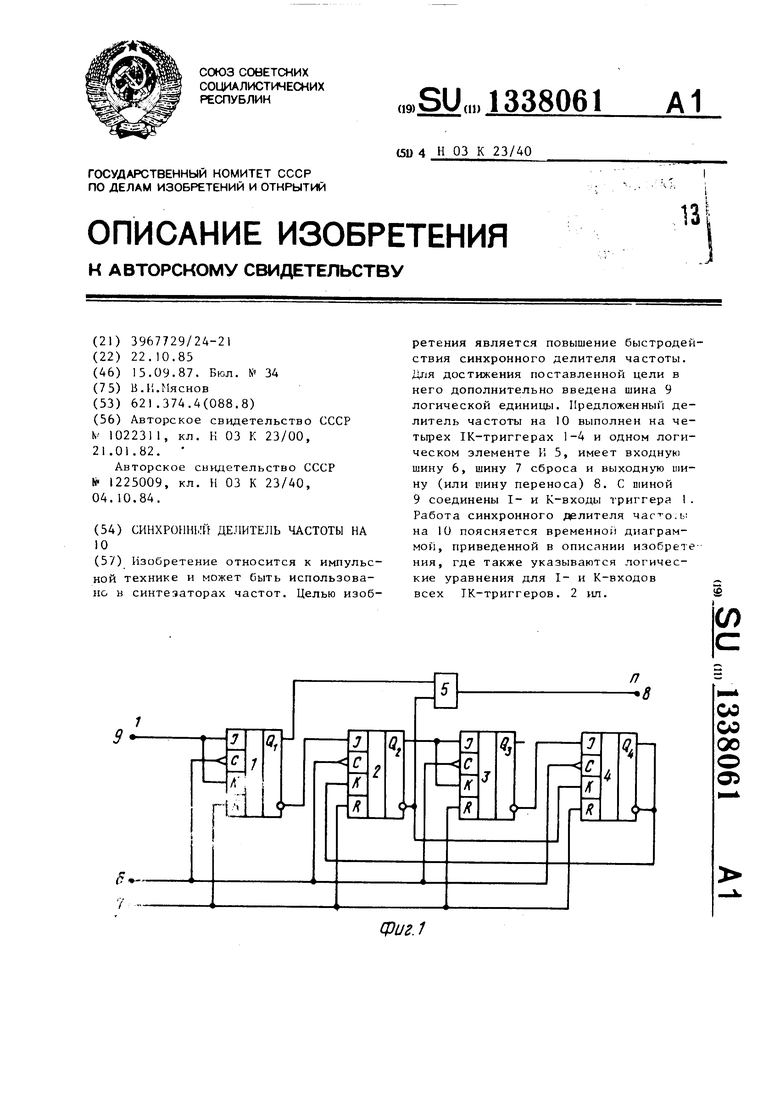

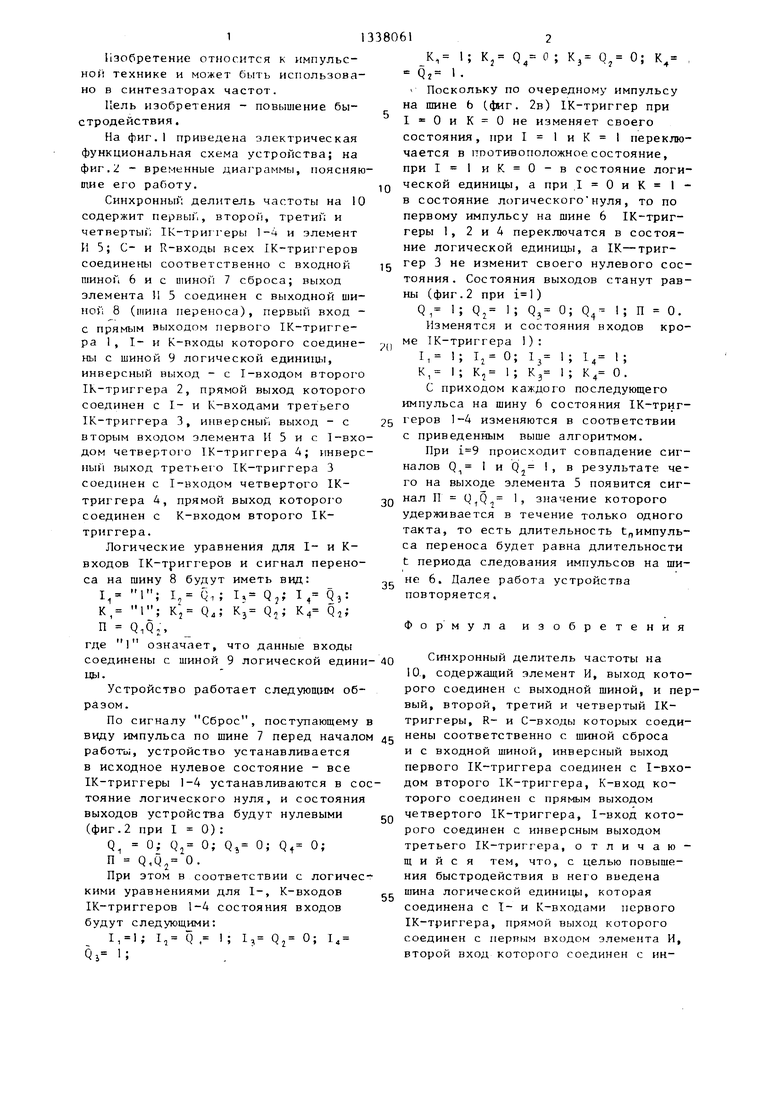

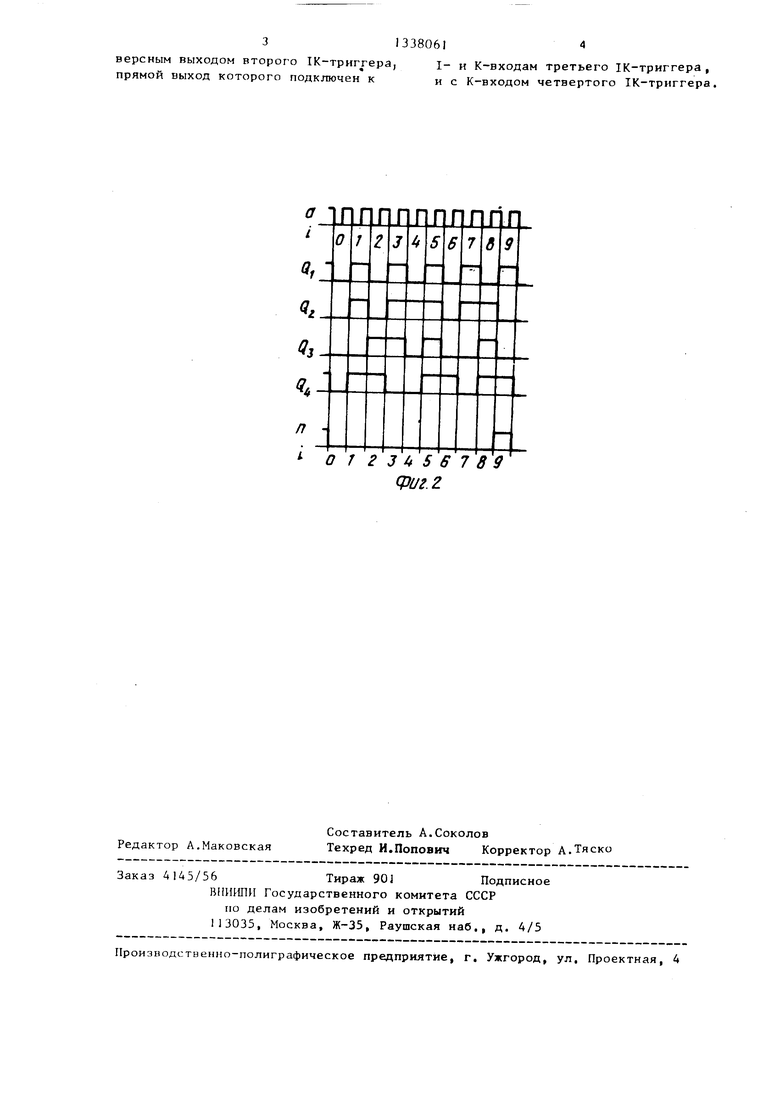

На фиг,1 приведена электрическая функциональная схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Синхронный делитель частоты на 10 содержит первыГ., второй, третий и четвертый 1К-триггеры 1-4 и элемент И 5; С- и R-входы всех 1К-триггеров соединены соответственно с входной шиной бис шиной 7 сброса; выход элемента И 5 соединен с выходной шиной 8 (шина переноса), первый вход - с прямым выходом первого 1К-тригге- ра 1, I- и К-входы которого соединены с шиной 9 логической едини1ц,1, инверсный выход - с 1-входом второго 1К-триггера 2, прямой выход которого соединен с I- и К-входами третьего 1К-триггера 3, инверсный выход - с вторым входом элемента И 5 и с 1-входом четвертого 1К-триггера А; инверсный выход третьего 1К-триггера 3 соединен с 1-входом четвертого IK- триггера 4, прямой выход которого соединен с К-входом второго IK- триггера.

Логические уравнения для I- и К- входов 1К-триггеров и сигнал переноса на шину 8 будут иметь вид: 1. 1„ Q,,; 1, Q

2 4 3

П Q,Q,,

где означает, что данные входы соединены с шиной 9 логической един цы.

Устройство работает следующим образом.

. 1, Q,,; 1, QJ; 1, Q,: К к; Q,; К, Q,

К4 Q7.

Синхронный делитель частоты на 10,, содержащий элемент И, выход ко рого соединен с выходной шиной, и вый, второй, третий и четвертый IK триггеры, R- и С-входы которых соед

По сигналу Сброс, поступающему в виду импульса по шине 7 перед началом 45 соответственно с шиной сброса работь;, устройство устанавливаетсяи с входной шиной, инверсный выход

в исходное нулевое состояние - все 1К-триггеры 1-4 устанавливаются в состояние логического нуля, и состояния

первого IK-триггера соединен с 1-вх дом второго 1К-триггера, К-вход ко торого соединен с прямым выходом четвертого 1К-триггера, 1-вход кот рого соединен с инверсным выходом третьего 1К-триггера, отличаю щийся тем, что, с целью повыш ния быстродействия в него введена шина логической едини1Цз1, которая соединена с Т- и К-входами первого 1К-триггера, прямой выход которого соединен с перным входом элемента И второй вход которого соединен с инвыходов устройства будут нулевыми (фиг.2 при ):

Q 0; Qj 0; Q, 0; Q 0;

П Q,q,, 0.

При этом в соответствии с логичкими уравнениями для I-, К-входов 1К-триггеров 1-4 состояния входов будут следующими:

1,1; 1, Q . 1; 1, Qj 0; I,

Qi 1;

10

15

u

- 40

3380612

К, 1; Kj Q О ; К Q 0; К ,

Qz 1.

Поскольку по очередному импульсу на шине b (фиг. 2в) 1К-триггер при изменяет своего состояния, при I 1 и К I переключается в противоположное состояние, при I 1 и К О - в состояние логической единицы, а при I О и К 1 - в состояние логического нуля, то по первому импульсу на шине 6 1К-триг- геры 1, 2 и 4 переключатся в состояние логической единицы, а IK-триггер 3 не изменит своего нулевого состояния. Состояния выходов станут равны (фиг.2 при )

Q, I; Q, 1; Q3 0; 1; п 0.

Изменятся и состояния входов кроме 1К-триггера 1):

1, I; Ij 0; lj 1; 1, 1; К, I ; К,, 1 ; Кз 1 ; К 0.

С приходом каждого последующего импульса на шину 6 состояния 1К-триг- 25 геров 1-4 изменяются в соответствии с приведенным выше алгоритмом.

При происходит совпадение сигналов Q I и Q,| I, в

30

35

:,, , результате чего на выходе элемента 5 появится сигнал П Q,QT 1, значение которого удерживается в течение только одного такта, то есть длительность tпИмпyль- са переноса будет равна длительности t периода следования импульсов на шине 6. Далее работа устройства повторяется,

Формула изобретения

Синхронный делитель частоты на 10,, содержащий элемент И, выход которого соединен с выходной шиной, и первый, второй, третий и четвертый IK- триггеры, R- и С-входы которых соедивм 45 соответственно с шиной сброса и с входной шиной, инверсный выход

0

5

первого IK-триггера соединен с 1-входом второго 1К-триггера, К-вход которого соединен с прямым выходом четвертого 1К-триггера, 1-вход которого соединен с инверсным выходом третьего 1К-триггера, отличающийся тем, что, с целью повышения быстродействия в него введена шина логической едини1Цз1, которая соединена с Т- и К-входами первого 1К-триггера, прямой выход которого соединен с перным входом элемента И, второй вход которого соединен с инверсным выходом второго 1К-триг ера, прямой выход которого подключен к

Редактор А.Маковская

Составитель А.Соколов

Техред И.Попович Корректор А.Тяско

Заказ 4145/56Тираж 901Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

I- и К-входам третьего 1К-триггера , и с К-входом четвертого 1К-триггера,

7 23US6789

(иг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

| Синхронный делитель частоты на 17 | 1985 |

|

SU1285593A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Синхронный делитель частоты на 9 | 1986 |

|

SU1378055A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Синхронный делитель частоты на 12 | 1987 |

|

SU1431068A1 |

| Синхронный делитель частоты на 10 | 1984 |

|

SU1225009A1 |

Изобретение относится к импульсной технике и может быть использовано в синтезаторах частот. Целью изоб9ретения является повышение быстродействия синхронного делителя частоты. достижения поставленной цели в него дополнительно введена шина 9 логической единицы. Предложенный делитель частоты на 10 выполнен на четырех 1К-триггерах 1-4 и одном логическом элементе И 5, имеет входную шину 6, шину 7 сброса и выходную и1И- ну (или шину переноса) 8. С шиной 9 соединены I- и К-входы триггера 1. Работа синхронного делителя .ы на 10 поясняется временно диаграммой, приведенной в описании изобретения, где также указываются логические уравнения для I- и К-входов всех IK-триггеров. 2 ил. t сл 8 00 оо 00 о 05 Фиг.

| Прибор для измерения объема камер сгорания автомобильных и авиационных двигателей | 1954 |

|

SU102231A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синхронный делитель частоты на 10 | 1984 |

|

SU1225009A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-15—Публикация

1985-10-22—Подача