(21)4185881/24-2А

(22)26.01.87

(46) 23.10.88.БЮЛ. № 39 (71).Криворожский горнорудный институт

(72) Е.К.Бабец, В.П.Хорольский, В.Г.Хорошенький, Е.И.Сологуб, В.М.Яковлев ft Н.И.Сокур (53) 62-50 (088.8)

(56)Авторское свидетельство СССР № 1076873, кл. G 05 В 13/02, 1984. ,(54) АДАПТИВНЫЙ РЕГУЛЯТОР

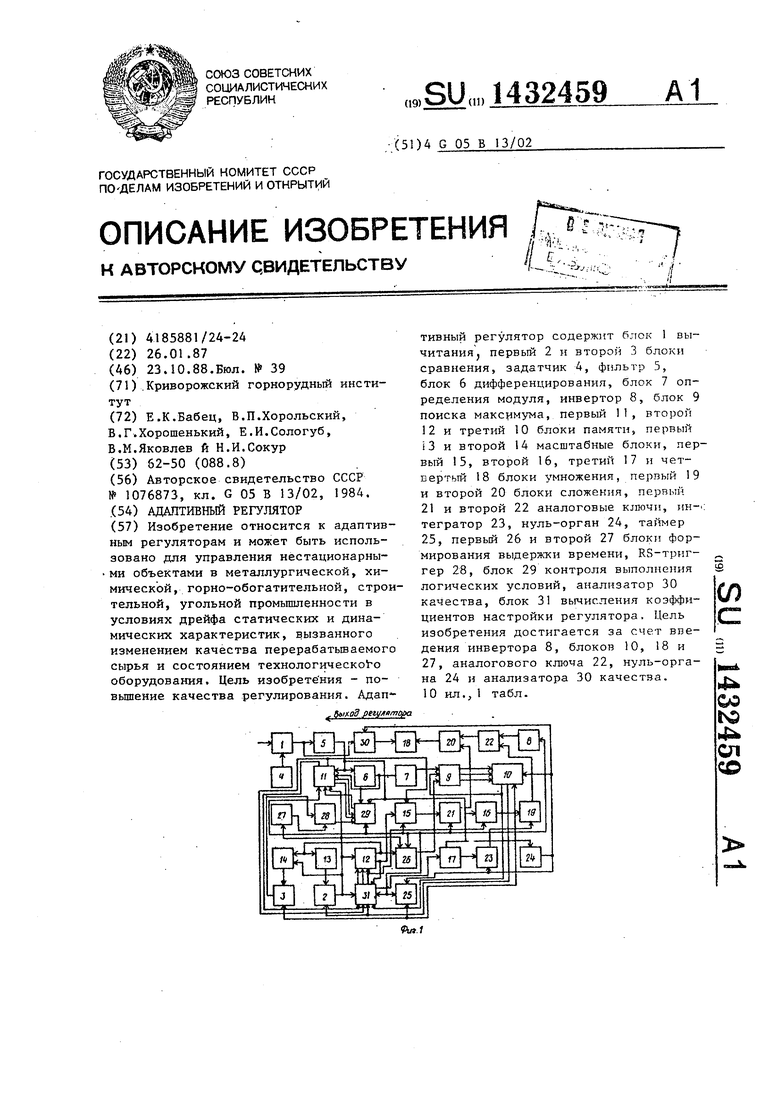

(57)Изобретение относится к адаптивным регуляторам и может быть использовано для управления нестационарны ми объектами в металлургической, химической, горно-обогатительной, строительной, угольной промьгашенности в условиях дрейфа статических и динамических характеристик, вызванного изменением качества перерабатьшаемого сырья и состоянием технологическо о оборудования. Цель изобрете ния - повышение качества регулирования. Адап fetij amtyta

тивный регулятор содержит блок 1 вычитания, первый 2 н второй 3 блоки сравнения, задатчик 4, фильтр 5, блок 6 дифференцирования, блок 7 определения модуля, инвертор 8, блок 9 поиска максимума, первый П, второй

12и третий 10 блоки памяти, первый

13и второй 14 масштабные блоки, первый 15, второй 16, третий 17 и четвертый 18 блоки умножения, первый 19 и второй 20 блоки сложения, первый

21 и второй 22 аналоговые ключи, ин- : тегратор 23, нуль-орган 24, таймер 25, первый 26 и второй 27 блоки формирования выдержки времени, RS-триг- гер 28, блок 29 контроля выполнения логических условий, анализатор 30 качества, блок 31 вычисления коэффициентов настройки регулятора. Цель изобретения достигается за счет введения инвертора 8, блоков 10, 18 и 27, аналогового ключа 22, нуль-органа 24 и анализатора 30 качества. 10 ил., 1 табл.

1C

(Л

4

N3

4 СП

г

1U32459

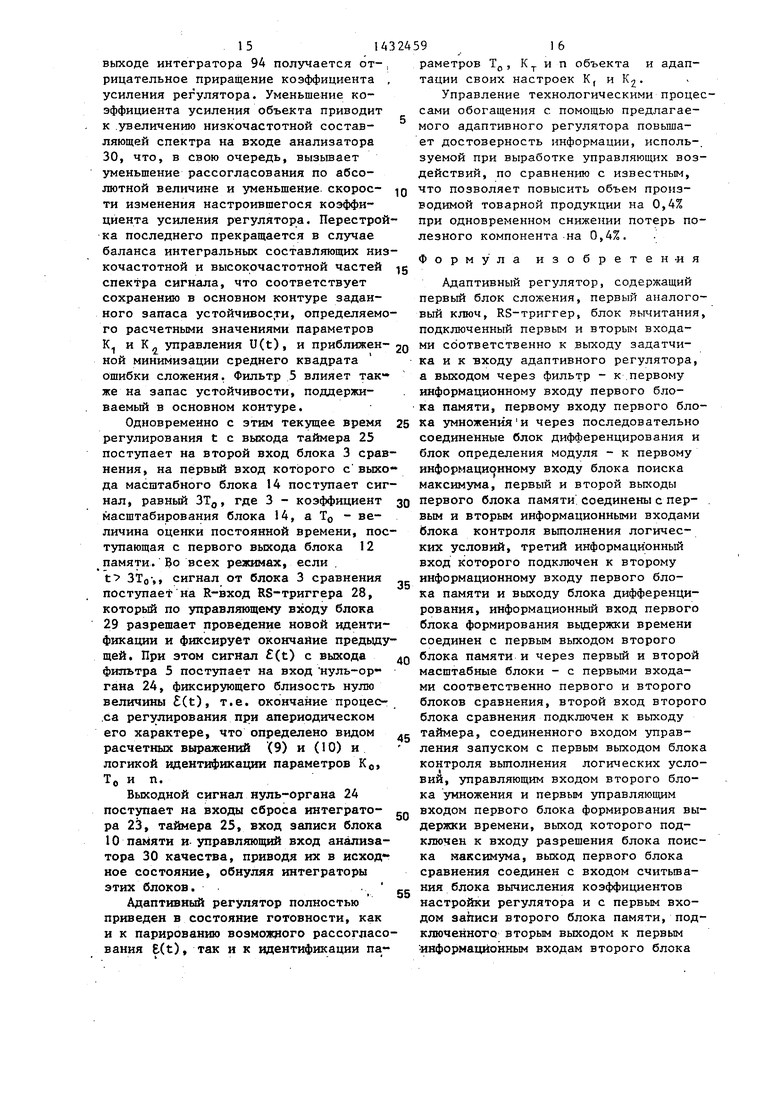

Изобретение относится к адаптивным регуляторам и может быть использовано для управления нестационарными объектами в металлургической, химической j горно-обогатительной, строительной, угольной промьшшеннос- ти в условиях дрейфа статических и динамических характеристик, вызванноблок-схемы первого и второго блоко памяти; на фиг.5 - блок-схема тайм ра; на фиг. 6 - блок-схема блока форми вания выдержки времени; на фиг. 7 -бл схема блока контроля выполнения логи ких условий; на фиг .8 блок-схема ан лизатора качества; на фиг.9 - блок схема блока вычисления коэффициент

го изменением качества перерабатывае- Ю настройки регулятора; на фиг.10 мого сырья и состоянием технологического оборудования.

Цель изобретения - повышение качества регулирования.

Сущность изобретения заключается в идентификации статического коэффициента Кр, постоянной времени Т, и порядка п объекта, описываемого передаточной функцией вида

W(P)

(ТоР+1)

(О

и пересчета коэффициентов К пропорциональной и К 2 интегральной 25 тей формируемого регулятором закона управления вида

15

К. (t) +

(i;)d C.

(2) 30

15

Идентификация переменных параметров объекта осуществляется путем анализа аналога переходной характеристики объекта на специальным образом сформулированное активное тестирующее воздействие, подаваемое на вход объекта в момент времени, когда выполнены логические условия возможности проведения идентификаций. В момент проведения идентификации обратная связь в системе разрьшается и формируется скачок. После окончания идентификации проводится проверка правиль Н04:ти новых расчетных значений К и K,j и осуществляется формирование новых управляющих воздействий.

Отличие изобретения заключается в использовании лишь части, до точки перегиба, переходной характеристики для определения параметров объекта, и точного аналитического расчета параметров управления по этим параметрам объекта, за счет чего noBbmiaiOTcrt качество и устойчивость управления.

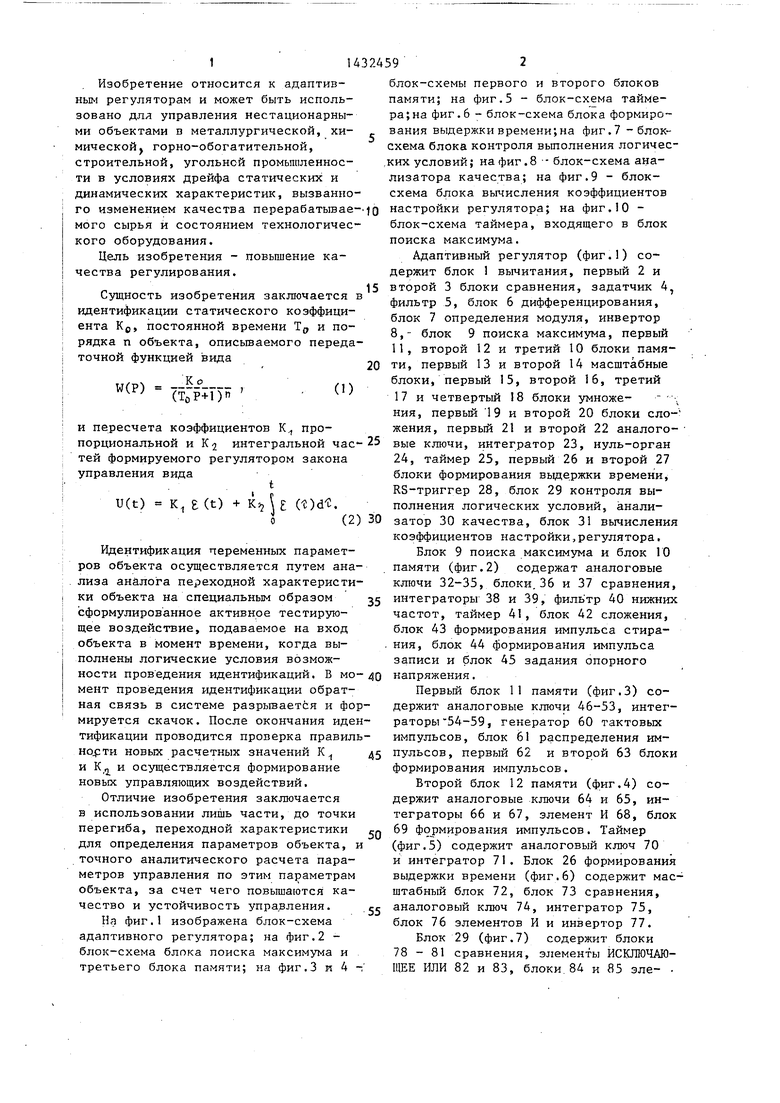

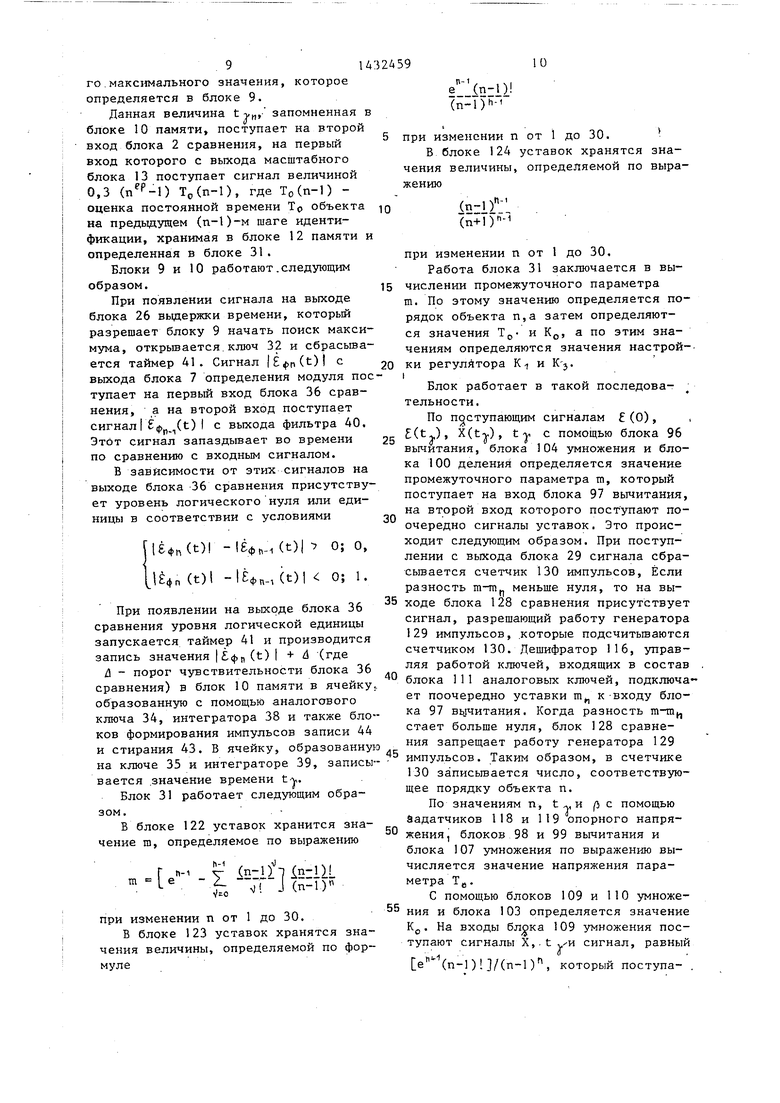

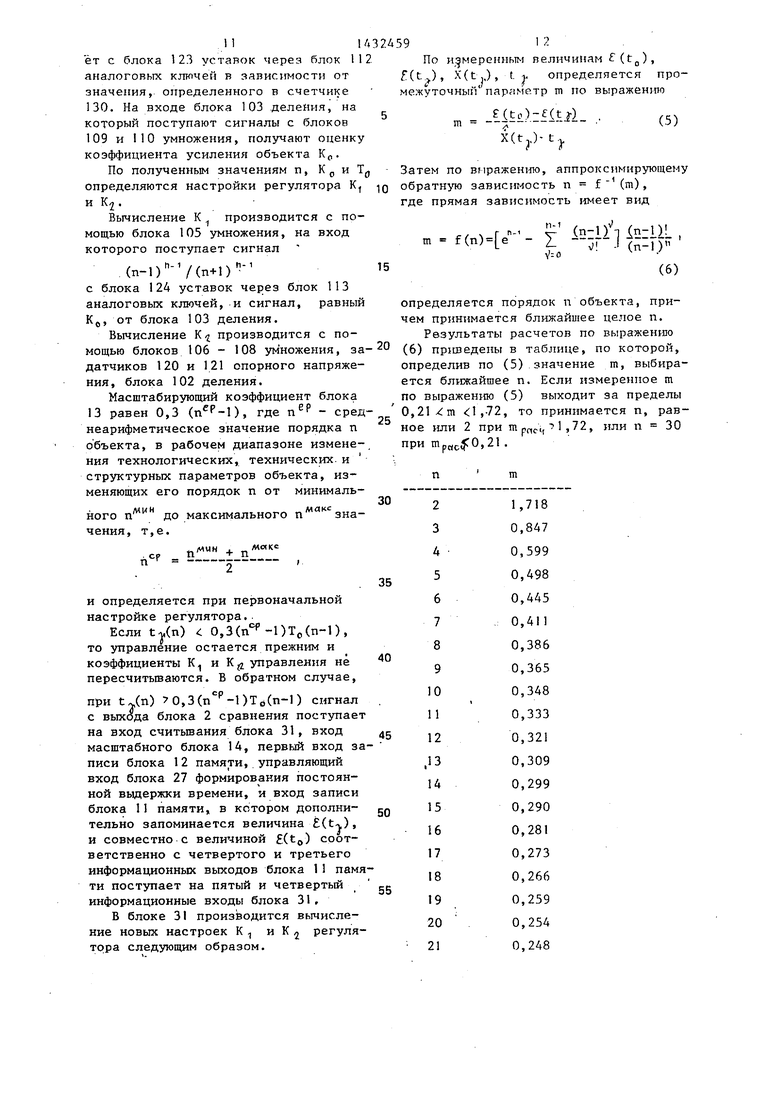

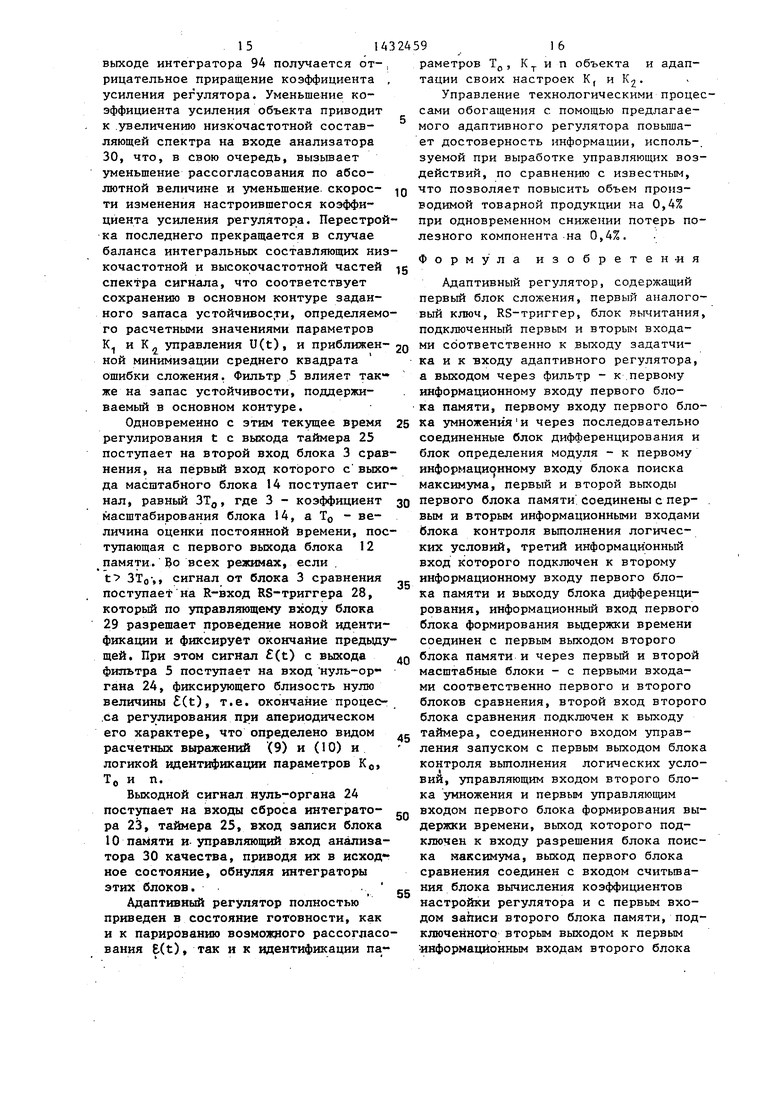

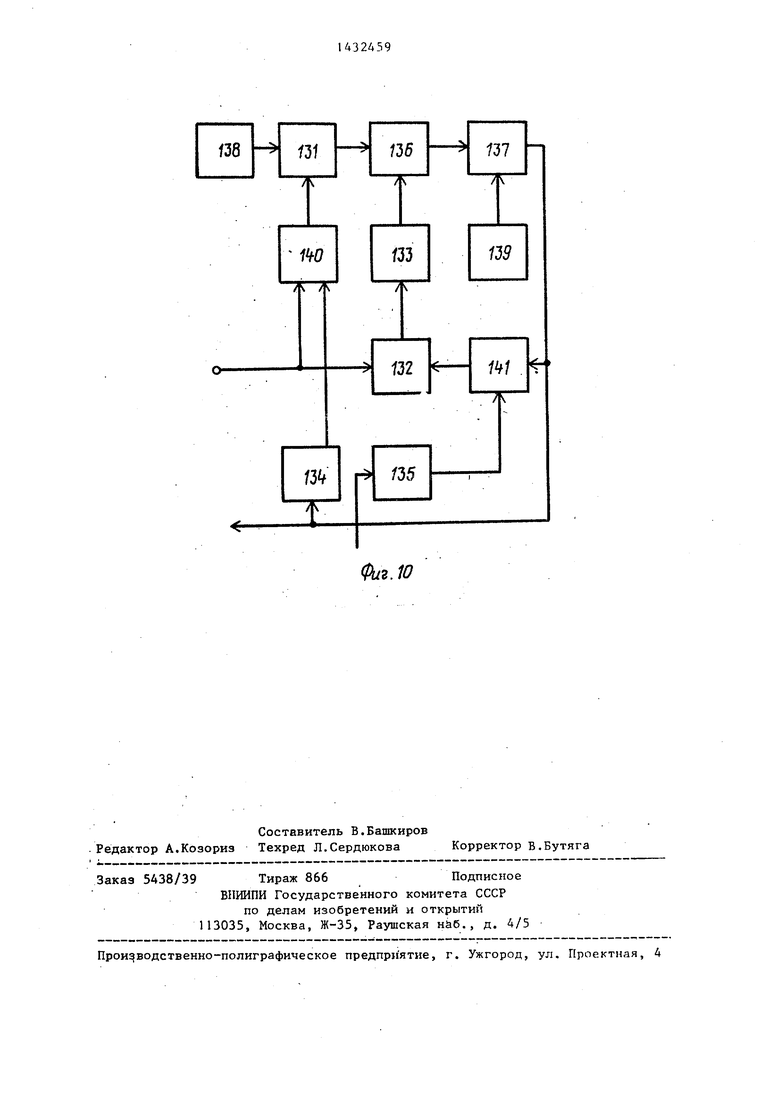

На фиг.1 изображена блок-схема адаптивного регулятора; на фиг.2 - блок-схема блока поиска максимума и третьего блока памяти; на фиг.З и 4

блок-схемы первого и второго блоков памяти; на фиг.5 - блок-схема таймера; на фиг. 6 - блок-схема блока формирования выдержки времени; на фиг. 7 -блок- схема блока контроля выполнения логических условий; на фиг .8 блок-схема анализатора качества; на фиг.9 - блок- схема блока вычисления коэффициентов

0

5

0

5

0 5

блок-схема таймера, входящего в блок поиска максимума.

Адаптивный регулятор (фиг.1) содержит блок вычитания, первый 2 и 5 второй 3 блоки сравнения, задатчик 4, фильтр 5, блок 6 дифференцирования, блок 7 определения модуля, инвертор 8,- блок 9 поиска максимума, первый П, второй 12 и третий 10 блоки памяти, первый 13 и второй 14 масштабные блоки, первый 15, второй 16, третий 17 и четвертый 18 блоки умноже- ния, первьй 19 и второй 20 блоки ело- жения, первый 21 и второй 22 аналого- вые ключи, интегратор 23, нуль-орган 24, таймер 25, первый 26 и второй 27 блоки формирования выдержки времени, RS-триггер 28, блок 29 контроля выполнения логических условий, анализатор 30 качества, блок 31 вычисления коэффициентов настройки,регулятора.

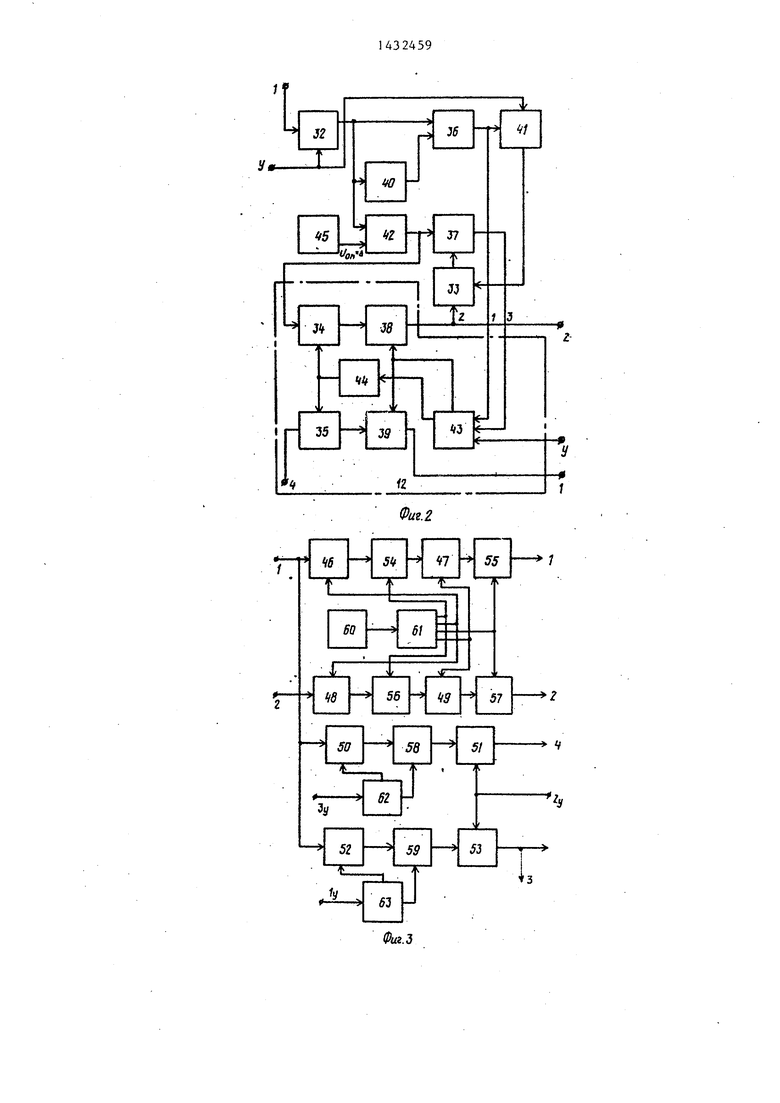

Блок 9 поиска максимума и блок 10 памяти (фиг.2) содержат аналоговые ключи 32-35, блоки.36 и 37 сравнения, интеграторы 38 и 39, фильтр 40 нижних частот, таймер 41, блок 42 сложения, блок 43 формирования импульса стирания, блок 44 формирования импульса записи и блок 45 задания опорного напряжения.

Первый блок 11 памяти (фиг.З) содержит аналоговые ключи 46-53, интеграторы 54-59, генератор 60 тактовых импульсов, блок 61 распределения импульсов, первый 62 и второй 63 блоки формирования импульсов.

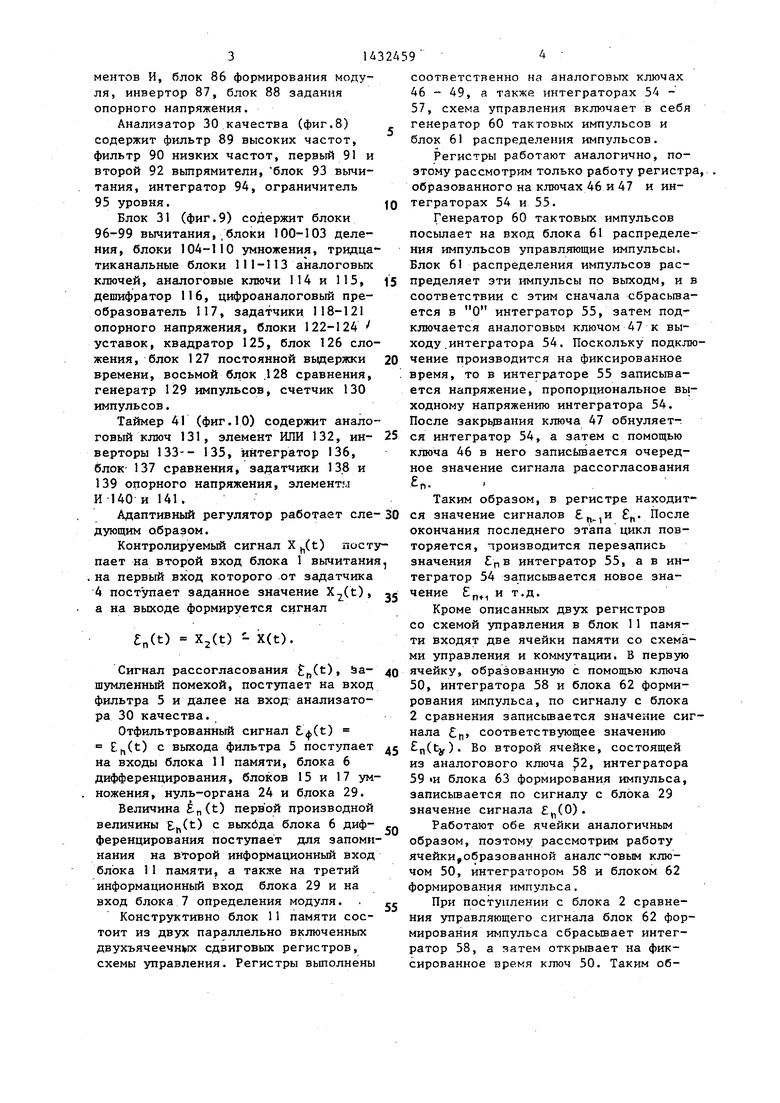

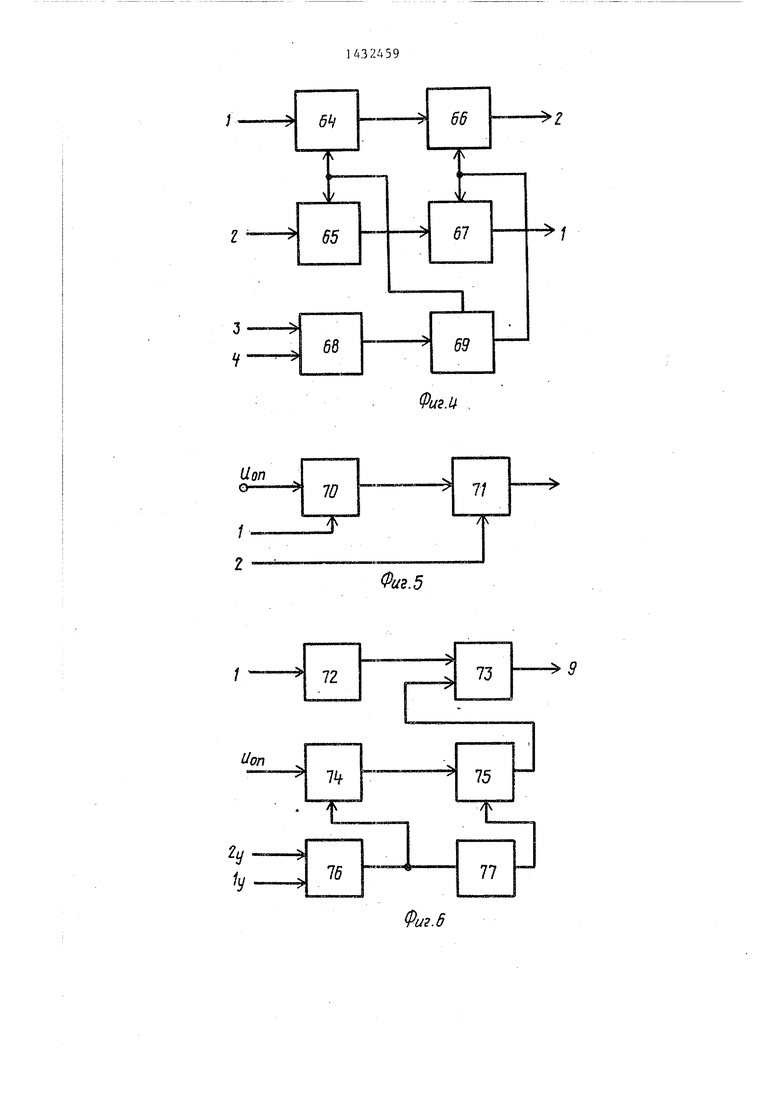

Второй блок 12 памяти (фиг.4) содержит аналоговые ключи 64 и 65, интеграторы 66 и 67, элемент И 68, блок Q 69 фojэмиpoвaния импульсов. Таймер (фиг.5) содержит аналоговый ключ 70 и интегратор 71. Блок 26 формирования выдержки времени (фиг.6) содержит масштабный блок 72, блок 73 сравнения, аналоговый ключ 74, интегратор 75, блок 76 элементов И и инвертор 77. Блок 29 (фиг.7) содержит блоки 78-81 сравнения, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 82 и 83, блоки.84 и 85 эле-

5

31Д

ментов И, блок 86 формирования модуля, инвертор 87, блок 88 задания опорного напряжения.

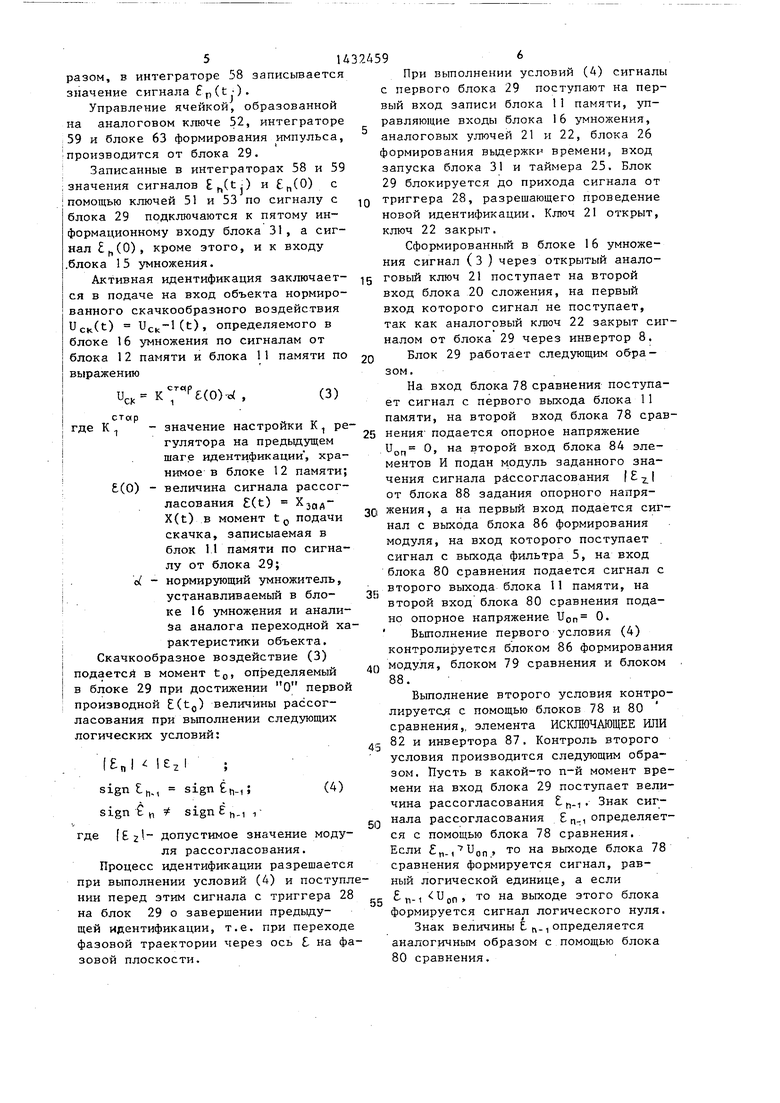

Анализатор 30 качества (фиг,8) содержит фильтр 89 высоких частот, фильтр 90 низких частот, первый 91 и второй 92 вьтрямители, блок 93 вычитания, интегратор 94, ограничитель 95 уровня.

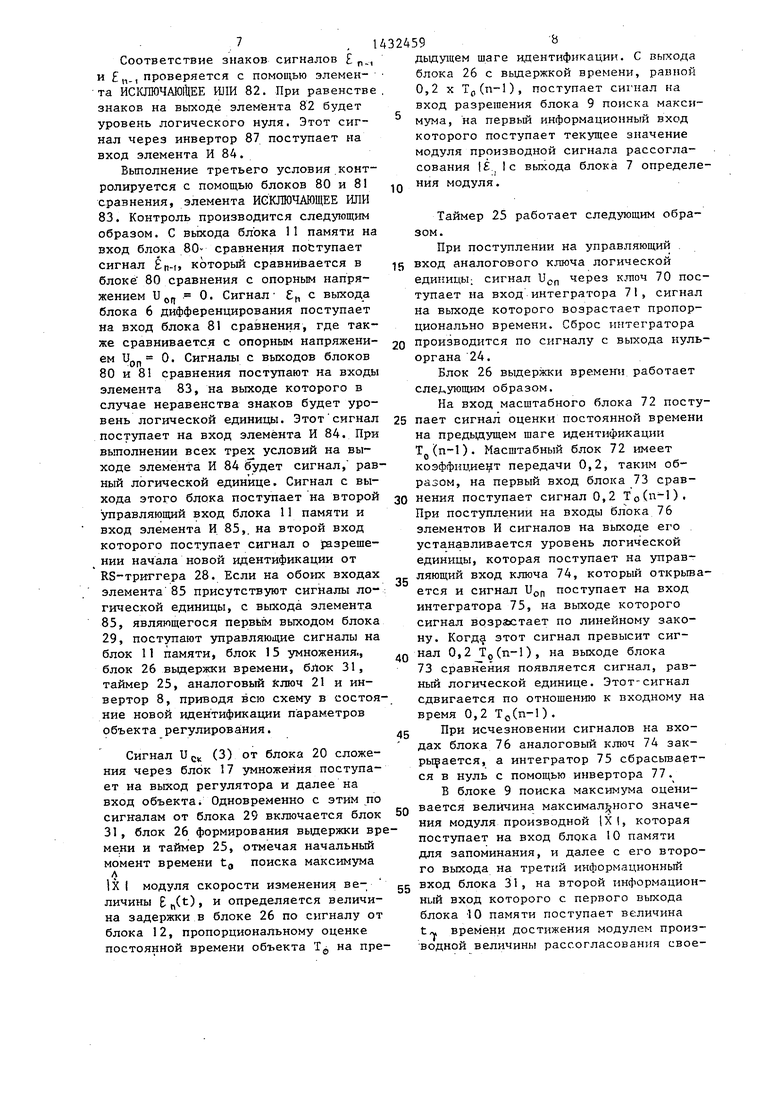

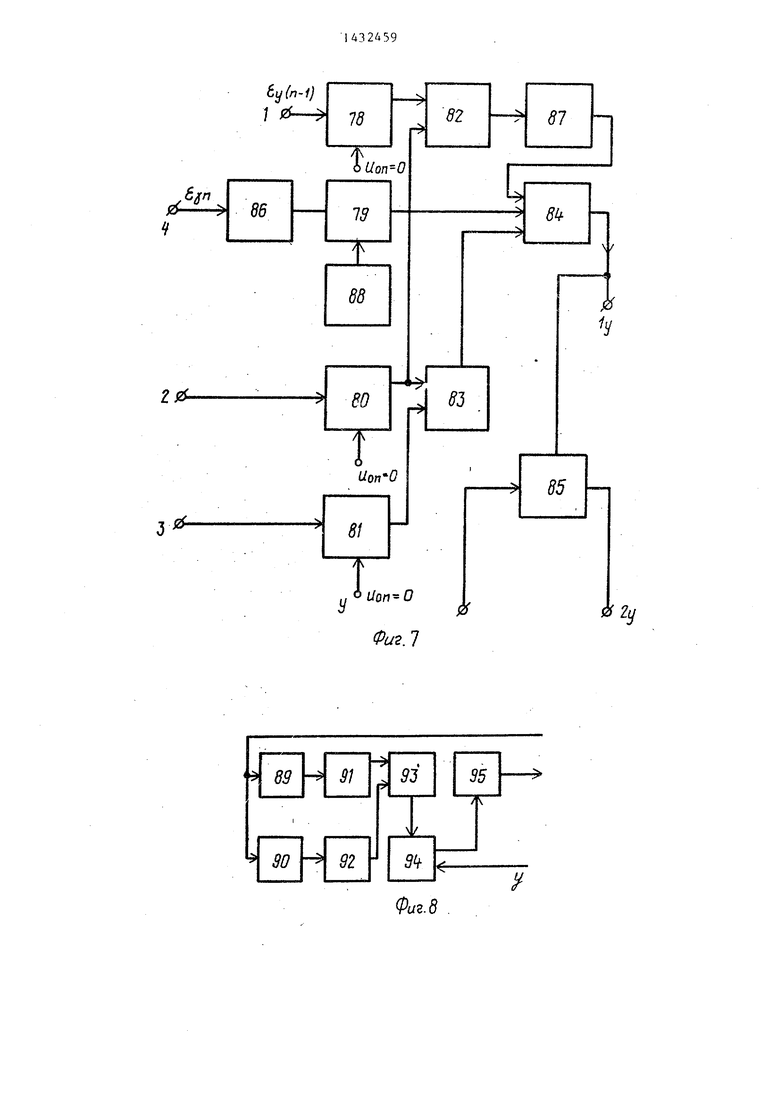

Блок 31 (фиг.9) содержит блоки 96-99 вычитания,/блоки 100-103 деления, блоки 104-110 умножения, тридца- тиканальные блоки 111-113 аналоговых ключей, аналоговые ключи 114 и 115, дешифратор 116, цифроаналоговый преобразователь 117, задатчики 118-121 опорного напряжения, блоки 122-124 уставок, квадратор 125, блок 126 сло

соответственно на аналоговых ключах 46-49, а также интеграторах 54 - 57, схема управления включает в себя генератор 60 тактовых импульсов и блок 61 распределения импульсов.

Регистры работают аналогично, поэтому рассмотрим только работу регистра образованного на ключах 46 и 47 и интеграторах 54 и 55.

Генератор 60 тактовых импульсов посылает на вход блока 61 распределения импульсов управляющие импульсы. Блок 61 распределения импульсов распределяет эти импульсы по выходм, и в соответствии с этим сначала сбрасьгаа- ется в О интегратор 55, затем подключается аналоговым ключом 47 к выходу .интегратора 54. Поскольку подклю

| название | год | авторы | номер документа |

|---|---|---|---|

| Система автоматического управления циклом измельчения | 1983 |

|

SU1357072A1 |

| Адаптивный регулятор | 1982 |

|

SU1076873A1 |

| Система адаптивного управления одностадийным циклом мокрого измельчения | 1987 |

|

SU1480878A1 |

| Система автоматического регулирования загрузки мельницы | 1982 |

|

SU1255207A1 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА КОМБИНИРОВАННОГО РЕГУЛИРОВАНИЯ | 1989 |

|

RU2022313C1 |

| Система автоматического регулирования одностадийным циклом мокрого измельчения | 1982 |

|

SU1255208A1 |

| Адаптивная система регулирования объекта с нестационарной характеристикой,например,дуговой сталеплавильной печи | 1983 |

|

SU1068891A1 |

| Самонастраивающаяся система комбинированного регулирования | 1987 |

|

SU1509828A1 |

| Самонастраивающаяся система комбинированного регулирования | 1986 |

|

SU1339494A1 |

| Самонастраивающаяся система комбинированного регулирования | 1986 |

|

SU1511734A1 |

20

жения, блок 127 постоянной вьщержки времени, восьмой блок .128 сравнения, генератр импульсов, счетчик 130 импульсов.

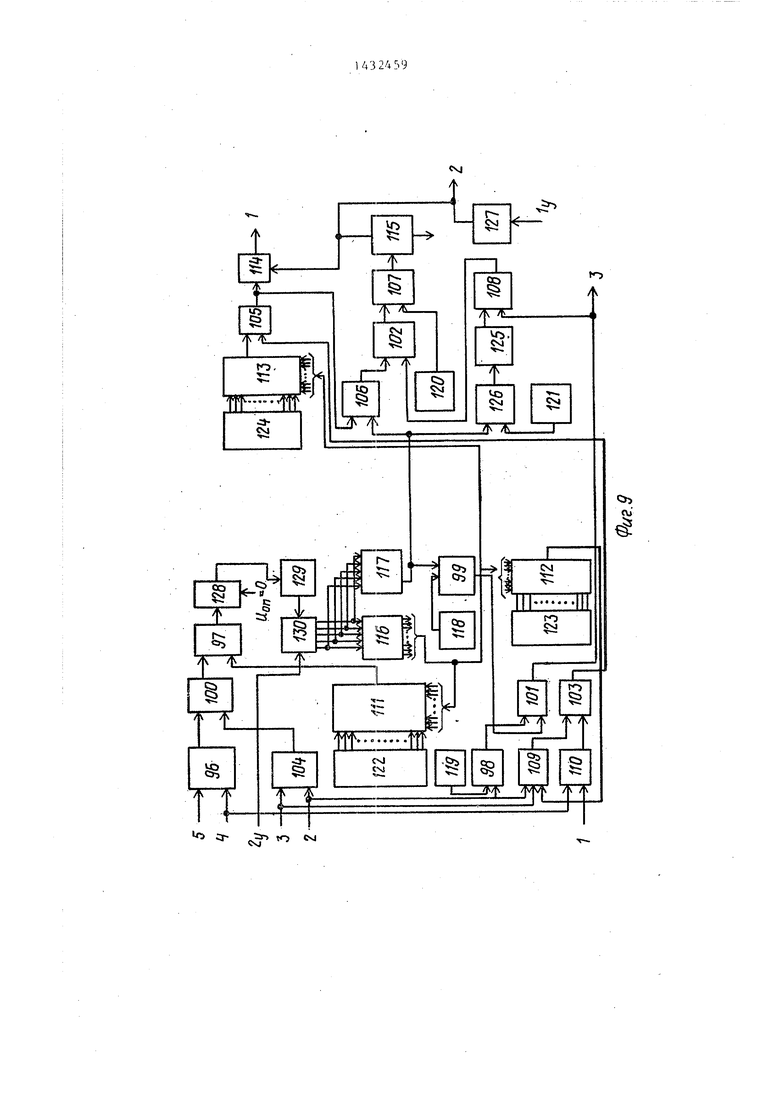

Таймер 41 (фиг.10) содержит аналоговый ключ 131, элемент ИЛИ 132, ни- 25 верторы 133-- 135, интегратор 136, блок- 137 сравнения, задатчики 13.8 и 139 опорного напряжения, элементы И 140 и 141.

Адаптивный регулятор работает еле- 30 ся значение сигналов дующим образом.

Контролируемый сигнал X j(t) посту- торяется, производится перезапись пает на второй вход блока 1 вычитания, значения рВ интегратор 55, а в ин- . на первый вход которого от задатчика

чение производится на фиксированное время, то в интеграторе 55 записьша- ется напряжение, пропорциональное вы ходному напряжению интегратора 54. После закрьдаания ключа 47 обнуляется интегратор 54, а затем с помощью ключа 46 в него записывается очередное значение сигнала рассогласования

п.

Таким образом, в регистре находит

,и „. После окончания последнего этапа цикл повтегратор 54 записьшается новое значение р и т.д.

4 поступает заданное значение X(t), а на выходе формируется сигнал

(t) X2(t) - X(t).

Кроме описанных двух регистров со схемой управления в блок 11 памяти входят две ячейки памяти со схема ми управления и коммутации. В первую 40 ячейку, образованную с помощью ключа 50, интегратора 58 и блока 62 формирования импульса, по сигналу с блока 2 сравнения записьшается значение си нала р, соответствующее значению

Сигнал рассогласования (t), йа- шумленный помехой, поступает на вход фильтра 5 и далее на вход анализатора 30 качества.

Отфильтрованный сигнал .ф(t)

(t) с выхода фильтра 5 поступает дд p(ty) Во второй ячейке, состоящей на входы блока 11 памяти, блока 6 из аналогового ключа 2, интегратора дифференцирования, блоков 15 и 17 умножения, нуль-органа 24 и блока 29.

Величина n(t) перв ой производной

величины .n(t) с выхбда блока 6 диф- Работают обе ячейки аналогичным ференцирования поступает для запоми- образом, поэтому рассмотрим работу

59 «и блока 63 формирования импульса, записьшается по сигналу с блока 29 значение сигнала (0) .

нания на второй информационный вход блока 11 памяти, а также на третий информационный вход блока 29 и на вход блока 7 определения модуля.

Конструктивно блок 11 памяти состоит из двух параллельно включенных двухьячеечнцх сдвиговых регистров, схемы управления. Регистры выполнены

ся значение сигналов

чение производится на фиксированное время, то в интеграторе 55 записьша- ется напряжение, пропорциональное выходному напряжению интегратора 54. После закрьдаания ключа 47 обнуляется интегратор 54, а затем с помощью ключа 46 в него записывается очередное значение сигнала рассогласования

п.

Таким образом, в регистре находит,и „. После окончания последнего этапа цикл повторяется, производится перезапись значения рВ интегратор 55, а в ин-

тегратор 54 записьшается новое значение р и т.д.

Кроме описанных двух регистров со схемой управления в блок 11 памяти входят две ячейки памяти со схемами управления и коммутации. В первую ячейку, образованную с помощью ключа 50, интегратора 58 и блока 62 формирования импульса, по сигналу с блока 2 сравнения записьшается значение сигнала р, соответствующее значению

p(ty) Во второй ячейке, состоящей из аналогового ключа 2, интегратора

p(ty) Во второй ячейке, состоящей из аналогового ключа 2, интегратора

Работают обе ячейки аналогичным образом, поэтому рассмотрим работу

59 «и блока 63 формирования импульса, записьшается по сигналу с блока 29 значение сигнала (0) .

ячейки,образованной аналс-овым ключом 50, интегратором 58 и блоком 62 формирования импульса.

При поступлении с блока 2 сравнения управляющего сигнала блок 62 формирования импульса сбрасьшает интегратор 58, а затем открьшает на фиксированное время ключ 50. Таким образом, в интеграторе 58 значение сигнала р (t )

Управление ячейкой, образованной на аналоговом ключе 52, интеграторе :59 и блоке 63 формирования импульса, производится от блока 29. Записанные в интеграторах 58 и 59 значения сигналов E(t;) и .„(0} с помощью ключей 51 и 53 по сигналу с блока 29 подключаются к пятому информационному входу блока 31, а сигнал (0), кроме этого, и к входу .блока 15 умножения.

Активная идентификация заключается в подаче на вход объекта нормированного скачкообразного воздействия ) ), определяемого в блоке 16 умножения по сигналам от блока 12 памяти и блока 11 памяти по выражению

и.

10

стар где К

(о)-с,

- значение настройки К регулятора на предыдущем шаге идентификации , хранимое в блоке 12 памяти; (0) - величина сигнала рассогласования (t) Хзад X(t) в момент tp подачи скачка, записыаемая в блок 11 памяти по сигналу от блока 29; о( - нормирующий умножитель, устанавливаемый в блоке 16 умножения и анали- эа аналога переходной характеристики объекта. Скачкообразное воздействие (3) подаетсй в момент t, определяемый в блоке 29 при достижении О первой производной E(t(j) величины рассогласования при выполнении следующих логических условий:

1U324596

записьгоается При выполнении условий (4) сигналы с первого блока 29 поступают на первый вход записи блока 11 памяти, управляющие входы блока 16 умножения, аналоговых улючей 21 и 22, блока 26 формирования выдержки времени, вход запуска блока 31 и таймера 25. Блок 29 блокируется до прихода сигнала от триггера 28, разрешающего проведение новой идентификации. Ключ 21 открыт, ключ 22 закрыт.

Сформированный в блоке 16 умножения сигнал (3 ) через открытый анало- 15 говый ключ 21 поступает на второй вход блока 20 сложения, на первый вход которого сигнал не поступает, так как аналоговый ключ 22 закрыт сигналом от блока 29 через инвертор 8.

Блок 29 работает следующим образом.

На вход блока 78 сравнения поступает сигнал с первого выхода блока 11 памяти, на второй вход блока 78 сравнения- подается опорное напряжение

20

(3)

25

оп о второй вход блока 84 эле3 i

ментов И подан модуль заданного значения сигнала рассогласования IE-2.I от блока 88 задания опорного напря30 жения, а на первый вход подаётся сигнал с выхода блока 86 формирования модуля, на вход которого поступает сигнал с выхода фильтра 5, на вход блока 80 сравнения подается сигнал с второго выхода блока 11 памяти, на второй вход блока 80 сравнения подано опорное напряжение Uon О- Выполнение первого условия (4) контролируется блоком 86 формирования

40 модуля, блоком 79 сравнения и блоком 88.

Выполнение второго условия контролируется с помощью блоков 78 и 80 сравнения,, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 82 и инвертора 87. Контроль второго условия производится следующим образом. Пусть в какой-то п-й момент времени на вход блока 29 поступает велиI

(п1

sign &п,, sign .,; sign п 1

где

.2. допустимое значение модуля рассогласования. Процесс идентификации разрешается при выполнении условий (4) и поступлении перед этим сигнала с триггера 28 на блок 29 о завершении предыдущей идентификации, т.е. при переходе фазовой траектории через ось С на фазовой плоскости.

оп о второй вход блока 84

ментов И подан модуль заданного значения сигнала рассогласования IE-2.I от блока 88 задания опорного напря0 жения, а на первый вход подаётся сигнал с выхода блока 86 формирования модуля, на вход которого поступает сигнал с выхода фильтра 5, на вход блока 80 сравнения подается сигнал с второго выхода блока 11 памяти, на второй вход блока 80 сравнения подано опорное напряжение Uon О- Выполнение первого условия (4) контролируется блоком 86 формирования

0 модуля, блоком 79 сравнения и блоком 88.

Выполнение второго условия контролируется с помощью блоков 78 и 80 сравнения,, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 82 и инвертора 87. Контроль второго условия производится следующим образом. Пусть в какой-то п-й момент времени на вход блока 29 поступает вели.(,., . Знак сиг5

0

5

чина рассогласования нала рассогласования n-i определяется с помощью блока 78 сравнения. Если ., Uon 3 выходе блока 78 сравнения формируется сигнал, равный логической единице, а если п-1 и рп, то на выходе этого блока формируется сигнал логического нуля.

Знак величины Е -i определяется аналогичным образом с помощью блока 80 сравнения.

Соответствие знаков сигналов р, и „., проверяется с помощью элемента ИСЮШЧАЮЩЕЕ ШШ 82. При равенстве знаков на выходе элемента 82 будет уровень логического нуля. Этот сигнал через инвертор 87 поступает на вход элемента И 84.

Вьтолнение третьего условия контролируется с помощью блоков 80 и 81 сравнения, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 83. Контроль производится следующим образом. С выхода блока П памяти на вход блока 80 сравнения поступает сигнал n-f который сравнивается в блоке 80 сравнения с опорным напряжением и j . 0. Сигнал- f, с выхода блока 6 дифференцирования поступает на вход блока 81 сра внения, где также сравнивается с опорным напряжением Upi 0. Сигналы с выходов блоков 80 и 81 сравнения поступают на входы элемента 83, на выходе которого в случае неравенства знаков будет уровень логической единицы. Этот сигнал поступает на вход элемента И 84. При выполнении всех трех условий на выходе элемента И 84 будет сигнал, равный логической единице. Сигнал с выхода этого блока поступает на второй зо нения поступает сигнал 0,2 То().

управляющий вход блока 11 памяти и вход элемента И 85,, на второй вход которого поступает сигнал о разрешении начала новой идентификации от RS-триггера 28. Если на обоих входах элемента 85 присутствуют сигналы ло-: гической единицы, с выхода элемента 85, являющегося первьгм выходом блока 29, поступают управляющие сигналы на блок 11 памяти, блок 15 умножения., блок 26 вьщержки времени, блок 31, таймер 25, аналоговый Ключ 21 и инвертор 8, приводя всю схему в состояние новой идентификации параметров объекта регулирования.

Сигнал UCK (3) от блока 20 сложения через блок 17 умножения поступает на выход регулятора и далее на вход объекта. Одновременно с этим по сигналам от блока 29 включается блок

35

40

45

50

При поступлении на входы блока 76 элементов И сигналов на выходе его устанавливается уровень логической единицы, которая поступает на управляющий вход ключа 74, который открьго ется и сигнал поступает на вход интегратора 75, на выходе которого сигнал возрастает по линейному закону. Когда этот сигнал превысит сигнал 0,2 Т)(п-1), на выходе блока 73 сравнения появляется сигнал, равный логической единице. Этот-сигнал сдвигается по отношению к входному н время 0,2 (п-1) .

При исчезновении сигналов на входах блока 76 аналоговый ключ 74 зак- ры ается, а интегратор 75 сбрасьшает ся в нуль с помощью инвертора 77.

В блоке 9 поиска максимума оценивается величина максимального значения модуля производной 1X1, которая поступает на вход блока 10 памяти для запоминания, и далее с его второ го выхода на третий информационный вход блока 31, на второй информацион ный вход которого с первого выхода блока -10 памяти поступает величина t времени достижения модулем произ водной величины рассогласования свое

31, блок 26 формирования вьщержки времени и таймер 25, отмечая начальный

момент времени tg поиска максимума л

1Х I модуля скорости изменения величины В (t), и определяется величина задержки в блоке 26 по сигналу от блока 12, пропорциональному оценке постоянной времени объекта Tj, на пре

дыдущем шаге идентификации. С выхода блока 26 с вьщержкой времени, раиной 0,2 X Tj,(n-l), поступает си1 нал на вход разрешения блока 9 поиска максимума, на первый информационный вход которого поступает текущее значение модуля производной сигнала рассогласования | 1с выхода блока 7 определения модуля.

Таймер 25 работает следующим образом.

При поступлении на управляющий . вход аналогового ключа логической

единицы; сигнал U(,p через ключ 70 поступает на вход интегратора 71, сигнал на выходе которого возрастает пропорционально времени. Сброс интегратора производится по сигналу с выхода нуль- органа 24.

Блок 26 вьщержки времени работает следующим образом.

На вход масштабного блока 72 посту- пает сигнал оценки постоянной времени на предьщущем шаге идентификации Tg(n-l). Масштабный блок 72 имеет коэффицие1 т передачи 0,2, таким образом, на первый вход блока 73 срав5

0

5

0

5

При поступлении на входы блока 76 элементов И сигналов на выходе его устанавливается уровень логической единицы, которая поступает на управляющий вход ключа 74, который открьгоа- ется и сигнал поступает на вход интегратора 75, на выходе которого сигнал возрастает по линейному закону. Когда этот сигнал превысит сигнал 0,2 Т)(п-1), на выходе блока 73 сравнения появляется сигнал, равный логической единице. Этот-сигнал сдвигается по отношению к входному на время 0,2 (п-1) .

При исчезновении сигналов на входах блока 76 аналоговый ключ 74 зак- ры ается, а интегратор 75 сбрасьшает- ся в нуль с помощью инвертора 77.

В блоке 9 поиска максимума оценивается величина максимального значения модуля производной 1X1, которая поступает на вход блока 10 памяти для запоминания, и далее с его второго выхода на третий информационный вход блока 31, на второй информационный вход которого с первого выхода блока -10 памяти поступает величина t времени достижения модулем произ- водной величины рассогласования своекоторое

го.максимального значения, определяется в блоке 9.

Данная величина t л,„, запомненная в блоке 10 памяти, поступает на второй вход блока 2 сравнения, на первый вход которого с выхода масштабного блока 13 поступает сигнал величиной 0,3 () Tj,(n-l), где To(n-l) - оценка постоянной времени Тр объекта на предьщущем (п-1)-м шаге идентификации, хранимая в блоке 12 памяти и определенная в блоке 31.

Блоки 9 и 10 работают.следующим образом.

При появлении сигнала на выходе блока 26 вьщержки времени, который разрешает блоку 9 начать поиск максимума, открьшается.ключ 32 и сбрасьша- ется таймер 41. Сигнал (t) с выхода блока 7 определения модуля поступает на первый вход блока 36 сравнения, а на второй вход поступает сигналI (t)I с выхода фильтра 40, Этот сигнал запаздывает во времени по сравнению с входным сигналом.

В зависимости от этих сигналов на выходе блока 36 сравнения присутствует уровень логического нуля или единицы в соответствии с условиями

(t)l )| О; О, ифп (t)l -1КФП-, (t)l о; 1.

При появлении на выходе блока 36 сравнения уровня логической единицы запускается таймер 41 и производится запись значения , (t) | d (где

Л - порог чувствительности блока 36 сравнения) в блок 10 памяти в ячейку образованную с помощью аналогового ключа 34, интегратора 38 и также блоков формирования импульсов записи 44 и стирания 43. В ячейку, образованную на ключе 35 и интеграторе 39, записы- Бается значение времени t-v.

Блок 31 работает следующим образом,

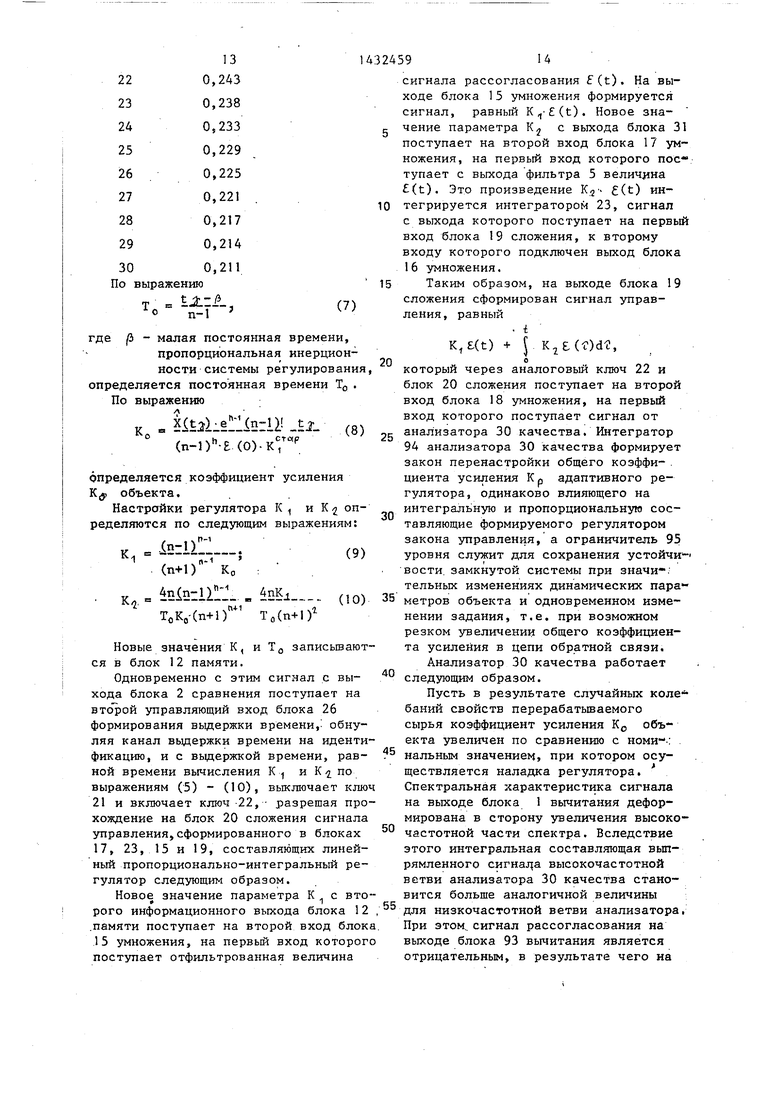

В блоке 122 уставок хранится значение т, определяемое по выражению

m

Г П-, у (nrOSin-l)

fc - -5 -

при изменении п от 1 до 30,

В блоке 123 уставок хранятся значения величины, определяемой по формуле

е Чп-О )h

5

о

5

0

5

при изменении п от 1 до 30.

В блоке 124 уставок хранятся значения величины, определяемой по выражению

(niif: .

(n+l)при изменении п от 1 до 30,

Работа блока 31 заключается в вычислении промежуточного параметра т. По этому значению определяется порядок объекта п,а затем определяются значения Т,- и К, а по этим значениям определяются значения настрой-ки регулАтора К-, и K-j. I

Блок работает в такой последовательности.

По поступающим сигналам f(0), (t..,), X(t-v), t л. с помощью блока 96 вычитания, блока 104 умножения и блока 100 деления определяется значение промежуточного параметра т, который поступает на вход блока 97 вычитания, на второй вход которого поступают поочередно сигналы уставок. Это происходит следующим образом. При поступлении с выхода блока 29 сигнала сбра- сьшается счетчик 130 импульсов. Если разность m-m меньше нуля, то на вы0

ходе блока 128 сравнения присутствует сигнал, разрешающий работу генератора

129импульсов, .которые подсчитьшаются счетчиком 130. Дешифратор 116, управляя работой ключей, входящих в состав блока 111 аналоговых ключей, подключает поочередно уставки т к -входу блока 97 вычитания. Когда разность т-т, стает больше нуля, блок 128 сравнения запрещает работу генератора 129 импульсов. Таким образом, в счетчике

130записьшается число, соответствующее порядку объекта п.

По значениям п, с помощью аадатчиков 118 и 119 опорного напряжения, блоков 98 и 99 вычитания и блока 107 умножения по выражению вычисляется значение напряжения параметра Tg.

С помощью блоков 109 и 110 умноже- ния и блока 103 определяется значение Кд. На входы блока 109 умножения поступают сигналы X,-t,. H сигнал, равный

- -1 (п-1)/(п-1), который поступа- .

0

ёт с блока 123 уставок через блок аналоговых ключей в зависимости от значения, определенного в счетчике 130, На входе блока 103 деления, на который поступают сигналы с блоков 109 и 110 умножения, получают оценку коэффициента усиления объекта Кр.

По полученным значениям п, Кр и Т определяются настройки регулятора К, и К2.

Вычисление К производится с помощью блока 105 умножения, на вход которого поступает сигнал

(n-l) -V(

с блока 124 уставок через блок 113 аналоговых ключей, и сигнал, равный Кд, от блока 103 деления.

Вычисление K-j производится с помощью блоков 106 - 108 умножения, задатчиков 120 и 121 опорного напряжения, блока 102 деления.

Масштабирующий коэффициент блока 13 равен 0,3 (), где п - среднеарифметическое значение порядка п объекта, в рабочем диапазоне изменения технологических, технических, и структурных параметров объекта, изменяющих его порядок п от минималь- /мин

1

него n чения.

до максимального

т,е.

п

/ИНН

+ п 2

мочс

и определяется при первоначальной настройке регулятора..

Если t(n) О.)To(n-l), то управление остается прежним и коэффициенты К и К управления не пересчитьшаются. В обратном случае,

при t,.(n) 0,3(n -l)To(n-l) сигнал с выхода блока 2 сравнения поступает на вход считывания блока 31, вход масштабного блока 14, первый вход записи блока 12 памяти, управляющий вход блока 27 формирования постоянной вьщержки времени, и вход записи блока 11 памяти, в котором дополнительно запоминается величина (t), и совместно с величиной ECt) соответственно с четвертого и третьего информационных выходов блока 11 памяти поступает на пятый и четвертый информационные входы блока 31,

В блоке 31 производится вычисление новых настроек К ., и К регулятора следующим образом.

1А32Д5912

12По и: мереныым величинам f (tj,),

E(t.), X(t,,), t. -) определяется про „ ;

межуточнып параметр т по выражение

-l(t.)-(ti)

X(tj,)-t.j.

m

(5)

Затем по вмражению, аппроксимирующему обратную зависимость п (m), где прямая зависимость имеет вид

n-t

г -1 / . vv / 1 I

f( is fi §E}}L.

(6)

Vio

определяется порядок n объекта, причем принимается ближайтлее целое п.

Результаты расчетов по выражению (6) приведены в таблице, по которой, определив по (5) значение т, выбирается ближайшее п. Если измеренное m по выражению (5) выходит за пределы 0,21.т :1,72, то принимается п, равное 1ти 2 при m pfjcd 5 2, или п 30 при ,21 .

13

220,243

230,238

240,233

250,229

260,225

270,221

280,217

290,214

300,211 о выражению

о

(7)

где р - малая постоянная времени, пропорциональная инерционности системы регулирования,

определяется постоянная времени Т .

По выражению

X(t2)e:-:(n;il tjr ( (0).К

стар

(8)

определяется коэффициент усиления К объекта.

Настройки регулятора К , и К определяются по следующим выражениям:

. П-1

(9)

К,

К

.(п-1)

(n-t-l) Ко

vll-1

lsisiil. . nKi (10)

TcVCn+J)

To(n-fl)

Новые значения К, и Т записьшают- ся в блок 12 памяти.

Одновременно с этим сигнал с выхода блока 2 сравнения поступает на управляющий вход блока 26 формирования вьщержки времени,- обнуляя канал вьздержки времени на идентификацию, и с выдержкой времени, равной времени вычисления К и К по выражениям (5) - (10), выключает ключ 21 и включает ключ-22, разрешая прохождение на блок 20 сложения сигнала управления,сформированного в блоках 17, 23, 15 н 19, составляющих линейный пропорционально-интегральный регулятор следующим образом.

Новое значение параметра К с второго информационного выхода блока 12 , .памяти поступает на второй вход блока. 15 умножения, на первый вход которого поступает отфильтрованная величина

, .

3245914

сигнала рассогласования f (t). На выходе блока 15 умножения формируется сигнал, равный (t). Новое зна- с чение параметра К с выхода блока 31 поступает на второй вход блока 17 умножения, на первый вход которого пос тупает с выхода фильтра 5 велич.ина (t). Это произведение (t) ин- 10 тегрируется интегратором 23, сигнал с выхода которого поступает на первый вход блока 19 сложения, к второму входу которого подключен выход блока 16 умножения.

15 Таким образом, на выходе блока 19 сложения сформирован сигнал управления, равный

. i

K(t) + J (f)di;,

20°

который через аналоговый ключ 22 и

блок 20 сложения поступает на второй вход блока 18 умножения, на первый вход которого поступает сигнал от 2с анализатора 30 качества. Интегратор 94 анализатора 30 качества формирует закон перенастройки общего коэффи- . циента усиления К р адаптивного регулятора, одинаково влияющего на интегральную и пропорциональную составляющие формируемого регулятором закона управления, а ограничитель 95 уровня служит для сохранения устойчи- вости. замкнутой системы при значи-.- тельных изменениях динамических метров объекта и одновременном изменении задания, т.е. при возможном резком увеличении общего коэффициента усиления в цепи обратной связи.

Анализатор 30 качества работает следующим образом.

Пусть в результате случайных коле- баний свойств перерабатьшаемого сырья коэффициент усиления К объекта увеличен по сравнению с

30

35

40

45

50

55

нальным значением, при котором осуществляется наладка регулятора. Спектральная характеристика сигнала на выходе блока 1 вычитания деформирована в сторону увеличения высокочастотной части спектра. Вследствие этого интегральная составляющая вьш- рямленного сигнад а высокочастотной ветви анализатора 30 качества становится больще аналогичной величины для низкочастотной ветви анализатора, При этом., сигнал рассогласования на выходе блока 93 вычитания является отрицательным, в результате чего на

выходе интегратора 94 получается от- , рицательное приращение коэффициента , усиления регулятора. Уменьшение коэффициента усиления объекта приводит к .увеличению низкочастотной составляющей спектра на входе анализатора 30, что, в свою очередь, вызьшает уменьшение рассогласования по абсолютной величине и уменьшение, скорое- ти изменения настроившегося коэффициента усиления регулятора. Перестройка последнего прекращается в случае баланса интегральных составляющих низкочастотной и высокочастотной частей спектра сигнала, что соответствует сохранению в основном контуре заданного запаса устойчивости, определяемого расчетными значениями параметров К и К управления U(t), и приближен- ной минимизации среднего квадрата ошибки сложения. Фильтр 5 влияет также на запас устойчивости, поддерживаемый в основном контуре.

Одновременно с зтим текущее время регулирования t с выхода таймера 25 поступает на второй вход блока 3 сравнения, на первый вход которого с выхода масштабного блока 14 поступает сигнал, равный ЗТд, где 3 - коэффициент масштабирования блока 14, а Т, - величина оценки постоянной времени, поступающая с первого выхода блока 12 памяти. Во всех режимах, если , t ЗТо ,, сигнал от блока 3 сравнения поступает на R-вход RS-триггера 28, который по управляющему входу блока 29 разрешает проведение новой идентификации и фиксирует окончание предьщу- щей. При этом сигнал f(t) с выхода фильтра 5 поступает на вход нуль-органа 24, фиксирующего близость нулю величины (t), т.е. окончание процес- .са регулирования при апериодическом его характере, что определено видом расчетных выражений (9) и (10) и логикой идентификации параметров Ко, TO и п.

Выходной сигнал нуль-органа 24 поступает на входы сброса ннтеграто- ра 23, таймера 25, вход записи блока 1О памяти и управляющий вход анализатора 30 качества, приводя их в исходное состояние, обнуляя интеграторы этих блоков.

Адаптивный регулятор полностью приведен в состояние готовности, как и к парированию возможного рассогласования E.(t), так и к идентификации параметров Тр, К и п объекта и адаптации своих настроек К, и К2.

Управление технологическими процесами обогащения с помощью предлагаемого адаптивного регулятора повышает достоверность информации, используемой при выработке управляющих воздействий, по сравнению с известным, что позволяет повысить объем производимой товарной продукции на 0,4% при одновременном снижении потерь полезного компонента на 0,4%.

Формула изобретен -и я

Адаптивный регулятор, содержащий первый блок сложения, первый аналоговый ключ, RS-триггер, блок вычитания подключенный первым и вторым входами соответственно к выходу задатчи- ка и к входу адаптивного регулятора, а выходом через фильтр - к первому информационному входу первого блока памяти, первому входу первого блока умножения и через последовательно соединенные блок дифференцирования и блок определения модуля - к первому информационному входу блока поиска максимума, первый и второй выходы первого блока памяти соединены с пер- вым и вторым информационными входами блока контроля вьтолнения логических условий, третий информационный вход которого подключен к второму информационному входу первого блока памяти и выходу блока дифференцирования, информационный вход первого блока формирования выдержки времени соединен с первым выходом второго блока памяти и через первый и второй масштабные блоки - с первыми входами соответственно первого и второго блоков сравнения, второй вход второг блока сравнения подключен к выходу таймера, соединенного входом управления запуском с первым выходом блок контроля выполнения логических условий, управляющим входом второго блока умножения и первым управляющим входом первого блока формирования выдержки времени, выход которого подключен к входу разрешения блока поиска максимума, выход первого блока сравнения соединен с входом считьша- ния блока вычисления коэффициентов настройки регулятора и с первым входом записи второго блока памяти, подключенного вторым выходом к первым информационным входам второго блока

1714

умножения и блока вычисления коэффи- пиентов настройки регулятора, первый выход которого соединен с первым информационным входом второго блока памяти и вторым входом первого блока умножения, подключенного первым I входом к первому входу третьего бло |ка умножения, второй и третий выходы Iблока вычисления коэффициентов наст- ройки регулятора соединены соответственно с йторым информационным входом второго блока памяти и вторым входом I третьего блока умножения, подключенного выходом через интегратор к первому входу второго блока сложения, второй вход которого соединен с выходом первого блока умножения, отличающийся тем, что, с целью повышения качества регулирования, введены второй блок формирования выдержки времени, третий блок памяти, второй аналоговый ключ, четвертый блок умножения, инвертор, нуль-орган и анализатор качества, информационный вход которого подключен к выходу блока вычитания, управляющий вход - к входу записи третьего блока памяти, входу сброса интегратора, входу сброса таймера и выходу нуль-орга- на, соединенного входом с первым входом третьего блока умножения, а выход - к входу четвертого блока умножения, соединенного вторым входом с выходом первого блока сложения, а выходом - с выходом адаптивного регулятора, первый выход блока контроля выполнения логических условий подключен к первому входу записи первого блока памяти, управляющему входу пер- вого аналогового ключа и через инвертор - к управляющему входу второго аналогового ключа, соединенного информационным входом с выходом второго блока сложения, а выходом - с первым входом первого блока сложения, второй вход которого подключен к выходу пер

0

5

0

зо Q,j

25

35

)918

вого аналогового ключа, соединенного входом с выходом второго блока умножения, выход второго блока сравнения подключен к входу установки в нулевое состояние RS-триггера, подключенного входом установки в единичное состояние к выходу второго блока формирования вьщержки времени, а выходом - к входу разрешения блока контроля выполнения логических условий, второй выход которого соединен с входом считывания первого блока памяти, подключенного вторым входом записи к управляющему входу второго блока формирования вьдержки времени, второму управляющему входу первого блока формирования выдержки времени и выходу первого блока сравнения, второй вход которого соединен с вторым информационным входом блока вычисления коэффициентов настройки регулятора и первым информационным выходом третьего блока памяти,. подключенного вторым информационным выходом к третьему информационному входу блока вычисления коэффициентов настройки регулятора и второму информационному входу поиска максимума, три выхода которого соединены с соответствующими входами третьего блока памяти, подключенного четвертым информационным входом к выходу таймера, третий выход первого блока памяти соединен с вторым информационным входом второго блока умножения и четвертым информационным входом блока вычисления коэффициентов настройки регулятора, подключенного пятым информационным входом к четвертому выходу первого блока памяти, входом запуска к входу запуска таймера и управляющим выходом к второму-входу записи второго блока памяти, а выход фильтра соединен с четвертым информационным входом блока контроля вьтолнения логических .условий.

Ч

Фиг.6

еу{п-1}

1 fzf-fZf81

78

82

87

/

,«3

y

Uon-G

85

I

Фиг. 7

0 2tj

Фаг. 8

fл сг- ,- csi

съ

Фиг.Ю

Авторы

Даты

1988-10-23—Публикация

1987-01-26—Подача