выход которого соединей с третьим входом первого блока памяти, четвертый вход которого и первый вход третьего блока умножения соединены с вторым выходом вычислителя, к пятому входу которого подсоединен выход первого масштабного блока, второй выход логического блока соединен с вторым входом второго блока умножения, к третьему входу которого подсоединен первый вход вьпислителя, а второй выход второго блока умножения соединен с шестым входом вычислителя и с вторым входом первого блока сложения, выход которого соединен с вторым входом третьего блока умножения, выход которого соединен с входом интегратора,, второй вход первого блока умножения соединен с первым выходом вычислителя, выход третьего маса1табного блока соединен с вторым выходом второго блока сравнения, выход второго задатчика соединен с первым входом четвертого блока сравнения, к другому входу которого подключен выход первого блока опреде- ления модуля, а выход четвертого блока сравнения соединен с вторым входом адаптивного регулятора, выход которого соединен с выходом второго блока сложения .

| название | год | авторы | номер документа |

|---|---|---|---|

| Система автоматического регулирования загрузки мельницы | 1982 |

|

SU1255207A1 |

| Система адаптивного управления одностадийным циклом мокрого измельчения | 1987 |

|

SU1480878A1 |

| Система автоматического управления циклом измельчения | 1983 |

|

SU1357072A1 |

| Система автоматического регулирования одностадийным циклом мокрого измельчения | 1982 |

|

SU1255208A1 |

| Система управления измельчительным агрегатом | 1982 |

|

SU1101302A1 |

| Адаптивный регулятор | 1987 |

|

SU1432459A1 |

| Адаптивный регулятор | 1980 |

|

SU911462A1 |

| Система регулирования загрузки измельчительного агрегата | 1983 |

|

SU1146085A1 |

| Система автоматического управления измельчительным агрегатом | 1982 |

|

SU1052259A1 |

| Самонастраивающаяся система автоматического управления процессом мокрого измельчения | 1981 |

|

SU1018106A1 |

АДАПТИВНЫЙ РЕГУЛЯТОР, содержащий первый блок сложения, первый задатчик, соединенный с первым входом первого блока сравнения, первый блок определения модуля, первый и второй масштабные блоки, первый блок умножения, логический блок, блок формирования выдержки времени, последовательно соединенные вычислительный блок и первый блок памяти, первый выход которого соединен с первым входом вычислительного блока, последовательно соединенные фильтр, блок дифференцирования, второй блок определения модуля и амплитудный детектор, к другому входу которого подсоединен выход блока формирования выдержки времени, выход блока дифференцирования соединен с первым входом логического блока, отличаю.щ и и с я тем, что, с целью повышения точности регулирования и улучшения качества формируемого переходного процесса, он содержит второй задатчик , третий масштабный блок, второй , третий и четвертый блоки сравнения, второй блок памяти, таймер, триггер, ключ, второй и третий блоки умножения, второй блок сложения, интегратор, выход которого соединен с первым входом второго блока сложения, к другому входу которого подсоединен выход первого блока умножения , первый вход которого соединен с выходом фильтра и с первыми входами первого блока сложения, второго блока умножения, второго блока памяти и первого блока определения модуля, к входу фильтра подключен выход пер вого блока сравнения, выход амплитудного детектора соединен с входом триггера и первым входом первого масштабного блока, к другому входу которого подсоед :нен первый выход Q триггера, второй выход которого сое-9 динен с первым входом таймера, к гому входу которого подсоединен пер- %f/ вый выход второго блока умножения, «в соединенный также с первым входом jtei блока фop мpoвaния выдержки времени, а к другому входу которого, а также к второму входу вычислителя, к перво ;; му входу второго масштабного блока и к входу третьего масштабного блока подсоединен второй выход первого блока памяти, к второму входу которого и к третьему выходу вычислителя подО соединен первый выход второго блока сравнения,другой выход которого сое00 динен с вторым в ходом второго масштаб ч1 ного блока, выход которого соединен с первым входом третьего блока сравМ нения, другой вход которого, а также первый вход второго блока сравнения и четвертый выход вычислителя | соединены с выходом таймера, выход третьего блока сравнения соединен с первым входом ключа, выг{од которого соединеи с вторым входом второго блока памяти, третий вход которого соединен с выходом блока дифференцирования, а выходы второго блока памяти соединены с вторым и третьим входами логического блока, первый

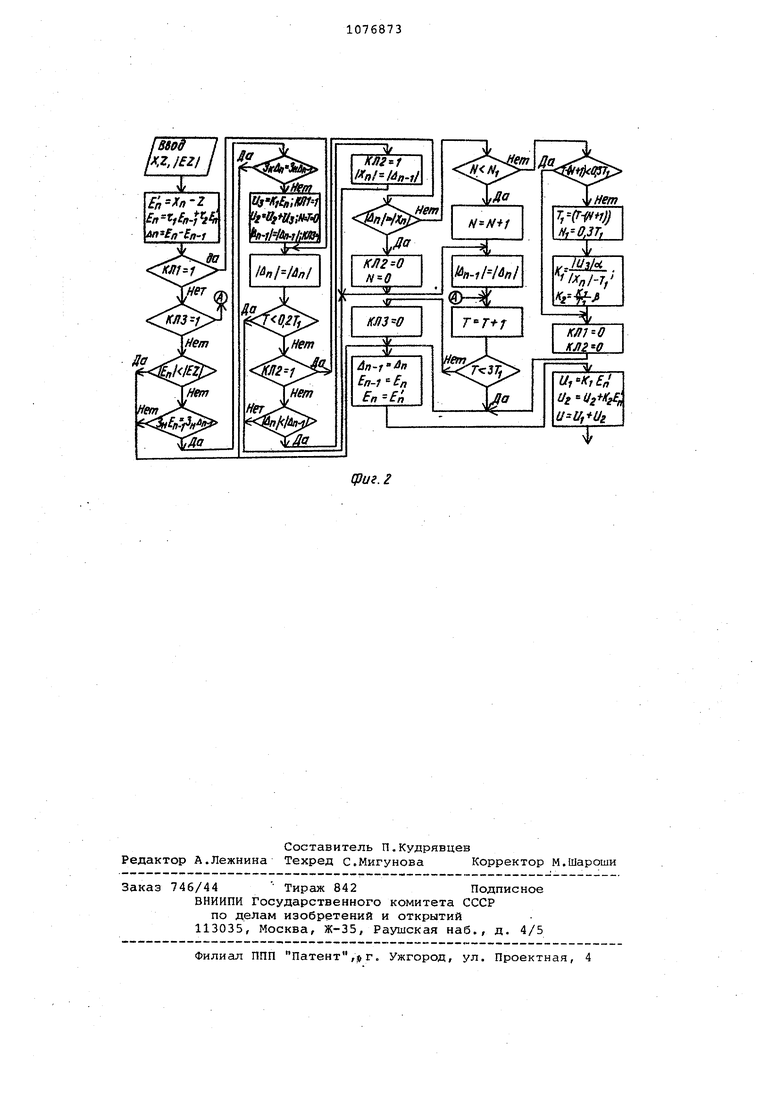

Изобретение относится к аналоговым устройствам автоматики и может быть использовано для управления нестационарными объектами в металлур гической, химической, горнообогатительной, строительной, угольной пролышленности в условиях дрейфа статических и динамических характеристик, вызванного изменением качества перерабатываемого сырья и состоянием тех нологического оборудования. Известен адаптивный регулятор, содержащий формирователь управляющего воздействия, последовательно соединенные элемент сравнения, первый блок определения модуля, первый фильтр, первый дифференциатор, второ блок определения модуля и амплитудный детектор JНедостатки указанного регулятора - низкая точность и неудовлетвори тельное качество переходного процесса. Наиболее близким к предлагаемому является адаптивный регулятор, содержащий первый сумматор, первый ззшатчик, соединенный с первым входом первого блока сравнения, первый блок определения модуля, первый и второй масштабные блоки, первый блок умножения, логический блок, блок фор мирования выдержки времени, последовательно соединенные вычислитель«ый блок и первый блок памяти, первый вы ход которого соединен с первым входом вычислительного блока, последевательно соединенные фильтр, блок дифференцирования, второй блок определения модуля и адаптивный детектор к другому входу которого подсоединен выход блока формирования выдержки вр времени, выход блока дифференцирования соединен с первым входом логичес кого блока , 2. К недостаткам известного адаптивного регулятора относятся низкие точность и качество регулирования, вызванные нечетом изменяющихся динамических параметров, длительным временем идентификсщии, а также невысокое качество переходного процесса в связи с малой помехозащищенностью. Цель изобретения - повьапение точности регулирования и улучшение качества формируемого переходного процесса. Поставленная цель достигается тем, что в адаптивный регулятор, содержащий первый блок сложения, первый задатчик, соединенный с первым входом первого блока сравнения, первый блок определения модуля, первый и . второй масштабные блоки, первый блок умножения, логический блок, блок формирования выдержки времени, последовательно соединенные вычислительный блок и первый блок памяти, первый выход которого соединен с первым входом вычислительного блока, последовательно соединенные фильтр, блок дифференцирования, второй блок определения модуля и амплитудный детектор, к другому входу которого подсоединен выход блока формирования выдержки времени, выход блока дифференцирования соединен с первым входом логического блока, дополнительно введены второй задатчик, третий масштабный блок, второй, третий и четвертый блоки сравнения, второй блок памяти, таймер, .триггер, клю второй и третий блоки умножения, второй блок сложения, интегратор, выход которого соединен с первым входом второго блока сложения, к другому входу которого подсоединен выход первого блока умножения, первый вход которого соединен с выходом фильтра и с первыми входами первого блока сложения, второго блока умножения, второго блока памяти и первого блока определения модул к входу фильтра подключен выход первого блока сравнения, выход амплитудного детектора соединен с входом триггера и первым входом первого мас штабного блока, к другому входу которого подсоединен первый выход триг гера, второй выход которого соединен с первым входом таймера, к другому входу которого подсоединен первый выход второго блока умножения, соединенный также с первым входом блока формирования выдержки времени, к дру гому входу которого, а также к второму входу вычислителя, к первому входу второго масштабного блока и к входу третьего масштабного блока под соединен второй выход первого блока памяти, к второму входу которого и к третьему выходу вычислителя подсоединен первый выход второго блока сравнения, другой выход которого сое динен с вторым входом второго масшта ного блока, выход которого соединен с первым входом третьего блока сравнения, другой вход которого, а также первый вход второго блока сравнения и четвертый выход вычислителя соединены с выходом таймера, выход третьего блока сравнения соединен с тервым входом ключа, выход которого соединен с вторым входом вто-; рого блока памяти, третий вход которого соединен с выходом блока дифференцирования, а выходы второго блока памяти соединены с вторым и третьим входами логического блока, первый выход которого соединен с . третьим входом первого блока памяти, четвертый вход которого и первый вхо третьего блока умножения соединены с вторым выходом вычислителя, к пятому входу которого подсоединен выход первого масштабного блока, второй выход логического блока соединен с вторым входом второго блока умножения, к третьему входу которого под соединен первый вход вычислителя, а второй выход второго блока умножения соединен с шестым входом вычислителя и с вторым входом первого блока сложения, выход которого соединен с вхо дом третьего блока умножения, выход которого соединен с входом интегратора, второй вход первого блока умно жения соединен с первым выходом вычи лителя, выход третьего масштабного блока соединен с вторым выходом второго блока Сравнения, выход второго эадатчика.соединен с. первым входом четвертого блока сравнения, к другому входу которого подключен выход пе вого блока определения модуля, а выход четвертого блока сравнения соединен с вторым входом адаптивного регулятора, выход которого соединен с выходом второго блока сложения. На фиг. 1 представлена функционгшь ная схема адаптивного регулятора на фиг. 2 - гшгоритм, реализующий управление объектом с помо111ью гшаптивного регулятора. Регулятор содержит первый блок 1 сложения, первый задатчик 2, первый блок 3 сравнения, первый блок 4 определения модуля, первый и второй масштабные блоки 5 и 6, первый блок 7 умножения, логический блок 8, блок 9 формирования выдержки времени,, вычислительный блок 10, первый блок 11 памяти, фильтр 12, блок 13 дифференцирования , второй блок 14 определе- . ния модуля, амплитудный детектор 15, второй задатчик 16, третий масштабный блок 17, второй 18, третий 19 и четвертый 20 блоки сравнения, второй блок 21 памяти, таймер 22, триггер 22, триггер 23, ключ 24, второй 25 и третий 26 блоки умножения, второй блок 27 сложения и интегратор 28. Регулятор работает следующим образом. Контролируемый сигнал Хр и его заданное значение Z поступают на первый блок 3 сравнения, сигнал на выходе которого защемленный помехой, поступает на вход фильтра 12. Отфильтрованный сигнал Е„ поступает на первый блок 4 определения модуля и через блок 13 дифференцирования «а второй блок 14 определения модуля. Сигналы с блоков 12 и 13 записываются на второй блок 21 памяти. Адаптивный регулятор предназначен для управления нестационарными объектами с переменными статическими и динамическими характеристиками путем формирования управляющего воздействия вида U((t)tKJe(t|cilt U +U . о E(i) (фиг.2) определяется по вы-, ражению SEn-i- ziV- l . (2) где п , п-1 - моменты дискретного времени; - постоянные фильтра 12. Фильтр 12 представляет собой рекурсивный цифровой фильтр первого порядка и может быть реализован по известном схеме ГзЗ. В непре млвном случае вырежение (2) эквивалентно низкочастотному КС-фильтру. Передаточная функция такого фильтра иые&т вид -gfPl. Е(Р)

откуда дифференциальное уравнение фильтра может быть записано как

в дискретном случав, используя в качестве дифференциала первую раз- 5 HOCTbj получим

T/E-F l-t-E -Е n-W I

откуда

e

n T+-) -n

Введя обозначения ,f и -f;i Т2, получим выражение (2),

Коэффициенты К и К - настроечны параметры регулятора, определяемые В:процессе активной идентификации в вы ислителе 10. Активная идентификация заключается в подаче на вход объекта нормированного скачкообразного воздействия U, определяемого во втором блоке 25 умножения по сигнала от первого блока 11 памяти и фильтра 12. Скачкообразное воздействие Uj подается в момент tg, определяеМЕЛИ в логическом блоке 8 из условия достижения нулю первой производной ECtfl) величины рассогласования (2), путем оценки положения системы на фазовой плоскости (Е, Е). Процесс индентификации начинается при переходе фазовой траектории через ось Е, при выполнении следующих логических условий (фиг.2), осуществляемых в логическом блоке 8,

1Еп : / EZ/J(3)

Знак ЕП-Т , (4)

Знак Е„ Знак Ё„ , (5)

где /Ег/ - допустимое значение модуля рассогласования.

При выполнении условий (3). - (5) сигналы с логического блока 8 поступают на управляющие входы первого блока 11 памяти и блока 25 умножения Логический блок блокируется до прихода следующего сигнала от блоков 24 и 14. Величина К(п-11 поступает с первого выхода блока 11 памяти на третий вход блока 25, а сформирован ное в блоке 25 скачкообразное тести рующее воздействие подается на первый блок 1 сложения, на блок 9 формирования выдержки времени и на таймер 22, отмечая начальный момент времени tp поиска максимума /Лп/ (фиг.2) модуля скорости изменения отклонения Е,,.

Сигнсш с выхода блока 15 поступает на управляющий вход блока 9 фор мирования выдержки времени, на другой вход которого с выхода первого блока 11 памяти подается величина Т, обратно пропорциональнаА предыдущему значению динамического параметра Kx(n-l). С выхода блока 9 с выдержкой времени равной Т,( поступает сигнал на управляющий вход амплитудно1о детектора 15, на второй вход которого подается текущее значение модуля производной сигнала рассогласования /ёп/ от второго блок 14 определения модуля,

В блоках 1,26,7,28 и 27 по сигналам от блоков 10,11 и 12 формируется управляющее воздействие U (фиг,2 вида

и К(п-1)ЕЧк2(п-) K(n-1|E Jdt, (6)

которое с выхода блока 27 поступает на объект рассогласования. I В амплитудном детекторе оценива(ется величина максимального значения модуля производной /Хп/(фиг.2), которая поступает на триггер 23 и на первый масштабный блок 5, Сигнал с выхода-триггера 23 подается на таймер 22, фиксируя момент окончания поиска максимума , и на второй С управляющий вход масштабного блока 5. На выходе блока 5 формируется величина максимального значения модуля производной с учетом перехода . объекта на правую ветвь экстремальной характеристики путем умножения величины значения /Ё , при котором сработали амплитудный детектор 15 и Tptirrep 23, на постоянный множитель (1+2р), где 2Г величина порога различимости при поиске максимума в амплитудном детекторе 15.

На выходе таймера 22 формируется новое значение параметра, которое поступает на вычислитель 10, второй блок 18 сравнения и третий блок 19 сравнения.

На второй блок 18 сравнения поступает величина 0,3 T(.n-i; от трет третьего масштабного блока. Если Т(п)СО,3. Т,, (h-1) {фиг. 2), то управление остается прежним и коэффициенты К и К регулятора не пересчитываются. Если Т(п)0,3 T(n-l), то сигнал с выхода блока 18 поступает на управляющие входы блока 11 памяти и вычислителя. В вычислителе 10 происходит определение новых значений коэффициентов К2 и К-, (фиг. 2) по сигналам от блоков 11, 22 и 5 по выражениям:

. / ,

,|Г,(п)

к (ш

К )

Г (п1

где и /5 - постоянные коэффициенты, определяемые при первоначальной настройке гщаптивного регулятора;

(п) и К2(п) - новые значения коэфК

фициентов пропорциональной и интегральной составляющей ПИ-закона регулирования;

К(п-1)/Е„/

- величина скачкообразного возмущающего воз-Ю действи.

Новые значения К

L и Kg и .Т записываются в блок 11 памяти и поступаю на блоки 26, 1, 7 и 27 для формирования управляющего воздействия по выражению (1).

Одновременно с этим сигнал с выхода второго блока 18 сравнения поступает на управляющий вход блока 6, на второй вход которого подается от блока 11 памяти старое значение T,(h-l).

В третьем блоке 19 сравнения сравниваются величины Т|(п) от блока 22 и ЗтЛп-1) от блока 6. Если Т(п) зт, (n-l), то сигйал с блока 19 поступает на ключ 24, разрешая проведение новой идентификации. Введение блоков 6,17,18,19;и 24 (повышает помехозащищенность при определении коэффициентов и устраняет выработку ложных управлений адаптивным регулятором, повышая качество формируемого переходного процесса.

Управление технологическими процессами обогащения с помоцью предлагаемого адаптивного регулятора повышает достоверность информации, используемой при выработке управляющих воздействий, что позволит повысить объем производимой товарной продукции на 0,3% при одновременном снижении потерь полезного компонента на 0,4%. Экономический эффект от внедрения составит 20 тыс.руб. на одну технологическую секцию.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приборы и систег-ы управления | |||

| М., 1974, № 1, с | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Измерение и анализ случайных процессов | |||

| М., Мир | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Чемодан с сигнальным замком | 1922 |

|

SU338A1 |

Авторы

Даты

1984-02-28—Публикация

1982-04-23—Подача