, Изобретение относится к области автоматического управления процессами измельчения и классификации при обогащении полезных ископаемых и может быть использовано на обогатительных фабриках цветной и черной металлургии при переработке руд с изменяющимися физико-механическими и текстурно-структурными свойствами, а также в условиях дрейфа статических характеристик технологических агрегатов, вызванного их износом.

Известна система автоматического, управления циклом измельчения, содержащая датчик и задатчик крупности соединенные с входами блока сравнения , последовательно соединенные первьй блок опр еделення модуля, пер- вьШ фильтр, блок дифференцирования, второй блок определения модуля, ампл тудньш детектор, вьиислительное устройство, блок памяти, блок умножения, регулятор, исполнительный механизм, задвижку, причем выход первого фильтра через ограничитель и масштабные блоки соединен с вторым входом вычислителя, к третьему входу которого подключен выход блока памяти, второй вход которого через логический блок и блок формирования вьщержки вр мени соединен с выходом блока дифференцирования, а выход блока формирования вьщержки времени соединен с другими входами логич еского блока и амплитудного детектора 1 .

Недостатком известной системы управления является невысокое качество управления, вызванное незгчетом изменяющихся динамических свойств, т.е. постоянной времени в передаточной функции объекта управления, а также невысокое качество переходного про- цес.са в связи с тем, что изменение статических характеристик объекта управления определяется только в моменты резкого, значительного изменени свойств перерабатываемого сырья. В . случае медленно изменяющихся динамических и статических характеристик в передаточной функций объекта регулирования известная система не обеспечивает высокого качества управления .

Наиболее близкой по технической сущности является система автоматического управления циклом измельчения, содержащая регулятор, четыре блока сравнения, два блока определе

5

0

д

5 30

ния модуля, фильтр, блок дифференцирования, амплитудньй детектор, три масштабных блока, вычислитель, два блока памяти, блок умноже:ния, логический блок, блок формирования вьщерж- KI времени, триггер, таймер, первьш ключ и задатчик модуля отклонения, причем выход первого блока сравнения соединен с входом фильтра, вихо- ды которого соединены с входами блока дифференцирования, первого блока определения модуля, с первыми входами блока з множения, первого блока памяти и регулятора, выход блока дифференцирования через второй блок определения модуля подключен к первому входу амплитудного детектора, к второму входу первого блока памяти и к первому входу логического блока, выход амплитудного детектора соединен с входом триггера и с первым входом nepBdro масштабного блока, выход ко- торого подключен к первому входу вычислителя, выход триггера соединен с вторым входом первого масштабного блока и с первым входом таймера, выход первого блока памяти соединен с вторым входом логического блока, выход логического блока соединен с вторым входом блока умноженияi вторым входом таймера, выход которого соединен с вторым входом вычислителя, третий вход которого соединен с выхо 2g дом второго блока определения модуля, четвертьй вход вычислителя соединен с первым выходом второго .блока памяти, первьй ВХОД которого соединен с первым выходом вычислителя, пятьй вход вычислителя соединен с вторым выходом второго блока памяти, второй вход которого соединен с выходом логического блока, третий вход второго блока памяти и шестой вход в)1числи- теля соединены с выходом второго блока сравнения, первый вход которого соединен с первым входом третьего , блока сравнения и с выходом таймера, второй выход вь1числителя Соединен с четвертым входом второго блока памяти, первьй выход которого подключен к третьему входу блока умножения, выход второго блока сравнения соединен с первым входом второго масштаб g ного блока, второй выход которого соединен с вторым входом третьего блока сравнения, входы второго и тре тьего масштабных блоков соединены с . вторым выходом второго блока памяти.

40

45

50

выход третьего масштабного блока соединен с вторым входом второго блока сравнения, выход третьего блока сравнения соединен с первым входом первого ключа, второй вход которого сое динен с выходом четвертого блока сравнения, входы четвертого блока сравнения подключены к задатчику модуля отклонения и к выходу первого блока определения модуля, выход пер- вого ключа соединен с вторым входом первого блока памяти, первый и второй выходы вычислителя соединены с первым и вторым входами регулятора, а выход фильтра соединен с третьим входом регулятора 2.

Недостатком известной системы является невысокое качество управления, вызванное неразделенностью во времени процессов поиска оптимальных значений управляющих воздействий и собственно управления процессом из- мельчейия.

Цель изобретения - повьшение точности управления.

Система автоматического управления циклом измельчения, содержащая регулятор, четыре блока сравнения, два блока определения модуля, фильтр, бло дифференцирования, амплитудньй детектор, три масщтабных блока, вычислитель, два блока памяти, блок умножения, логический блок, блок формирования вьщержки времени, триггер, таймер, первый ключ, задатчик модуля отклонения, причем выход первого блока сравнения соединен с входом фильтра, выходы которого соединены с входами блока дифференцирования, первого блока определения модуля, с первыми входами блока умножения, первого блока памяти и регулятора расхода воды, выход блока диффе|)енцирования через вто15ой блок определения модуля подключен к первому входу амплитудного детектора, к второму входу первого блока памяти и к первому входу логического блока, выход амплитудного детектора соединен с входом триггера и первым входом первого масштабного блока, вькод которого подключен к первому входу вычислителя, выход триггера соединен с вторым входом первого масштабного блока и с первым входом таймера, выход первого блока памяти соединен с вторым входом логического блока, выход логического блока соединен- с вторым входом блока

умножения, вторым входом таймера, выход которого соединен с вторым входо вычислителя, третий вход- которого содинен с выходом второго блока определения модуля, четвертьй вход вычислителя соединен с первым выходом второго блока памяти, первый вход которого соединен с первым выходом вычислителя, пятьй вход вычислителя содинен с вторым выходом второго блока памяти, второй вход которого соединен с выходом лог ического блока, третий вход второго блока памяти и шестой вычислителя соединены с выходом второго блока сравнения, первый вход которого соединен с первым входом третьего блока сравнения и с выходом таймера, второй выход вычислителя соединен с четвертым входом второго блока памяти, первый выход которого подключен к третьему входу блока умножения, выход второго блока сравнения соединен с первым выходом второго масштабного блока, второй выход которого соединен с вторым входом третьего блока сравнения, входы второго и третьего масштабных блоков соединены с вторым выходом второго блока памяти, выход третьего масштабного блока соединен с вторым йходом второго блока сравнения, выход третьего блока сравнения соединен с первым входом первого , второй вход которого соединен с. выходом четвертого блока сравнения, входы четвертого блока сравнения подключены к з,адатчи- ку модуля отклонения и к выходу первого блока определения модуля, выход первого ключа соединен с вторым входом первого блока памяти, первый и второй выводы вычислителя соединены с первым и вторым входами регулятора, а выход фильтра соединен с третьим входом регулятора, снабжена вторым ключом, датчиком и задатчиком крупности и исполнительным механизмом задвижки, интегратором и блоком сложения, причем выход блока умножения соединен с первым входом интегратора, выход которого соединен с первым входом блока сложения, к второму входу которого подключен выход второго ключа, первый вход которого соединен с ВЫХОДОК}, регулятора, а второй вход второго ключа соединен с выходом логического блока, выход таймера соединен с вторым входом интегратора, выход блока сложеЯия соединен с

вгсодом исполнительного механизма задвижки, а датчик и задатчик крупности Соединены с соответствующими входами первого блока сравнения.

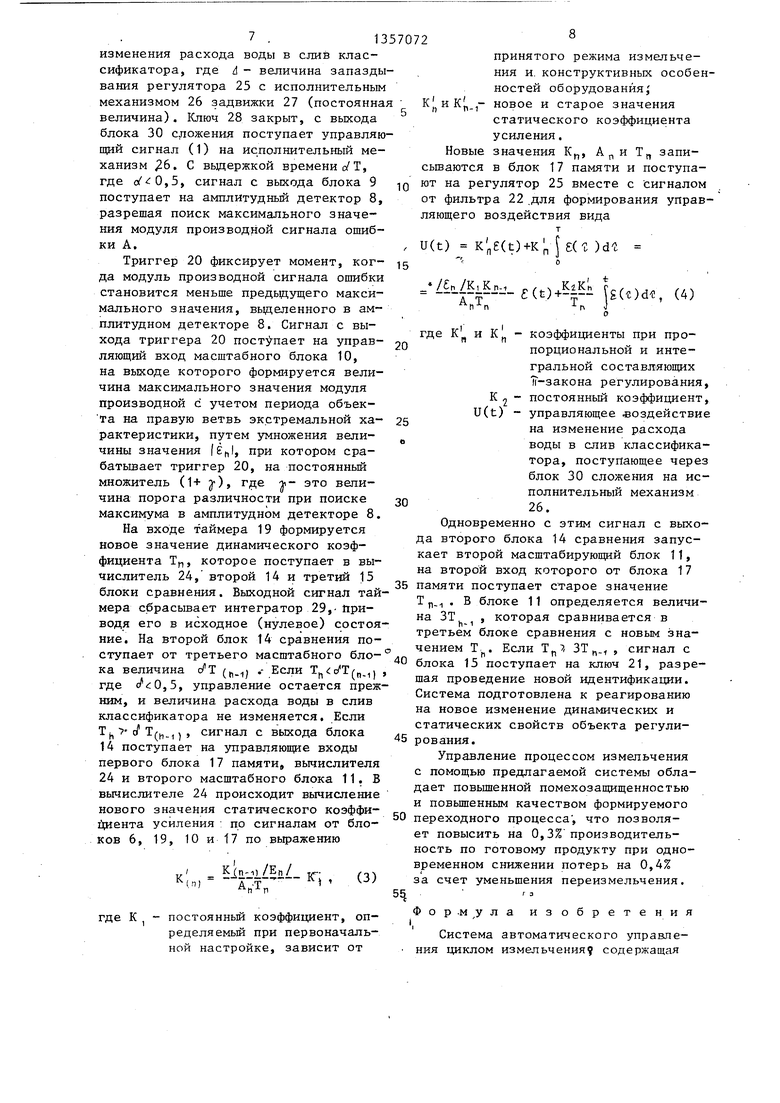

На чертеже представлена блок-схема предлагаемой системы.

Система содержит датчик 1 крупности,- задатчик 2 крупности, задатчик 3 модуля отклонения, блок 4 дифференцирования, первьй 5 и второй 6 блоки определения модуля, логический блок 7, амплитудный детектор 8, блок 9 формирования вьщержки времени масштабные блоки 10-12, блоки 13-16 сравнения, блоки 17 и 18 памяти, таймер 19, триггер 20, первьй ключ 21, фильтр 22, блок 23 умножения, вычислитель 24, регулятор 25, исполнительный механизм 26, задйижку 27, второй ключ 28, интегратор 29 и блок 30 сложения.

На чертеже представлены также мельнида 31 и классификатор 32, являющиеся объектом управления.

Управление циклом измельчения осуществляется следующим образом.

Перерабатываемая руда, измельченная в мельнице 31, поступает в классифицирующий аппарат 32, где разделяется на крупную фракцию, возвращаемую на доизмельчение в мельницу 31, и мелкую фракцию, которая в составе выходного продукта цикла со слива классифицирующего апйарата 32 поступает на обогащение.

Задачей цикла измельчения является полное раскрытие зерен полезного компонента без их переизмельчения. Целевой функцией управления циклом является максимизация производитель ности по вновь образованному расчетному готовому классу крупности. Величина расчетного готового класса крупности определяется характером вкрапленности полезного компонента и устанавливается задатч-иком 2.

Текущее значение х содержания выбранного класса крупности в выходном продукте цикла измеряется датчиком 1 крупности и поступает на блок 13 сравнения, где сравнивается с заданным значением. В блоке -13 сравнения и фильтре 22 выделяется отфильтрованное значение текущего отклонения 1 содержания выбранного Knact ci крупности от заданного значения, а в первом блоке 5 определения

,

57072

модуля

определяется модуль Е гекущеITO отклонения „ .

В блоке 4 дифференцирования определяется производная tf сигнала оши10

15

20

L , а второй блок 6 определения

б ки

совместно с амплитудным детектором 8, триггером 20 и первым масштабным блоком 10 вьделяют максимальное значение А .модуля производной сигнала ошибки (),1

Максимальное значение А модуля производной сигнала ошибки определяется в процессе активной идентификации, заключающейся в подаче на вход регулятора 25 нормированного скачкообразного воздействия U, , определяемого в блоке 23 умножения и интеграторе 29 по сигналам от первого блока. 17 памяти и фильтра 22 по выражению

1

kn (o)di:.

(11

k

kn

где I - оценка цостоянной времени объекта

нормирующий множитель коэффициент пропорциональной части регулятора 25-, Е(0) - значение ошибки рассогласования в момент подачи скачка t 0.

; Скачкообразное воздействие U;.. на изменение расхода воды в слив классифицирующего агрегата подается в мо-- мент tj), определяемьй в логическом блоке 7 в момент достижения модуля производной текущего отклонения нулевого значения, путем оценки положения системы на фазовой плоскости . (Е,Ё). Процесс идентификации начи- нается при переходе фазавой траектории через ось Е при выполнении следующих логических условий, проверка которых осуществляется в логическом блоке 7,

I г.1 . ,

Знак Ц.1 Знак n-i Знак ЕП Знак t „.,

(2)

где|Г 1- заданное значение модуля ,

ЛИЧИНЫ ошибкиС)от блока 3. При выполнении условий (2) сигналы с логического блока 7 поступают на управляющие входы первого блока 17 памяти, блока 23 умножения, второго ключа 28, таймера 19 и блока 9 формирования вьщержки времени. В таймере

19 фиксируется момент t,

+ Л t

7 .13

изменения расхода воды в слив классификатора, где 4 - величина запаздывания регулятора 25 с исполнительным механизмом 26 задвижки 27 (постоянна величина). Ключ 28 закрыт, с выхода блока 30 сложения поступает управляющий сигнал (1) на исполнительный механизм 6. С выдержкой времени с/Т, где (,5, сигнал с выхода блока 9 поступает на амплитудньй детектор 8, разрешая поиск максимального значения модуля производной сигнала ошибки А,

Триггер 20 фиксирует момент, ког- да модуль производной сигнала ошибки становится меньше предьщутцего максимального значения, вьщеленного в амплитудном детекторе 8. Сигнал с выхода триггера 20 на управляющий вход масштабного блока 10, на выходе которого формируется величина максимального значения модуля производной с учетом периода объек- та на правую ветвь экстремальной ха- рактеристики, путем умножения величины значения , при котором срабатывает триггер 20, на постоянный множитель (1+ j-), где TI- это величина порога различности при поиске максимума в амплитудном детекторе 8.

На входе таймера 19 формируется новое значение динамического коэффициента Tfi, которое поступает в вы

Одновременно с этим сигнал с да второго блока 14 сравнения за кает второй масштабирующий блок на второй вход которого от блока

П-1

числитель 24, второй 14 и третий 15

„ „35 памяти поступает старое значение

блоки сравнения. Выходной сигнал таи- „ „

мера сбрасывает интегратор 29,- приводя его в исходное (нулевое) состояние. На второй блок 14 сравнения поступает от третьего масштабного бло-° ка величина с/Т (. .- Если („, , где ,5, управление остается прежним, и величина расхода воды в слив классификатора не изменяется. Если J Т/, J , сигнал с выхода блока 14 поступает на управляющие входы первого блока 17 памяти, вычислителя 24 и второго масштабного блока 11. В вычислителе 24 происходит вычисление нового значения статического коэффи- 11Сиента усиления ; по сигналам от блоков 6, 19, 10и17по вьфажению

В блоке 11 определяется вел на ЗТ , которая сравнивается в третьем блоке сравнения с новым з чением Т:. Если Т, ЗТ . , сигнал

40 блока 15 поступает на ключ 21, ра шая проведение новой идентификаци Система подготовлена к реагирован на новое изменение динамических и статических свойств объекта регул

45 рования.

Управление процессом измельчен с помощью предлагаемой системы об дает повьш1енной помехозащищенност и повьшгенным качеством формируемо

50 переходного процесса , что позволя ет повысить на 0,3% производитель ность по готовому продукту при од временном снижении потерь на 0,4% за счет уменьшения переизмельчени

Мп 1) /ЕП/ Tf- стч - T-S- -- й. , и;

А -Т

(

где К - постоянньй коэффициент, оп- ределяемьм при первоначальной настройке, зависит от

2

8

принятого режима измельчения и. конструктивных особенностей оборудования ,,- новое и старое значения

статического коэффициента усиления.

Новые значения К,, А и Т„ запи- сьшаются в блок 17 памяти и поступают на регулятор 25 вместе с сигналом от фильтра 22 .для формирования управляющего воздействия вида

т

U(t) К „е(1:)+Кп ( )d. о

,Кп-,

KiKh

А.ТП

:(t) fsCOd (4)

n J

где К и Kj, - коэффициенты при пропорциональной и интегральной составляющих -закона регулирования, К 2 - постоянный коэффициент, U(t) - управляющее воздействие на изменение расхода воды в слив классификатора, поступающее через блок 30 сложения на исполнительный механизм 26.

Одновременно с этим сигнал с выхода второго блока 14 сравнения запускает второй масштабирующий блок 11, на второй вход которого от блока 17

П-1

„ „

В блоке 11 определяется величина ЗТ , которая сравнивается в третьем блоке сравнения с новым значением Т:. Если Т, ЗТ . , сигнал с

0 блока 15 поступает на ключ 21, разрешая проведение новой идентификации. Система подготовлена к реагированию на новое изменение динамических и статических свойств объекта регули5 рования.

Управление процессом измельчения с помощью предлагаемой системы обладает повьш1енной помехозащищенностью и повьшгенным качеством формируемого

0 переходного процесса , что позволяет повысить на 0,3% производительность по готовому продукту при одновременном снижении потерь на 0,4% за счет уменьшения переизмельчения.

Фор.мула изобретения

Система автоматического управле- ния циклом измельчения содержащая

1357072

регулятор, четыре блока сравнения, два блока определения модуля, фильтр блок дифференцирования, амплитудньй детектор, три масштабных блока, вычислитель, два блока памяти, блок умножения, логический блок,, блок формирования вьщержки времени, триггер, таймер, первый ключ и.задатчик модуля отклонения, пр1ичем выход первого блока сравнения соединен с входом фильтра, выход которого соединен с входами блока дифференцирования и первого блока определения модуля, с перрыми .входами блока умножения, первого блока памяти и регулятора, выход блока дифференцирования через второй блок определения модуля подключен к первому входу амплитудного детектора, к второму входу первого блока памяти и к первому входу логического блока, вькод амплитудного детектора соединен с входом триггера и с первым входом первого масштабного блока, выход которого подключен к первому входу вычислителя, выход триггера соединен с вторым входом первого масштабного блока и с первым входом таймера, выход первого блока памяти соединен с вторым входом логи ческого блока, выход логического бло ка соединен с вторым входом блока ум ножения, вторым входом таймера, выход которого соединен с вторым входом вычислителя, третий вход которого соединен с выходом второго блока определения модуля, четвертый вход вычислителя соединен с первым выходом второго блока памяти, первый вхо которого соединен с первым выходом вычислителя, пятый вход вычислителя соединен с вторым выходом второго блока памяти, второй вход которого соединен с выходом логического блока третий вход второго блока памяти и шестой вход вычислителя соединены с выходом второго блока сравнения, первый вход которого соединен с первым вводом третьего блока сравнения и с

Составитель В.Алекперов Редактор И.Горна Техредл.Сердюкова Корректор в.Бутяга

Заказ 5920/5 Тираж 57-3Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

10

0

5

0

зо

25

35

40

45

выходом таймера, второй выход вычислителя соединен с четвертым входом второго блока памяти, первьш выход которого подключен к третьему входу . блока умножения, .выход второго блока сравнения соединен с первым выходом второго масштабного блока, второй выход которого соединен с вторым входом третьего блока сравнения, входы второго и третьего масштабных блоков соединены с вторым выходом второго блока памяти, выход третьего масштабного блока соединен с вторым входом второго блока сравнения, выход третьего блока сравнения соединен с первым входом первого ключа, второй вход которого соединен с выходом четвертого блока сравнения, входы четвертого блока сравнения подключены к задатчику модуля отклонения и к вьЕходу. первого блока определе- ния модуля, выход первого ключа соединен с вторым входом первого блока памяти первьй и второй выходы вычислителя соединены с первым и вторым входами регулятора, а выход фильтра соединен с третьим входом регулятора, отличающая с я тем, что, с целью повышения точности управления, она снабжена вторым ключом, датчиком и задатчиком крупности исполнительным механизмом задвижки, интегратором и блоком сложения, причем вькод блока умножения соединен с первым входом интегратора, выход которого соединен с первым входом блока сложения, к второму входу которого подключен выход второго ключа, первый вход которого соединен с выходом ре- гулятора, а второй - с выходом логического блока, выход таймера .соединен с вторым входом интегратора, выход блока сложения соединён с входом исполнительного механизма задвижки, а датчик и задатчик крупности соединены с соответствующими входами первого блока сравнения,

| название | год | авторы | номер документа |

|---|---|---|---|

| Система адаптивного управления одностадийным циклом мокрого измельчения | 1987 |

|

SU1480878A1 |

| Адаптивный регулятор | 1982 |

|

SU1076873A1 |

| Система автоматического регулирования загрузки мельницы | 1982 |

|

SU1255207A1 |

| Система автоматического регулирования одностадийным циклом мокрого измельчения | 1982 |

|

SU1255208A1 |

| Адаптивный регулятор | 1987 |

|

SU1432459A1 |

| Система регулирования загрузки измельчительного агрегата | 1983 |

|

SU1146085A1 |

| Система управления измельчительным агрегатом | 1982 |

|

SU1101302A1 |

| Самонастраивающаяся система автоматического управления процессом мокрого измельчения | 1981 |

|

SU1018106A1 |

| Система автоматического регулирования загрузки мельницы | 1981 |

|

SU1007729A1 |

| Система автоматического управления одностадийным циклом мокрого измельчения | 1987 |

|

SU1491579A1 |

Изобретение относится к системам автоматического управления процессами измельчения и классификации РуЗа при обогащении полезных ископаемых, может быть использовано на обогатительных фабриках цветной и черной металлургии при переработке руд с изменяющимися физико-химическими и текстурно-структурными свойствами, .а также в условиях: дрейфа статических характеристик технологических агрегатов, вызванного их износом. Позволяет повысить точность управления. Система содержит датчик 1 крупности, задатчик 2 крупности, задатчик 3 йо- дуля отклонения, блок 4 дифференцирования, блоки 5 и 6 определения модуля, логический блок 7, амплитудный детектор 8, блок 9 формирования выдержки времени, масштабные блоки 10- 12, блоки 13-16 сравнения, блоки 17 и 18 памяти, таймер 19, триггер- 20, ключ 21, фильтр 22, блок 23 умножения, вычислитель 24, регулятор 25, исполнительный механизм 26 задвижки 27, ключ 28, интегратор 29, блок 30 сложения. 1 ил. & (Л со ел о to

Авторы

Даты

1987-12-07—Публикация

1983-07-11—Подача