1

Изобретение относится к вычислительной технике и предназначено для объединения двух ЭВМ, работающих в реальном масштабе времени.

Цель изобретения - повьш1ение скорости обмена данными за счет обеспечения режима прямого доступа к памяти обеих ЭВМ одновременно.

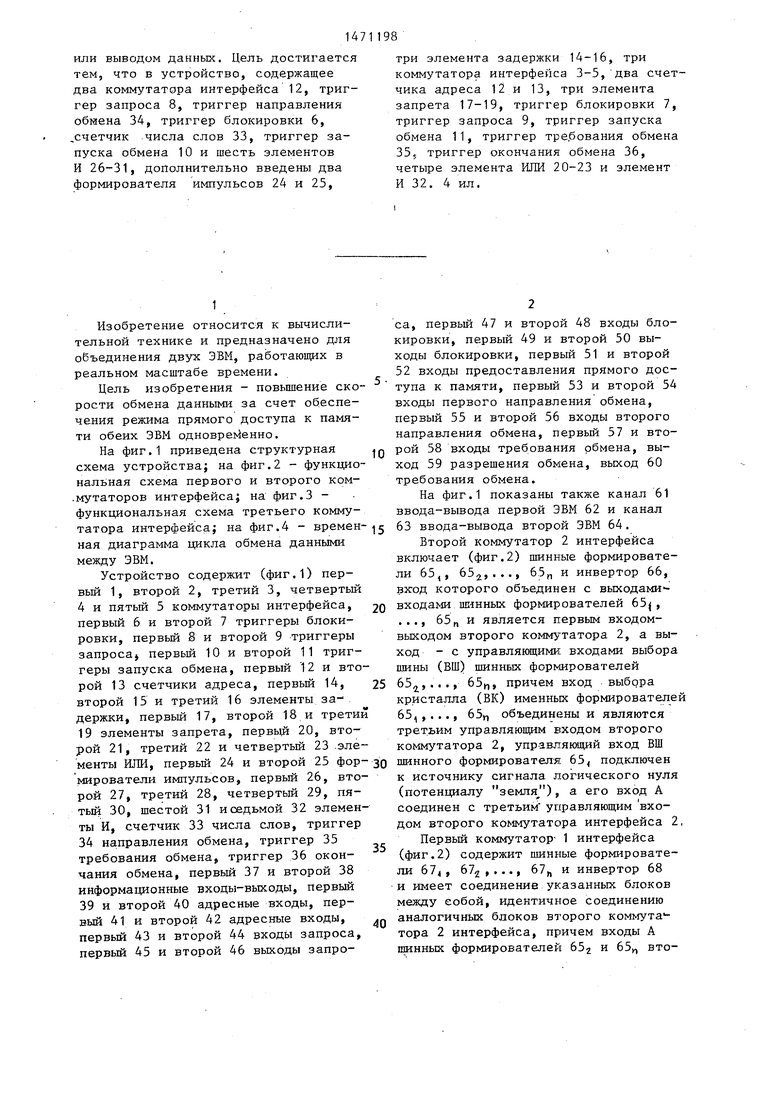

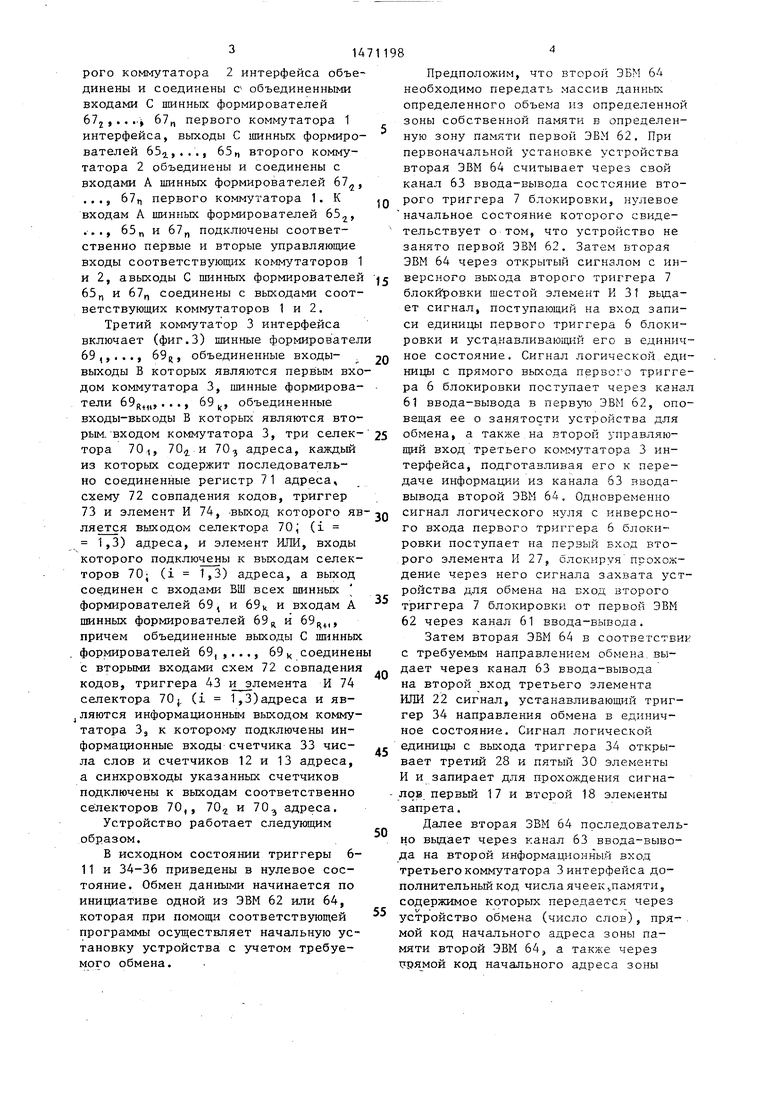

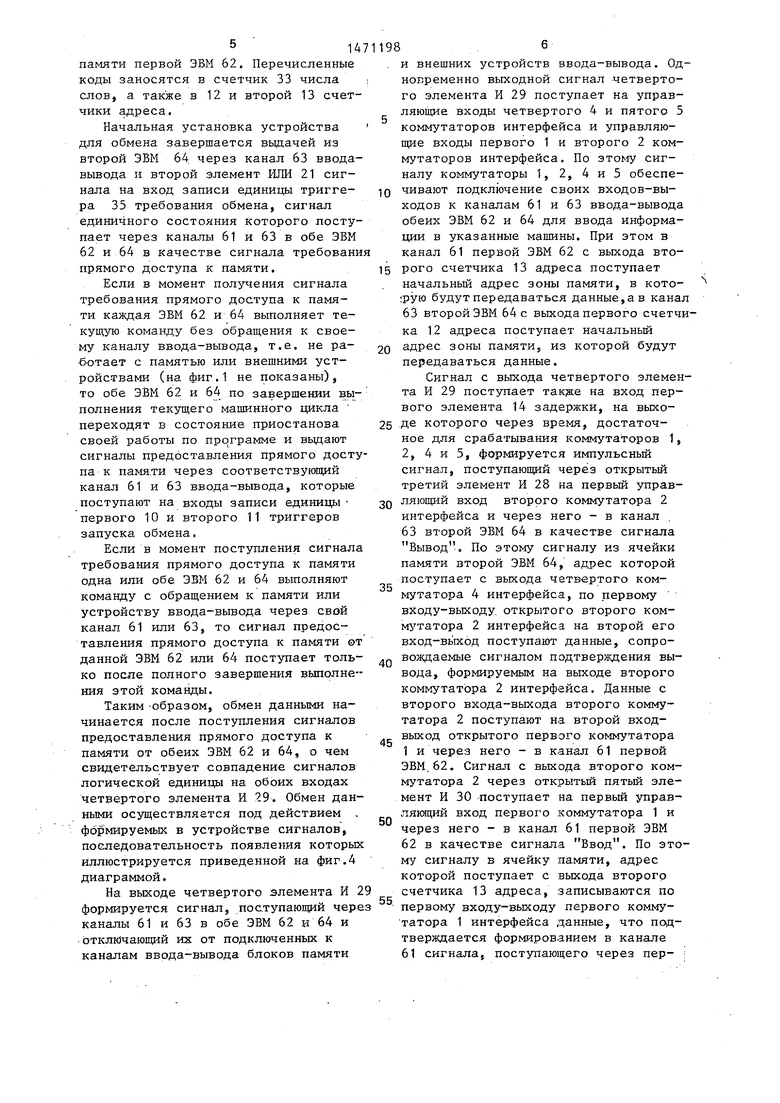

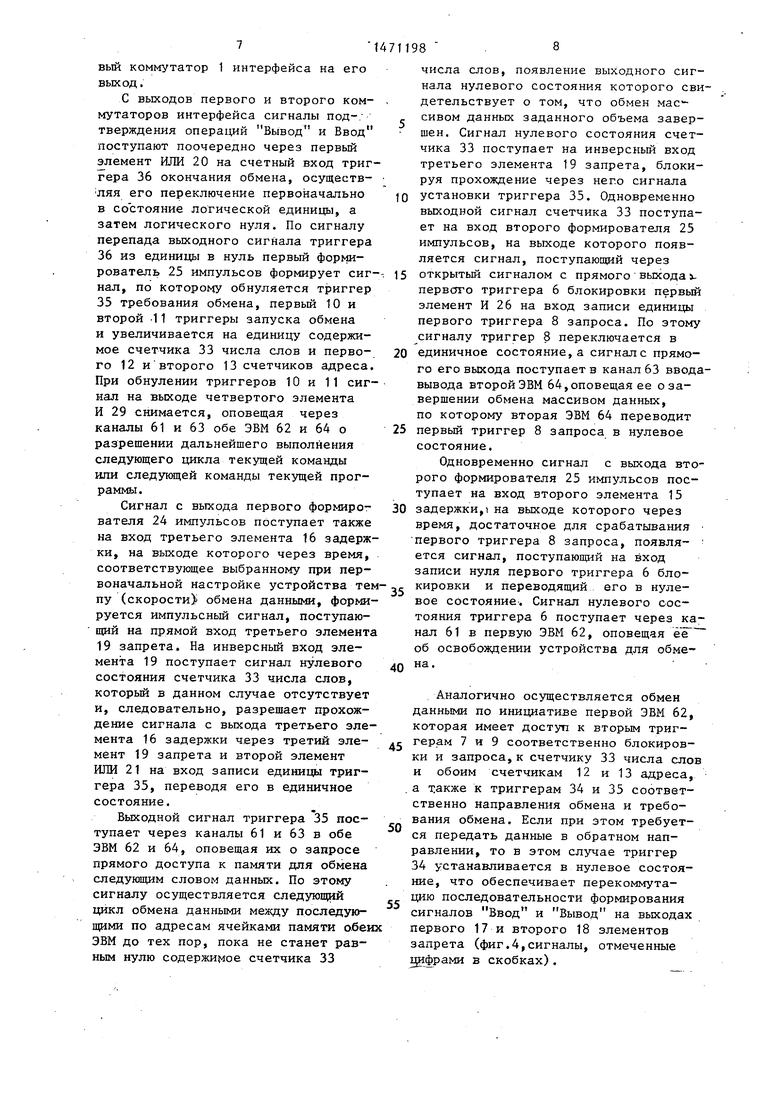

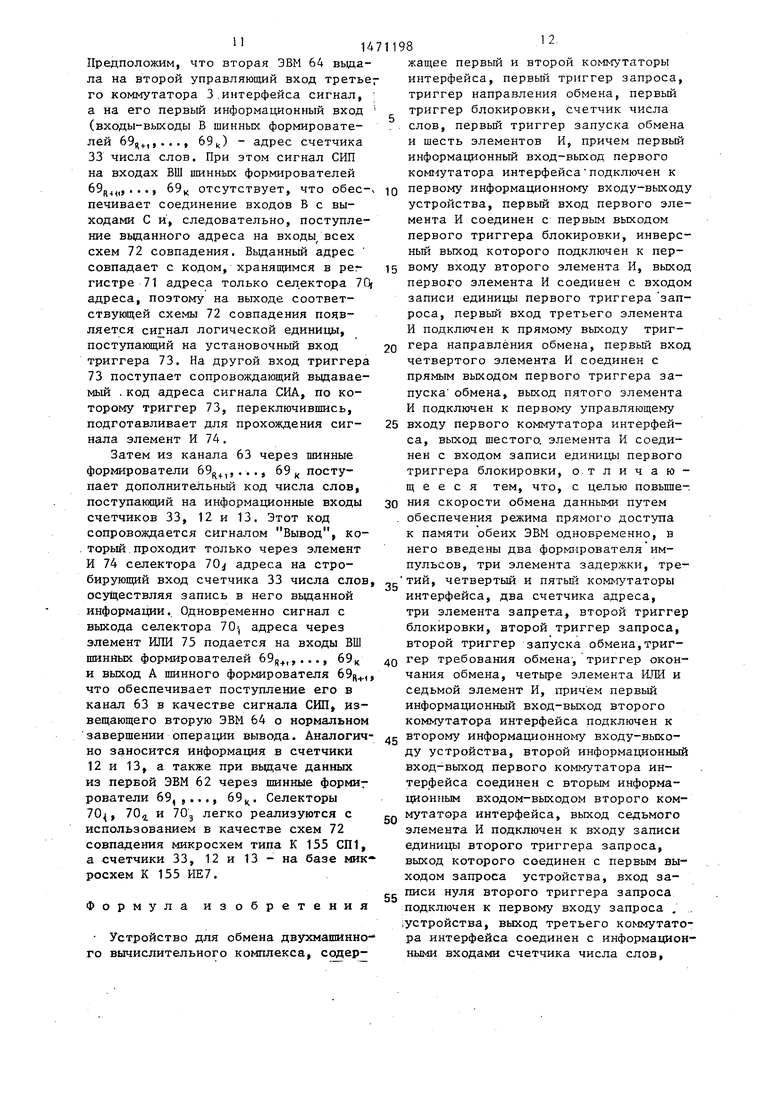

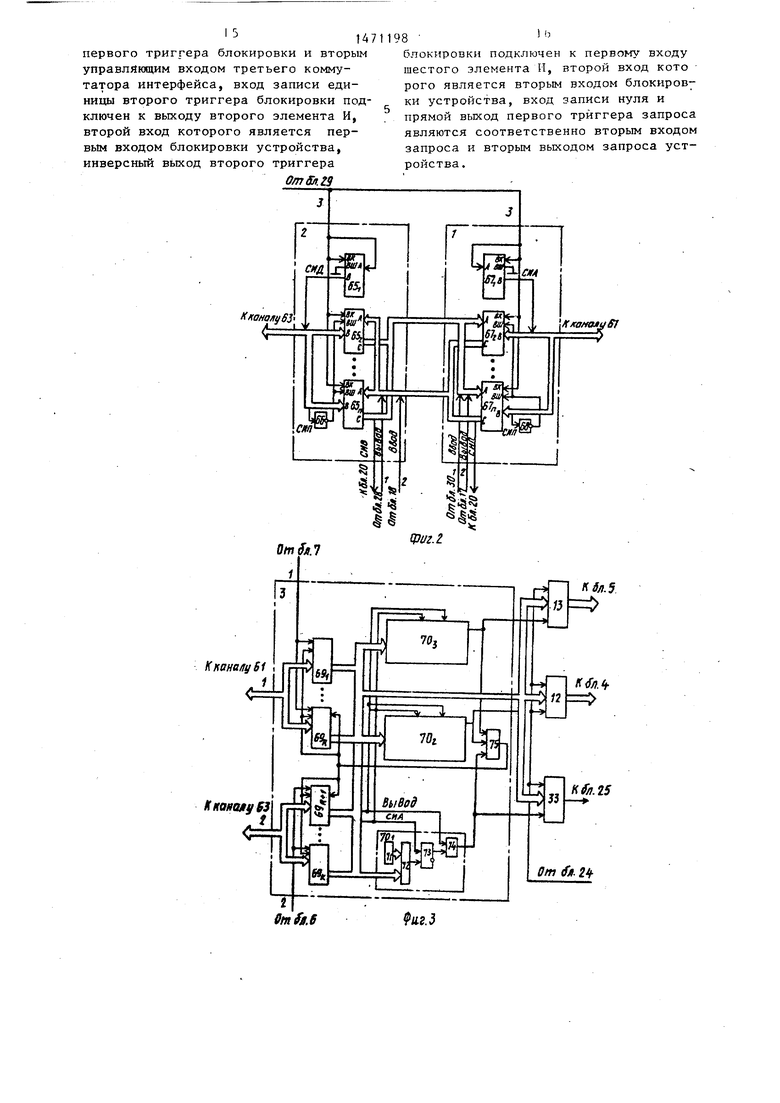

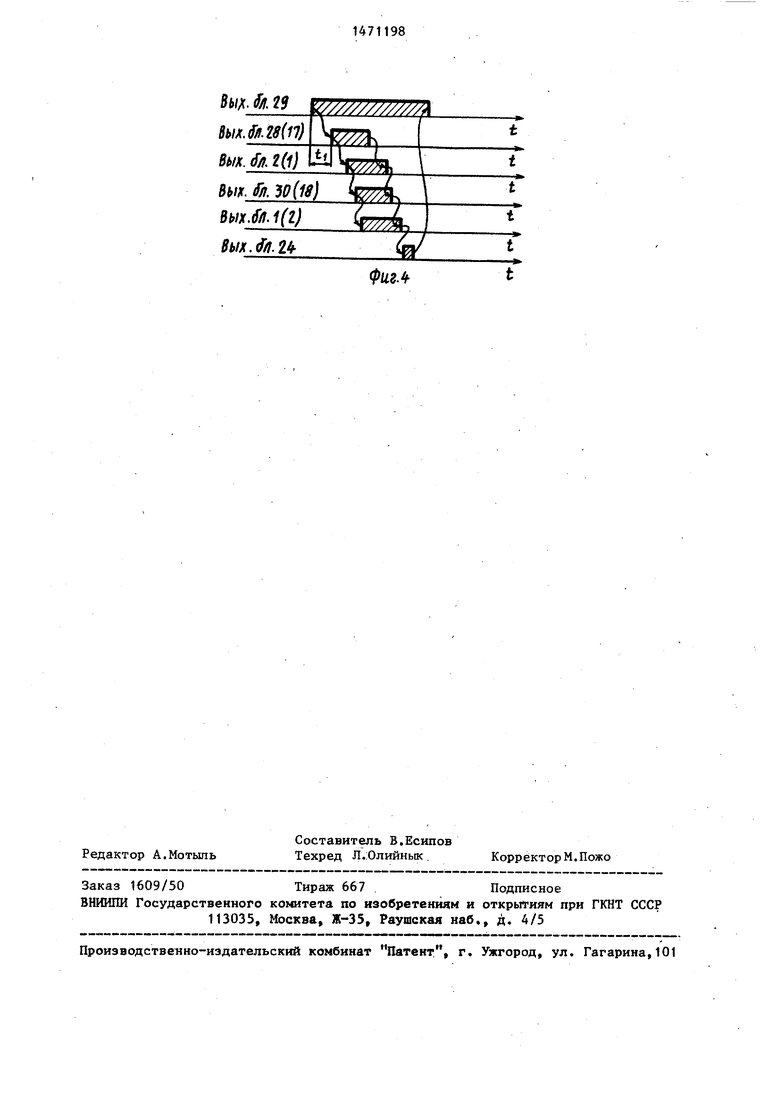

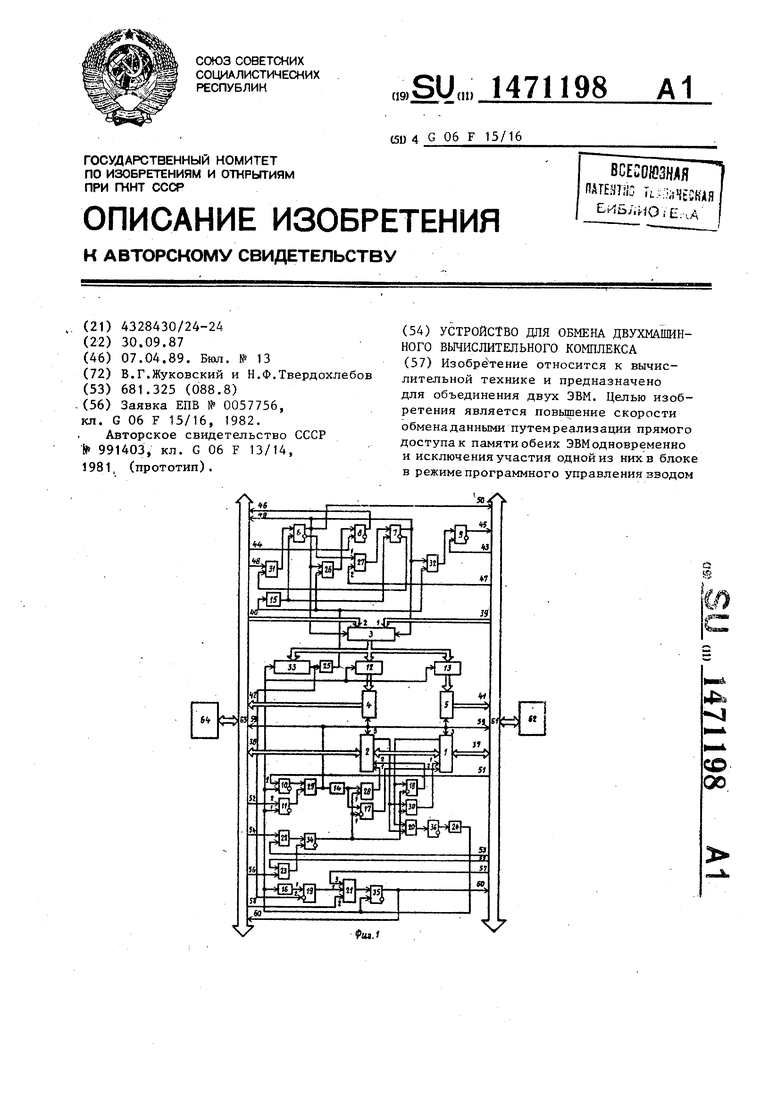

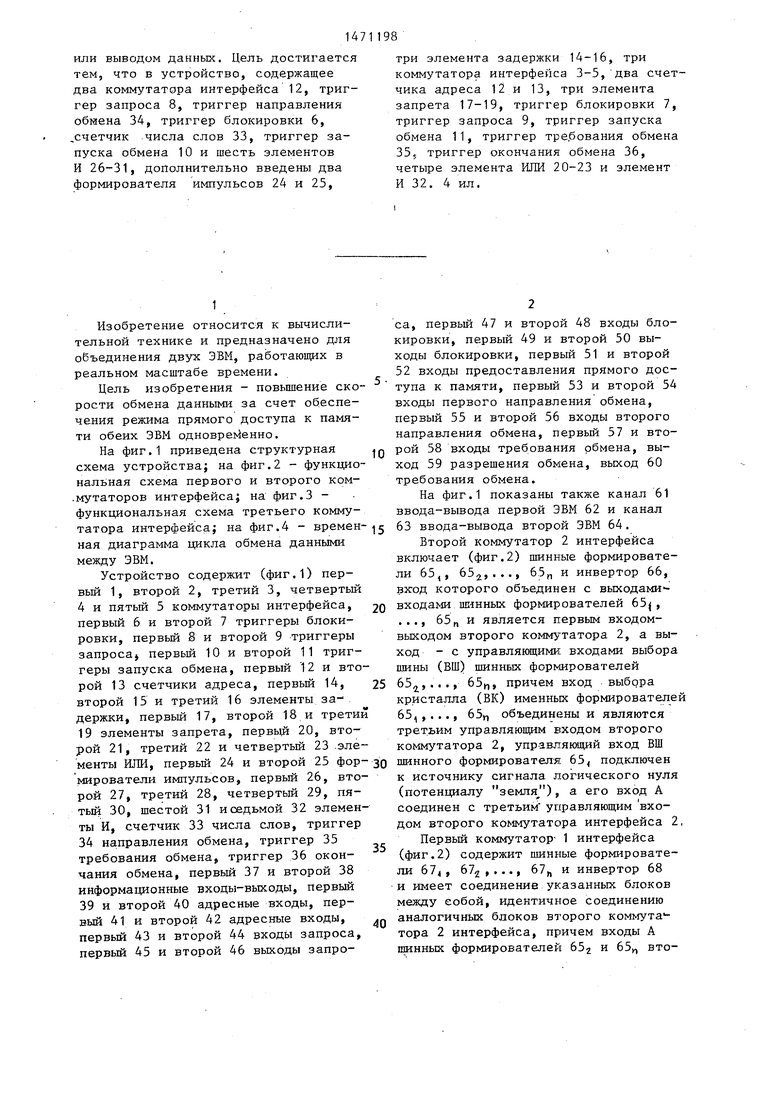

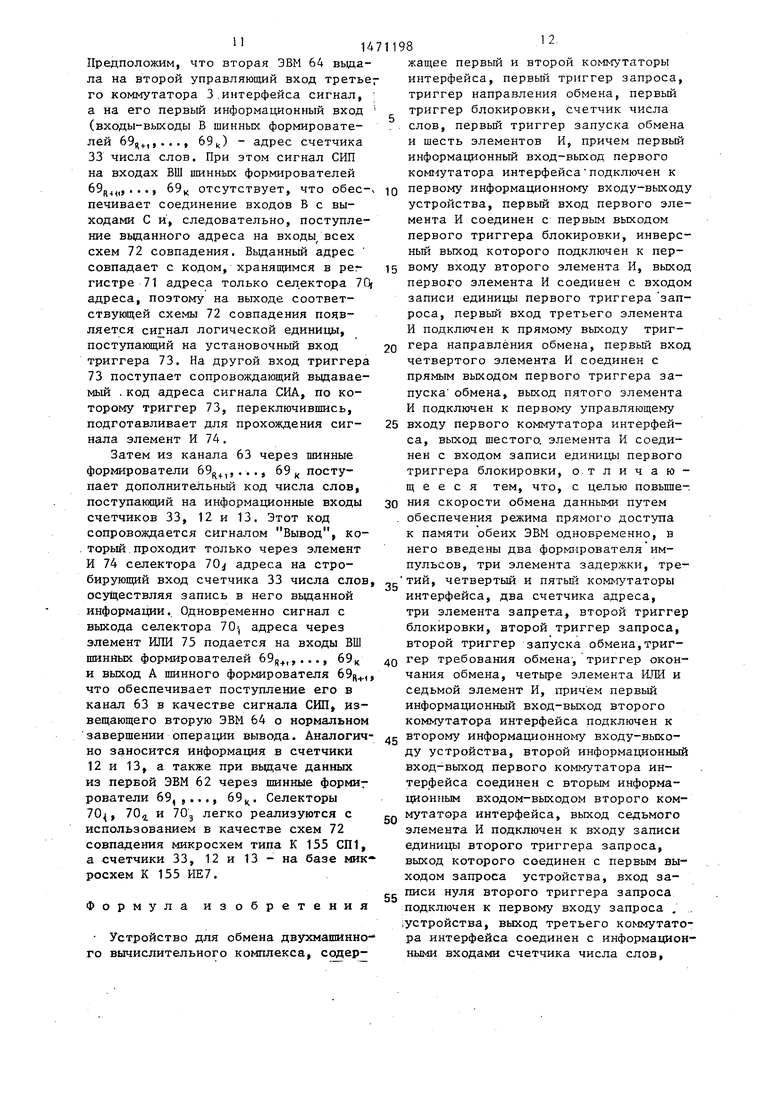

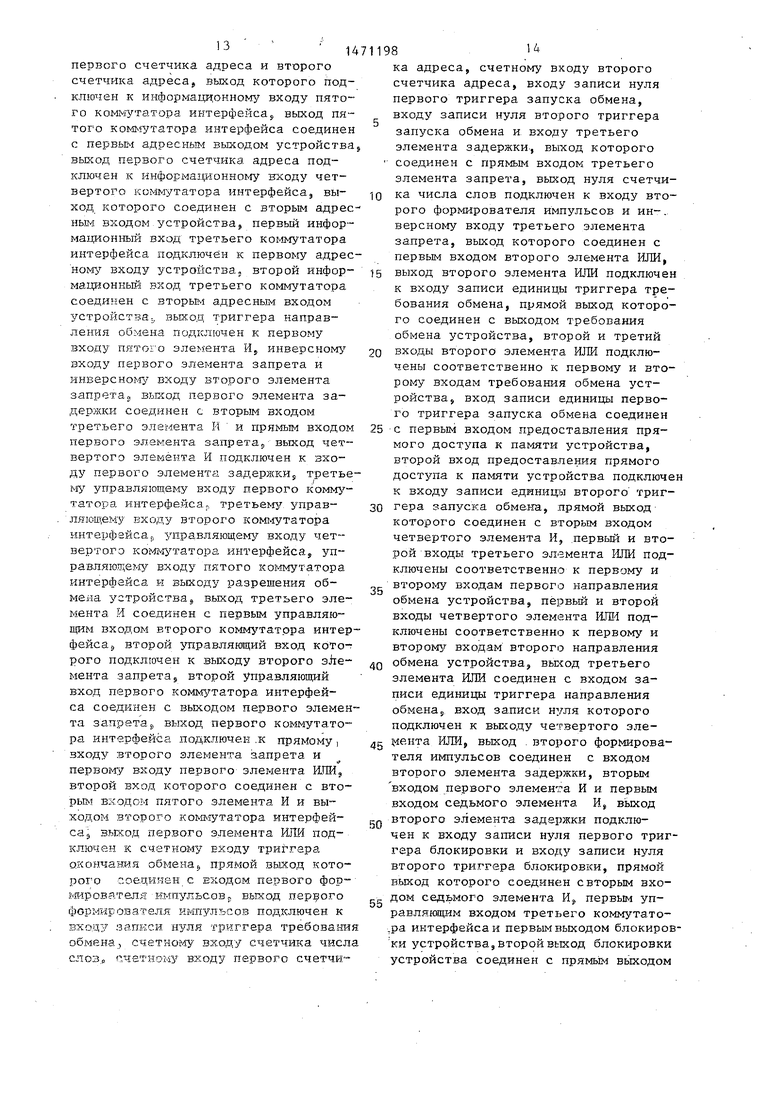

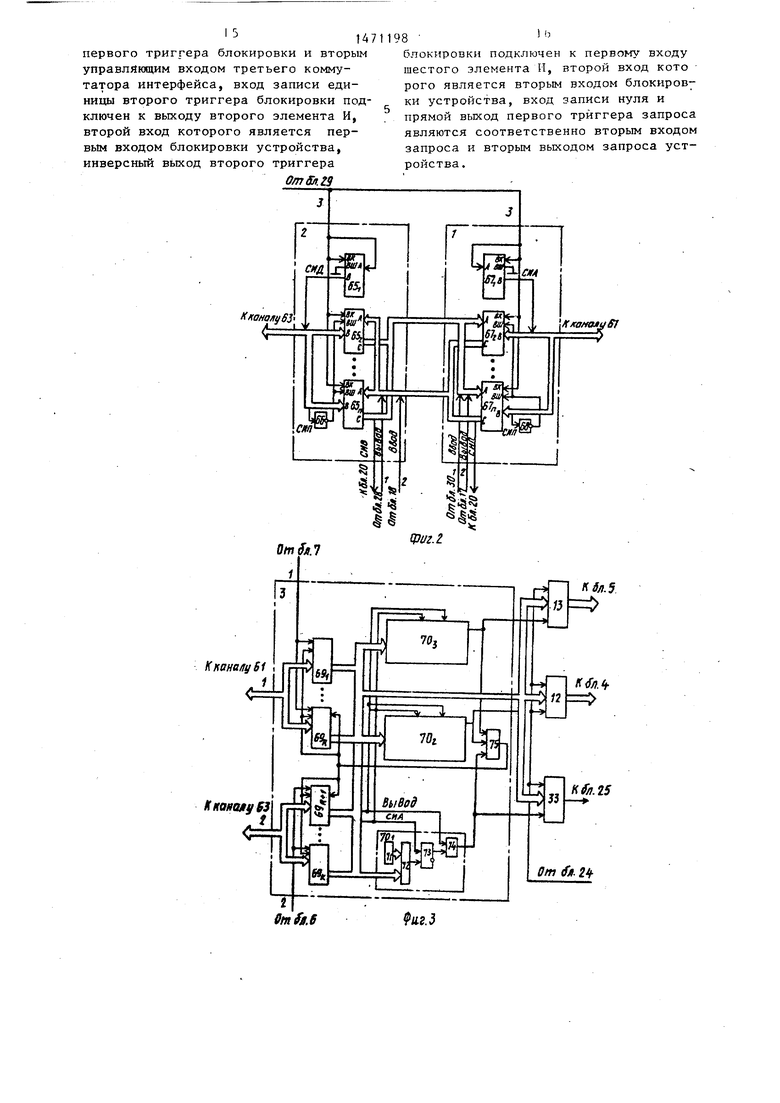

На фиг.1 приведена структурная схема устройства; на фиг.2 - функциональная схема первого и второго ком- .мутаторов интерфейса; на фиг.З - функциональная схема третьего коммутатора интерфейса; на фиг.4 - временная диаграмма цикла обмена данными между ЭВМ.

Устройство содержит (фиг.1) первый 1, второй 2, третий 3, четвертый 4 и пятый 5 коммутаторы интерфейса, первый 6 и второй 7 триггеры блокировки, первый 8 и второй 9 триггеры запроса) первый 10 и второй 11 триггеры запуска обмена, первый 12 и второй 13 счетчики адреса, первый 14, второй 15 и третий 16 элементы задержки, первьш 17, второй 18 и третий 19 элементы запрета, первь1й 20, второй 21, третий 22 и четвертый 23 .элементы ИЛИ, первьш 24 и второй 25 фор мирователи импульсов, первый 26, второй 27, третий 28, четвертый 29, пя- тьщ 30, шестой 31 и седьмой 32 элементы И, счетчик 33 числа слов, триггер 34 на.правления обмена, триггер 35 требования обмена, триггер 36 окончания обмена, первьш 37 и второй 38 информационные входы-выходы, первый 39 и второй 40 адресные входы, первый 41 и второй 42 адресные входы, первый 43 и второй 44 входы запроса, первый 45 и второй 46 выходы запро

са, первый 47 и второй 48 входы блокировки, первый 49 и второй 50 выходы блокировки, первый 51 и второй 52 входы предоставления прямого доступа к памяти, первый 53 и второй 54 входы первого направления обмена, первый 55 и второй 56 входы второго направления обмена, первый 57 и второй 58 входы требования обмена, выход 59 разрешения обмена, выход 60 требования обмена.

На фиг.1 показаны также канал 61 ввода-вывода первой ЭВМ 62 и канал 63 ввода-вывода второй ЭВМ 64.

Второй коммутатор 2 интерфейса включает (фиг.2) шинные формирователи 65,, 652,..., 65„ и инвертор 66, вход которого объединен с выходами-входами шинных формирователей 65, ..., 65„ и является первым входом- вькодом второго коммутатора 2, а выход - с управлякщими; входами выбора щины (ВШ) шинных формирователей 652,..., 65ц, причем вход выбора кристалла (ВК) именньк формирователей 65,,..., 65ц объединены и являются третьим управляющим входом второго коммутатора 2, управляющий вход ВШ шинного формирователя 65 подключен к источнику сигнала хюгического нуля (потенциалу земля), а его вход А соединен с третьим управляющим входом второго коммутатора интерфейса 2,

Первый коммутатор- 1 интерфейса (фиг.2) содержит шинные формирователи 67, 672,..., инвертор 68 и имеет соединение указанных блоков между собой, идентичное соединению аналогичных блоков второго коммута-- тора 2 интерфейса, причем входы А шинных формирователей 652 и вто31471198

2 интерфейса объе5

to

15

рого коммутатора

динены и соединены о объединенными входами С шинных формирователей б , .. . 67„ первого коммутатора 1 интерфейса, выходы С шинных формирователей 65.,..., 65ц второго коммутатора 2 объединены и соединены с входами А шинных формирователей 67, ..., 67,1 первого коммутатора 1. К входам А шинных формирователей 65j, ..., 65п и 67„ подключены соответственно первые и вторые управляющие входы cooTBeTCTByranpix коммутаторов 1 и 2, авыходы С шинных формирователей 65„ и 67f, соединены с выходами соответствующих коммутаторов 1 и 2.

Третий коммутатор 3 интерфейса включает (фиг.З) шинные формирователи 69,,..., 69, объединенные входы- 20 выходы В которых являются первым входом коммутатора 3, шинные формирова- - тели 69|,,,,. . .) 9 , объединенные

входы-выходы В которых являются вторым. ВХОДОМ коммутатора 3, три селек- 25 тора 701, 70 и 70, адреса, каждый из которых содержит последовательно соединенные регистр 71 адреса, схему 72 совпадения кодов, триггер 73 и элемент И 74, -выход которого ляется выходом селектора 70; (i 1,3) адреса, и элемент ИЛИ, входы которого подключены к выходам селекторов 70; (i 1,3) адреса, а выход соединен с входами ВШ всех шинных формирователей 69, и 69к и входам А шинных формирователей 69 и 69,, причем объединенные выходы С шинных формирователей 69,,..., 69ц соединены с вторыми входами схем 72 совпадения кодов, триггера 43 и элемента И 74 селектора 70, (i 1,3)адреса и яв- ляются информационным выходом коммутатора Зз к которому подключены информационные входы счетчика 33 числа слов и счетчиков 12 и 13 адреса, а синхровходы указанньк счетчиков подключены к выходам соответственно селекторов 70,, 70 и 70 адреса. Устройство работает следующим образом.

В исходном состоянии триггеры 6- 11 и 34-36 приведены в нулевое состояние. Обмен данными начинается по нициат иве одной из ЭВМ 62 или 64, которая при помощи соответствующей программы осуществляет начальную установку устройства с учетом требуеого обмена.

35

40

45

50

55

н

7

5

o

5

0

5 Q

5

0

5

0

5

Предположим, что второй ЭВМ 64 необходимо передать массив данных определенного объема из определенной зоны собственной памяти в определенную зону памяти первой ЭВМ 62. При первоначальной установке устройства вторая ЭВМ 64 считывает через свой канал 63 ввода-вывода состояние второго триггера 7 блокировки, нулевое начальное состояние которого свидетельствует о том, что устройство не занято первой ЭВМ 62. Затем вторая ЭВМ 64 через открытый сигналом с инверсного выхода второго триггера 7 блокировки шестой элемент И 31 вьща- ет сигнал, поступающий на вход записи единицы первого триггера 6 блокировки и уста.навливающгй его в единичное состояние. Сигнал логической единицы с прямого выхода первого триггера 6 блокировки поступает через канал

61ввода-вывода в первую ЭВМ 62, оповещая ее о занятости устройства для обмена, а также на второй управляющий вход третьего коммутатора 3 интерфейса, подготавливая его к передаче информации из канала 63 ввода- вывода второй ЭВМ 64. Одновременно сигнал логического нуля с инверсного входа первого триггера 6 блокировки поступает на первый вход второго элемента И 27, блокируя прохождение через него сигнала захвата устройства для обмена на вход второго триггера 7 блокировки от первой ЭВМ

62через канал 61 ввода-вывода. Затем вторая ЭВМ 64 в соответстви

с требуемым направлением обмена, выдает через канал 63 ввода-вывода на второй вход третьего элемента ИЛИ 22 сигнал, устанавливающий триггер 34 направления обмена в единичное состояние. Сигнал логической единицы с выхода триггера 34 открывает третий 28 и пятый 30 элементы И и запирает для прохождения сигналов первый 17 и второй 18 элементы запрета.

Далее вторая ЭВМ 64 последовательно выдает через канал 63 ввода-вывода на второй информационный вход третьего коммутатора 3 интерфейса дополнительный код числа ячеек памяти, содержимое которых передается через устройство обмена (число слов), пря-. мой код начального адреса зоны памяти второй ЭВМ 64J а также через код начального адреса зоны

514

памяти первой ЭВМ 62. Перечисленные коды заносятся в счетчик 33 числа слов, а также в 12 и второй 13 счетчики адреса.

Начальная установка устройства для обмена завершается вьщачей из второй ЭВМ 64 через канал 63 ввода- вывода и второй элемент ИЛИ 21 сигнала на вход записи единицы триггера 35 требования обмена, сигнал единичного состояния которого поступает через каналы 61 и 63 в обе ЭВМ 62 и 64 в качестве сигнала требовани прямого доступа к памяти.

Если в момент получения сигнала требования прямого доступа к памяти каждая ЭВМ 62 и 64 выполняет текущую команду без обращения к своему каналу ввода-вывода, т.е. не работает с памятью или внешними устройствами (на фиг.1 не показаны), то обе ЭВМ 62 и 64 по завершении выполнения текущего машинного цикла переходят в состояние приостанова своей работы по программе и выдают сигналы предоставления прямого доступа к памяти через соответствуюшдй канал 61 и 63 ввода-вывода, которые поступают на входы записи единицы первого 10 и второго 11 триггеров запуска обмена,

Если в момент поступления сигнала требования прямого доступа к одна или обе ЭВМ 62 и 64 выполняют комавду с обращением к памяти или устройству ввода-вывода через свой канал 61 или 63, то сигнал предоставления прямого доступа к памяти от данной ЭВМ 62 или 64 постзшает только после полного завершения выполнения этой команды.

Таким -образом, обмен данными начинается после поступления сигналов предоставления прямого доступа к памяти от обеих ЭВМ 62 и 64, о чем свидетельствует совпадение сигнгшов логической единицы на обоих входах четвертого элемента И 29. Обмен данными осуществляется под действием . формируемых в устройстве сигналов, последовательность появления которых иллюстрируется приведенной на фиг.4 диаграммой.

На выходе четвертого элемента И 2 формируется сигнал, поступающий чере каналы 61 и 63 в обе ЭВМ 62 и 64 и отключающий их от подключенных к каналам ввода-вывода блоков памяти

986

и внешних устройств ввода-вывода. Одновременно выходной сигнал четвертого элемента И 29 поступает на управляющие входы четвертого 4 и пятого 5 коммутаторов интерфейса и управляю- входы первого 1 и второго 2 коммутаторов интерфейса. По этому сигналу коммутаторы 1, 2, 4 и 5 обеспе0 чивают подключение своих входов-выходов к каналам 61 и 63 ввода-вывода обеих ЭВМ 62 и 64 для ввода информации в указанные машины. При этом в канал 61 первой ЭВМ 62 с выхода вто5 рого счетчика 13 адреса поступает начальный адрес зоны памяти, в кото- ;рую будут передаваться данные,а в канал 63 второй ЭВМ 64с выхода первого счетчика 12 адреса поступает начальный

0 адрес зоны памяти, из которой будут передаваться данные.

Сигнал с выхода четвертого элемента И 29 поступает на вход первого элемента 14 задержки, на выхо5 де которого через время, достаточное для срабатывания коммутаторов 1, 2, 4 и 5, формируется импульсный сигнал, поступающий через открытый третий элемент И 28 на первый управ0 ляющий вход второго коммутатора 2 интерфейса и через него - в канал 63 второй ЭВМ 64 в качестве сигнала Вывод, По этому сигналу из ячейки памяти второй ЭВМ 64, адрес которой поступает с выхода четвертого коммутатора 4 интерфейса, по первому входу-выходу, открытого второго ком- Mi TaTopa 2 интерфейса на второй его вход-вь1ход поступают данные, сопровождаемые сигналом подтверждения вывода, формируемым на выходе второго коммутатора 2 интерфейса. Данные с второго входа-выхода второго коммутатора 2 поступают на второй вход- выход открытого первого коммутатора 1 и через негр - в канал 61 первой ЭВМ,62, Сигнал с выхода второго коммутатора 2 через открытый пятый элемент И 30 поступает на первый управ- лякяций вход первого коммутатора 1 и через него - в канал 61 первой ЭВМ 62 в качестве сигнала Ввод. По этому сигналу в ячейку памяти, адрес которой поступает с выхода второго счетчика 13 адреса, записываются по первому входу-выходу первого коммутатора 1 интерфейса данные, что подтверждается формированием в канале 61 сигнала, поступающего через пер- ;

5

0

5

0

5.

7

вый коммутатор 1 интерфейса на его выход.

С выходов первого и второго ком- мутаторов интерфейса сигналы под-; тверждения операций Вывод и Ввод поступают поочередно через первый элемент ИЛИ 20 на счетный вход триггера 36 окончания обмена, осуществ- ляя его переключение первоначально в состояние логической единицы, а затем логического нуля. По сигналу перепада выходного сигнала триггера 36 из единицы в нуль первый формирователь 25 импульсов формирует сиг

нал, по KoTopoNjy обнуляется триггер 35 требования обмена, первый 10 и второй -11 триггеры запуска обмена и увеличивается на единицу содержимое счетчика 33 числа слов и первого 12 и второго 13 счетчиков адреса. При обнулении триггеров 10 и 11 сигнал на выходе четвертого элемента И 29 снимается, оповещая через каналы 61 и 63 обе ЭВМ 62 и 64 о разрешении дальнейшего выполнения следующего цикла текущей команды или следующей команды текущей программы.

Сигнал с выхода первого формирователя 24 импульсов поступает также на вход третьего элемента 16 задержки, на выходе которого через время, соответствующее выбранному при первоначальной настройке устройства темпу (скорости) обмена данными, формируется импульсный сигнал, поступающий на прямой вход третьего элемента 19 запрета. На инверсный вход элемента 19 поступает сигнал нулевого состояния счетчика 33 числа слов, которьй в данном случае отсутствует и, следовательно, разрешает прохождение сигнала с выхода третьего элемента 16 задержки через третий элемент 19 запрета и второй элемент ШШ 21 на вход записи единицы триггера 35, переводя его в единичное состояние.

Выходной сигнал триггера 35 поступает через каналы 61 и 63 в обе ЭВМ 62 и 64, оповещая их о запросе прямого доступа к памяти для обмена следующим словом данных. По этому сигналу осуществляется следующий цикл обмена данными между последующими по адресам ячейками памяти о.беи ЭВМ до тех пор, пока не станет равным нулю содержимое счетчика 33

8

числа слов, появление выходного сигнала нулевого состояния которого свидетельствует о том, что обмен массивом данных заданного объема завершен. Сигнал нулевого состояния счетчика 33 поступает на инверсный вход третьего элемента 19 запрета, блокируя прохождение через него сигнала установки триггера 35. Одновременно выходной сигнал счетчика 33 поступает на вход второго формирователя 25 импульсов, на выходе которого появляется сигнал, поступающий через

открытый сигналом с прямого выхода х. первого триггера 6 блокировки первый элемент И 26 на вход записи единицы первого триггера 8 запроса. По этому сигналу триггер 8 переключается в

единичное состояние,а сигнале прямого его выхода поступает в канал 63 ввода- вывода второй ЭВМ 64,оповещая ее о завершении обмена массивом данных, по которому вторая ЭВМ 64 переводит

первый триггер 8 запроса в нулевое состояние.

Одновременно сигнал с выхода второго формирователя 25 импульсов поступает на вход второго элемента 15

задержки, на выходе которого через время, достаточное для срабатывания первого триггера 8 запроса, появля- ется сигнал, поступающий на вход записи нуля первого триггера 6 блокировки и переводящий его в нулевое состояние. Сигнал нулевого состояния триггера 6 поступает через канал 61 в первую ЭВМ 62, оповещая её об освобождении устройства для обмена.

5

0

5

Аналогично осуществляется обмен данными по инициативе первой ЭВМ 62, которая имеет доступ к вторым триггерам 7 и 9 соответственно блокировки и запроса,к счетчику 33 числа слов и обоим счетчикам 12 и 13 адреса, а также к триггерам 34 и 35 соответственно направления обмена и требования обмена. Если при этом требуется передать данные в обратном направлении, то в этом случае триггер 34 устанавливается в нулевое состояние, что обеспечивает перекоммутацию последовательности формирования сигналов Ввод и Вывод на выходах первого 17 и второго 18 элементов запрета (фиг.4,сигналы, отмеченные 121фрами в скобках) .

. 9 147 Темп (скорость) обмена данными может быть первоначально (при изготовлении устройства) настроен заданием времени t задержки сигнала воспроизведения требования обмена третьим элементом 16 .задержки. Если t, -fc О, то сигнал с выхода.триггера 3.5 требования обмена практически не снимается поэтому обе ЭВМ 62 и.64 остаются приостановленньши до тех пор, пока не завершится весь процесс обмена заданным массивом данных. Этому случаю соответствует максимальная скорость обмена данными между ЭВМ 62 и 64. Увеличением времени t можно задать необходш й более медленный те,мп обмена данными между ЭВМ 62 и 645 который определит ту долю машинного времени которая будет отбираться на обмен данными без прекращения выполнения текущей програм- г/ы, не связанной с обменом.

Пример технической реализации первого 1 и второго 2 коммутаторов интерфейса (фиг.2) ориентирован на подключение к.каналам 61 и 63 ввода-вывода ЭВМ 62 и 64, построенных по правилам интерфейса VNIBUS(Q-BOS) Общая шина, например мини-ЭВМ СМ-4 или микро-ЭВМ Электроника-бОМ, Электроника МС 1201. качестве шинных формирователей 65j и 67/ (i 1 ,h.) при этом могут использоваться микросхемы типа К 589 АЛ 16 (АЛ 26), число h которых берется исходя из разрядности передаваемой через коммутаторы 1 и 2 информации. .

Шинные фор мирователи 651 и 67;; (i 1,h) при отсутствии сигнала на входах ВК обеспечивает полньй разрыв . связей межр,у каналами 61 и 63 обеих ЭВМ 62 и 64, С приходом сигнала по третьим управляющим входам коммутаторов 1 и 2 (на входы ВК шинных фор- мирователей 65; и 67;) обеспечивается соединение первых входов-выходов В шинных формирователей 65 ; и 67; (i 1,h) с входами А. Такое соеди- нение определяется состоянием входов ВШ шинньк формирователей. 65, и 67,- (i 1,h)j на которые подан сигнал логической единидь с выходов инверторов 66 и 68 при отсутствии на их входах сигнала синхронизации пассивного устройства СИП, Сигнал СИП в данном примере является сигналом подтверждения нормального завершения

0

19810

операции .ввода или вывода данных из каналов 61 и 63.

Сигнал включения коммутаторов 1 и 2 поступает через шинные формирователи 65, и 67, в каналы 61 и 63 в качестве синхронизации активного устройства СИА, определяющего занятость указанных каналов операции

Q ввода или вывода данных, которые начинаются с поочередным приходом сигналов на, первые и вторые управляняцие входы первого 1 и второго 2 коммутаторов интерфейса. Эти сигналы пос5 тупают через открытые пшнные формирователи 65 и 67, в каналы 61 и 63 в качестве сигналов Ввод или Вывод, на которые адресованное пассивное устройство (ячейка блока памяти) отвечает сигналом СИП. Сигнал СИП, поступив из канала 61 ;или 63 на вход инвертора 66 . или 68, обеспечи вает формирование на его выходе сигнала, которьш подается на входы ВШ шинных

5 формирователей 65; и 67; (i 27п) и осуществляет соединение входа-выхода В с выходами С и, следовательно, поступление сигнала СИП на выход первого 1 или второго 2 коммутаторов

0 интерфейса в качестве сигнала, подтверждения нормального завершения операции ввода или вывода данных.

Аналогично на щинньгх формировате- , лях типа К 589 АП 16 (АП 26) строится третий коммутатор 3 интерфейса (фиг.З); который при отсутствии сигналов на первом и втором управляющих входах (входах ВК пшнньпс формирователей 69, , 69д, 69f,,,...., 69,) обеспер сивает полное отключение информационных входов счетчика 33 числа слов и обоих Счетчиков 12 и 13 адреса от каналов 61 и 63 ввода-вывода. В дан- . ном варианте технической реализации третьего коммутатора 3 интерфейса предполагается работа с каналами 61 и 63- ввода-вывода микро-ЭВМ типа Электроника-60 и Электроника МС.1201.02, в интерфейсе которых шины данных и шЬны адрегсов совмещены конструктивно и выдача начинается с выдачи адреса внешнего устройства (в данном примере одного из счетчиков 12, 13 или 33), Для распознания адреса третий коммутатор 3 интерфейса содержит три селектора 70, 70 и 70 адреса, в регистре 71 адреса, которого хранится закрепленный за соответствуюшрм счетчиком адрес.

5

5

0

5

11

Предположим, что вторая ЭВМ 64 вьща- ла на второй управляющий вход третье го коммутатора 3.интерфейса сигнал, а на его первый информационный вход (входы-выходы В шинных формирователей 69щ.,,..., 69к) - адрес счетчика 33 числа слов. При этом сигнал СИП на входах ВШ шинных формирователей , . .., 69 отсутствует, что обес-v печивает соединение входов В с выходами С и, следовательно, поступление вьщанного адреса на входы всех схем 72 совпадения. Выданный адрес совпадает с кодом, хранящимся в рег гистре 71 адреса только седектора 7С1( адреса, поэтому на выходе соответствующей схемы 72 совпадения появляется сигнал логической единицы, поступающий на установочный вход триггера 73. На другой вход триггера 73 поступает сопровождающий выдаваемый , код адреса сигнала СИЛ, по которому триггер 73, переключивщись, подготавливает для прохождения сигнала элемент И 74.

Затем из канала 63 через шинные формирователи 69,,,..., 69 поступает дополнительный код числа слов, поступающий на информационные входы счетчиков 33, 12 и 13. Этот код сопровождается сигналом Вывод, который.проходит только через элемент И 74 селектора 70 адреса на стро- бирующий вход счетчика 33 числа слов, осу1цествляя запись в него выданной информации. Одновременно сигнал с выхода селектора 70 адреса через элемент ИЛИ 75 подается на входы ВШ шинных формирователей 69,,..., 69 выход А шинного формирователя 69.,, то обеспечивает поступление его в анал 63 в качестве сигнала СИП, извещающего вторую ЭВМ 64 о нормальном

завершении операции вывода. Аналогично заносится информация в счетчики 12 и 13, а также при вьщаче данных з первой ЭВМ 62 через шинные формиг ователи 69,,..., 69ц. Селекторы 70, 70 и 70д легко реализуются с спользованием в качестве схем 72 овпадения микросхем типа К 155 СП1, а счетчики 33, 12 и 13 - на базе микосхем К 155 ИЕ7.

ормула изобретения

Устройство для обмена двухмашинного вычислительного комплекса, содер-

7

v

1198

жащее первый и второй коммутаторы интерфейса, первьш триггер запроса, триггер направления обмена, первый триггер блокировки, счетчик числа слов, первый триггер запуска обмена и шесть элементов И, причем первый информационный вход-выход первого коммутатора интерфейса подключен к

1Q первому информационному входу-выходу устройства, первый вход первого элемента И соединен с первым выходом первого триггера блокировки, инверсный выход которого подключен к пер15 вому входу второго элемента И, выход первого элемента И соединен с входом записи единицы первого триггера запроса, первый вход третьего элемента И подключен к прямому выходу триг20 гера направления обмена, первый вход четвертого элемента И соединен с прямым выходом первого триггера запуска обмена, выход пятого элемента И подключен к первому управляющему

25 входу первого коммутатора интерфейса, выход шестого, элемента И соединен с входом записи единицы первого триггера блокировки, отличающееся тем, что, с целью повьш1е-.

30 ния скорости обмена данными путем . обеспечения режима прямого доступа к памяти обеих ЭВМ одновременно, в него введены два формирователя импульсов, три элемента задержки, тре- тий, четвертый и пятьш ком гутаторы интерфейса, два счетчика адреса, три элемента запрета, второй триггер блокировки, второй триггер запроса, второй триггер запуска обмена,триг40 гер требования обмена , триггер окончания обмена, четыре элемента ИЛИ и седьмой элемент И, прич ем первый информационный вход-выход второго коммутатора интерфейса подключен к

45 второму информационному входу-выходу устройства, второй информационный вход-выход первого коммутатора интерфейса соединен с вторьм информационным входом-выходом второго комgQ мутатора интерфейса, выход седьмого элемента И подключен к входу записи единицы второго триггера запроса, выход которого соединен с первым выходом запроса устройства, вход заgg писи нуля второго триггера запроса подключен к первому входу запроса , , ;устройства, выход третьего коммутатора интерфейса соединен с информационными входами счетчика числа слов.

3

147

первого счетчика адреса и второго счетчика адреса, выход которого подключен к информаццонному входу пятого коммутатора интерфейса выход пятого коммутатора интерфейса соединен с первьЕч адресным выходом устройства выход первого счетчика адреса подключен к информационног гу входу четвертого коммутатора интерфейса, выход которого соединен с вторым адрес. ньм входом устройства, первый инфор- маи онный вход третьего ко1 1мутатора интерфейса подключён к первому адресном / входу устройства, второй информационный вход третьего коммутатора соединен с вторым адресным входом устройства;, выход триггера направления обмена подключен к первому входу пято1 о элемента И инверсному входу первого элемента запрета и HHBepcHOf.r/ входу второго элемента запретаg выход первого элемента задержки соединен с вторым входом третьего элемента И и прямым входом первого элемента запретад выход четвертого элемента И подключен к входу первого элемента задерлски5 третьему управляющему входу первого коммутатора, интерфейса,,, третьем управляющему входу второго ком1х утатора интерфейса, управляющему входу четвертого KOMj.-ii TaTopa интерфейса, уп- равляющег-iiT, входу пятого ког-шутатора интерфейса и выходу разрешения обмена устройстваJ выход третьего элемента И соединен с первым управляющим входом второго коммутатора интерфейса;) второй управляющий вход кото-т рого подключен к выходу второго sJie- мента запретаJ второй управляющий вход первого коммутатора интерфейса соединен с выходом первого элемента запрета,, выход первого комг-гутато- ра интерфейса подключен ,к прямому, входу второго элемента запрета и первом;/ входу первого элемента ИЛИ второй вход которого соединен с вторым входом пятого элемента И и выходом второго KOMtiyTaTopa интерфей- сэ.} зькод первого элемента ИЛИ подключен к счетному Еходу триггера окончания обмена,, прямой выход ,кото рого соединен с входом первого формирователя импульсов,, выход ,пер9ого формирователя импульсов подключен к входу записи нуля триггера требования обмена, счетног у входу счетчика числа елоз,с счетному входу первого счетчи81

ка адреса, счетному входу второго счетчика адреса, входу записи нуля первого триггера запуска обмена, входу записи нуля второго триггера запуска обмена и входу третьего элемента задержки., выход которого соединен с прямым входом третьего элемента запрета, выход нуля счетчика числа слов подключен к входу второго формирователя импульсов и ин-.. версному входу третьего элемента запрета, выход которого соединен с первым входом второго элемента ИЛИ,

выход второго элемента ИЛИ подключен к входу записи единицы триггера требования обмена, прямой выход которого соединен с выходом требования обмена устройства, второй и третий

входы второго элемента ИЛИ подключены соответственно к первому и второму входам требования обмена устройства, вход записи единицы первого триггера запуска обмена соединен

с первым входом предоставления прямого доступа к памяти устройства, второй вход предоставления прямого доступа к памяти устройства подключен к входу записи единицы второго триггера запуска обмена., прямой выход которого соединен с вторым входом четвертого элемента И, .первый и второй входы третьего элемента ИЛИ подключены соответственно к первому и

второму входам первого направления обмена устройства, первый и второй входы четвертого элемента ИЛИ подключены соответственно к первому и BTopoMjj- вход.ам второго направления

обмена устройства, третьего элемента ИЛИ соединен с входом записи единицы триггера направления обмена5 вход записи нуля которого подключен к выходу четвертого ИЛИ, выход . второго формирователя импульсов соединен с входом второго элемента задержки, вторым входом первого элемен га И и первым входом седьмого элемента Hj вькод

второго элемента задержки подключен к входу записи нуля первого триггера блокировки и входу записи нуля второго триггера блокировки, прямой выход которого соединен с вторым вхоом седьмого элемента И первым уп- равлянщим входом третьего коммутато- ра интерфейса и первьм выходом блокиров- ки устройства, второй выход блокировки устройства соединен с прямьйм выходом

I 5

первого триггера блокировки и вторым управляющим входом третьего коммутатора интерфейса, вход записи единицы второго триггера блокировки под ключен к выходу второго элемента И, второй вход которого является первым входом блокировки устройства, инверсный выход второго триггера

OmSJi.O

1198

блокировки подключен к первому входу шестого элемента И, второй вход кото - рого является вторым входом блокиров ки устройства, вход записи нуля и прямой выход первого триггера запроса являются соответственно вторым входом запроса и вторым выходом запроса устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный аналого-цифровой преобразователь | 1988 |

|

SU1612373A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство оперативной связи с управляющими программами | 1981 |

|

SU970351A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для вывода информации на фототелеграфный аппарат | 1983 |

|

SU1161935A1 |

Изобретение относится к вычислительной технике и предназначено для объединения двух ЭВМ. Целью изобретения является повышение скорости обмена данными путем реализации прямого доступа к памяти обеих ЭВМ одновременно и исключения участия одной из них в обмене в режиме программного управления вводом или выводом данных. Цель достигается тем, что в устройство, содержащее два коммутатора интерфейса 1,2, триггер запроса 8, триггер направления обмена 34, триггер блокировки 6, счетчик числа слов 33, триггер запуска обмена 10 и шесть элементов И 26-31, дополнительно введены два формирователя импульсов 24,25, три элемента задержки 14-16, три коммутатора интерфейса 3-5, два счетчика адреса 12,13, три элемента запрета 17-19, триггер блокировки 7, триггер запроса 9, триггер запуска обмена 11, триггер требования обмена 35, триггер окончания обмена 36, четыре элемента ИЛИ 20-23 и элемент И 32. 4 ил.

К каналу S1

KKainuffS3

Ц}и г..

Ki/.5

.if

и.г.5

gb/A.(.g S.f/f. 28(17) BbiK.ffl,2(l} Ui

BbtK. fn, 30 (iff) BblX,f/l.i(l)

8bij(,d/l.2

Фигл

Авторы

Даты

1989-04-07—Публикация

1987-09-30—Подача