Изобретение относится к вычислительной технике и может быть использовано для подключения устройств ввода-вывода (УВЕ) к многосегментной магистрали управляющих вычислительных комплексов с последовательным арбитражем.

Цель изобретения - повышение пропускной способности многосегментной магистрали за счет сокращения времени арбитража, времени доступа УВВ, подключенных к внепроцессорному уровню к ресурсам системы, и уменьшению задержек, вносимых при расшире НИИ магистрали,

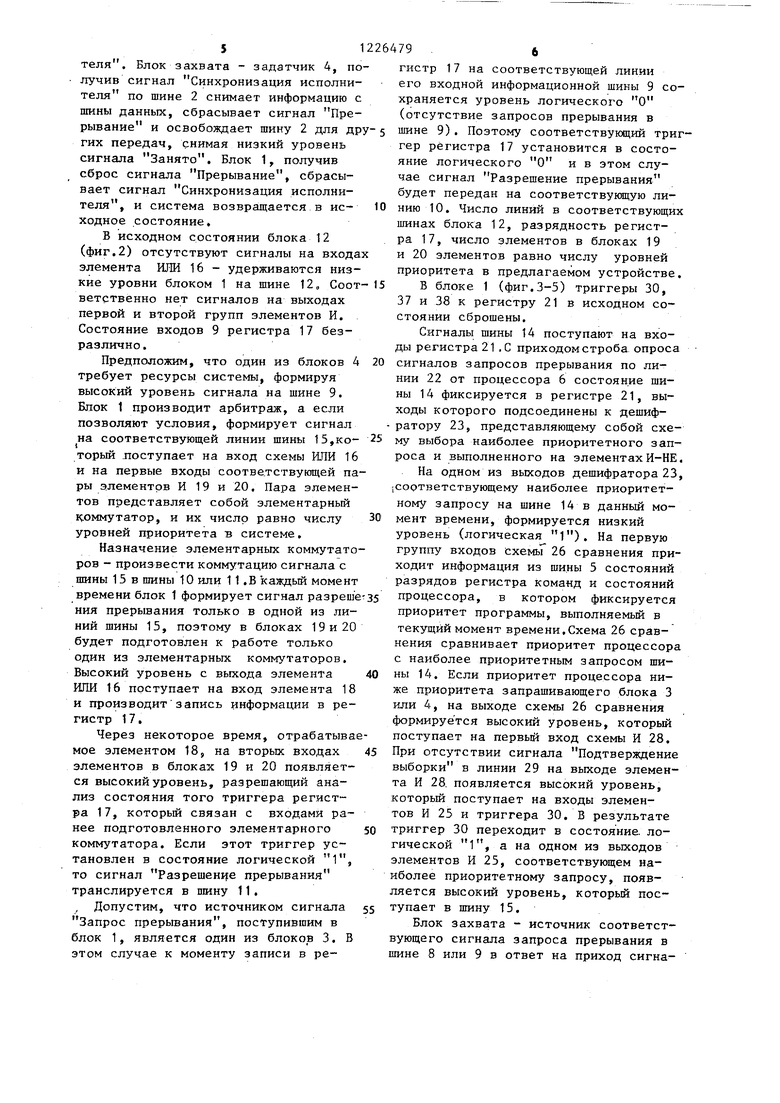

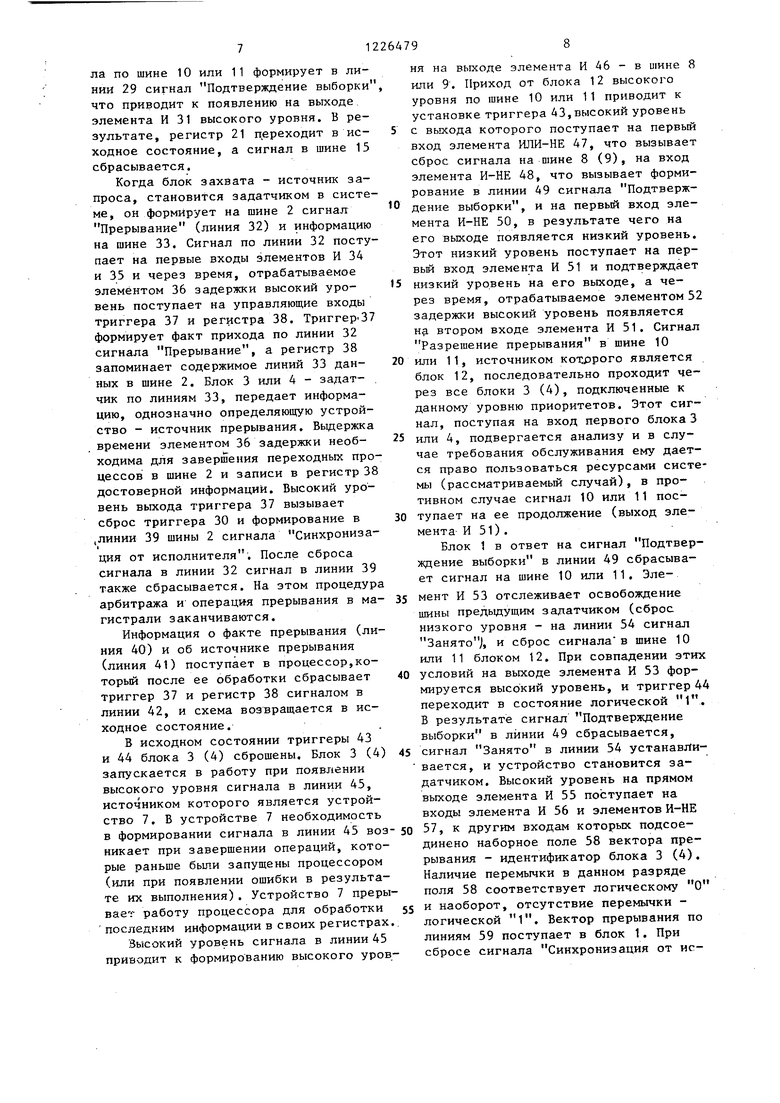

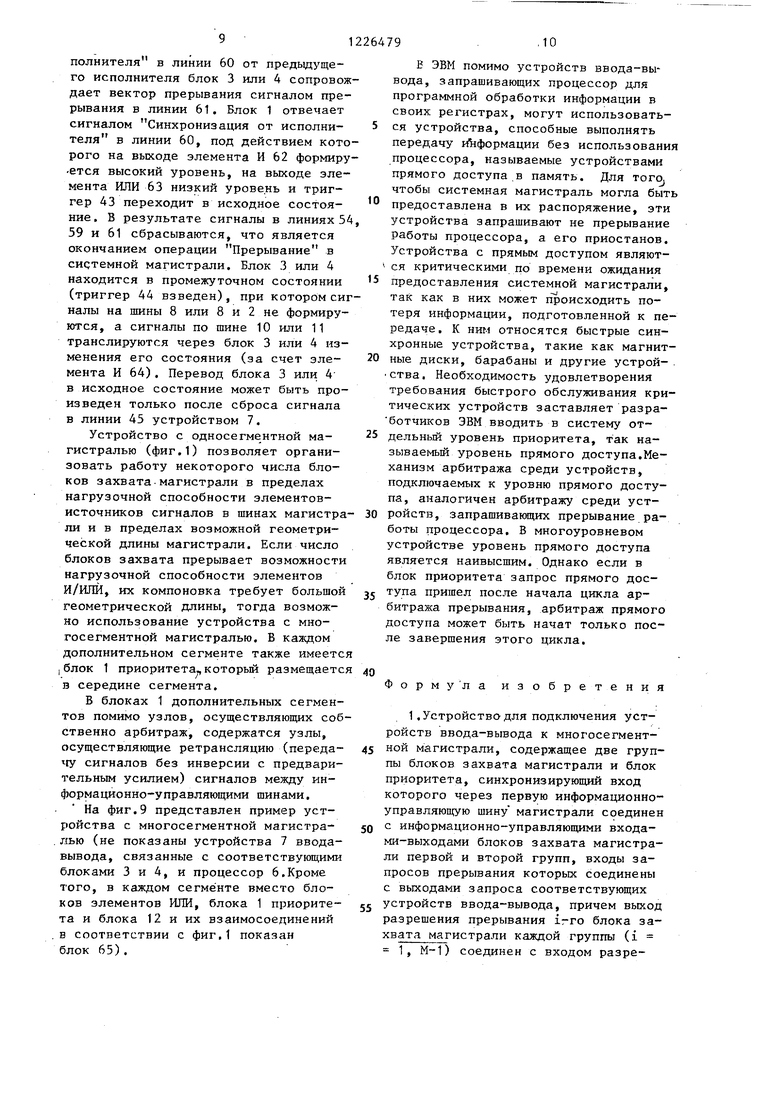

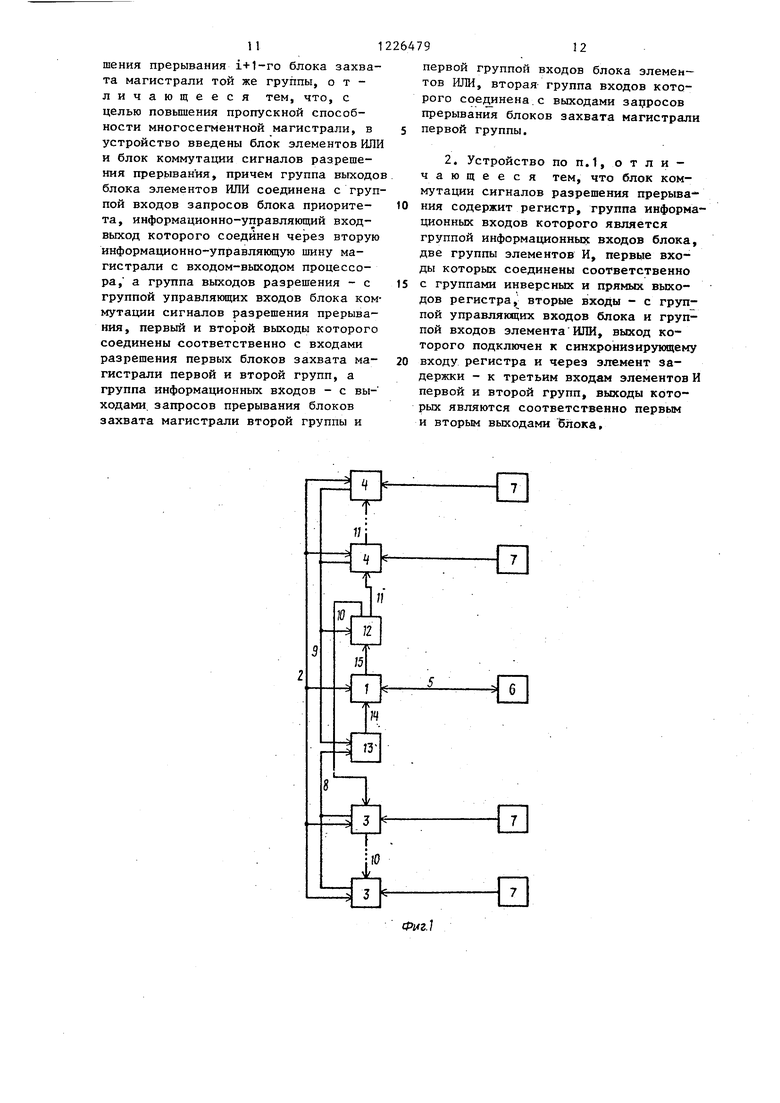

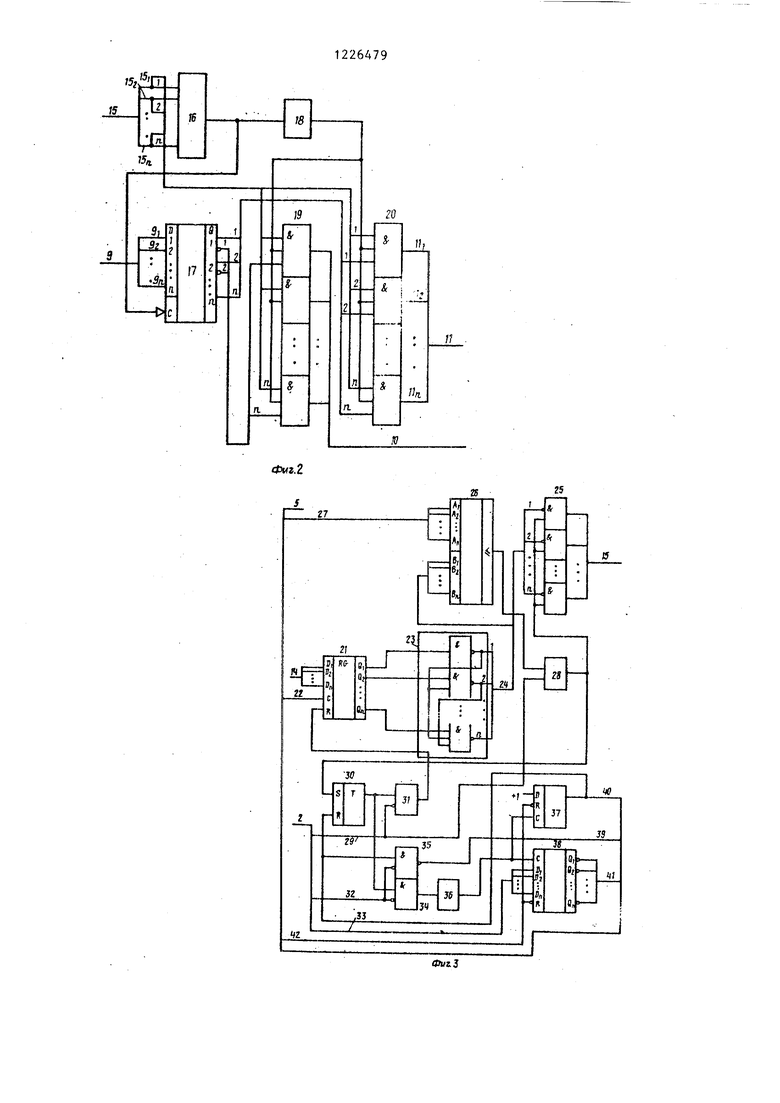

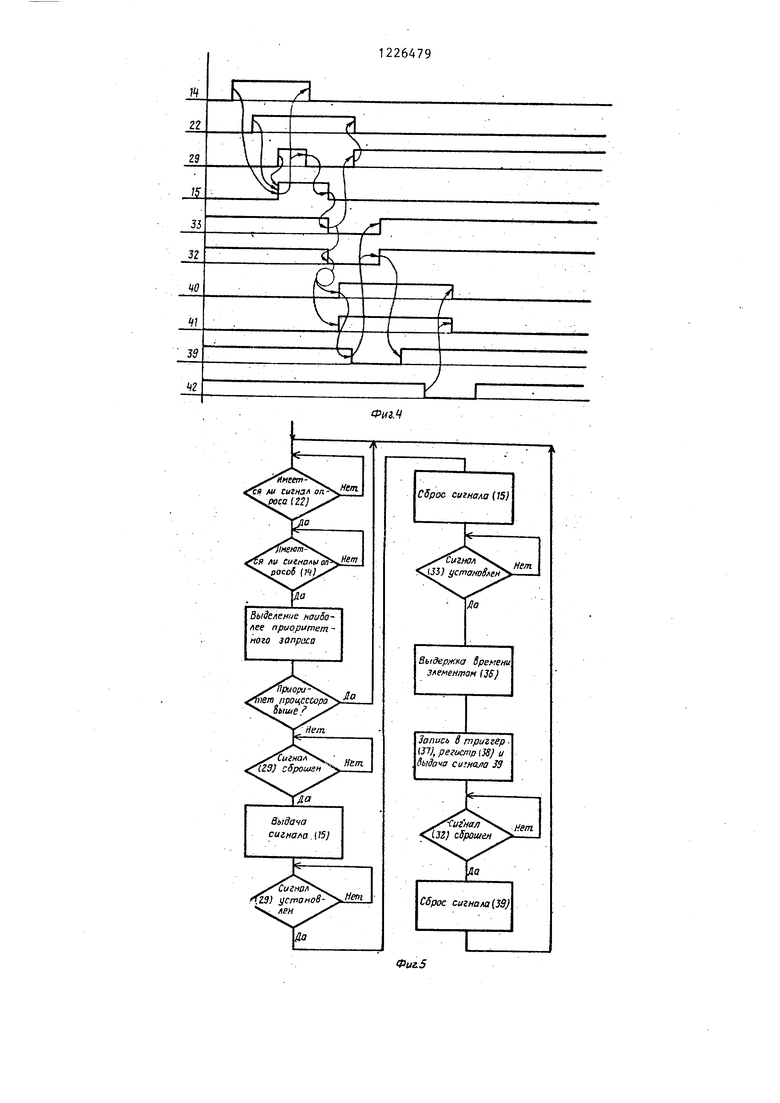

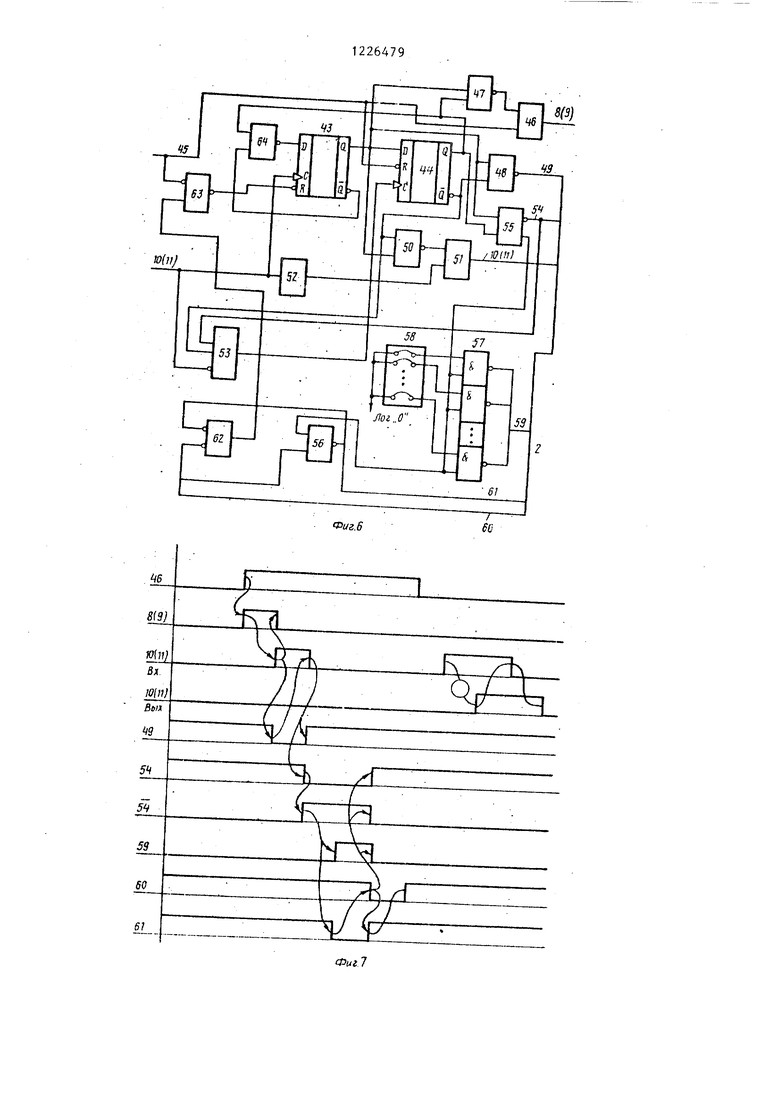

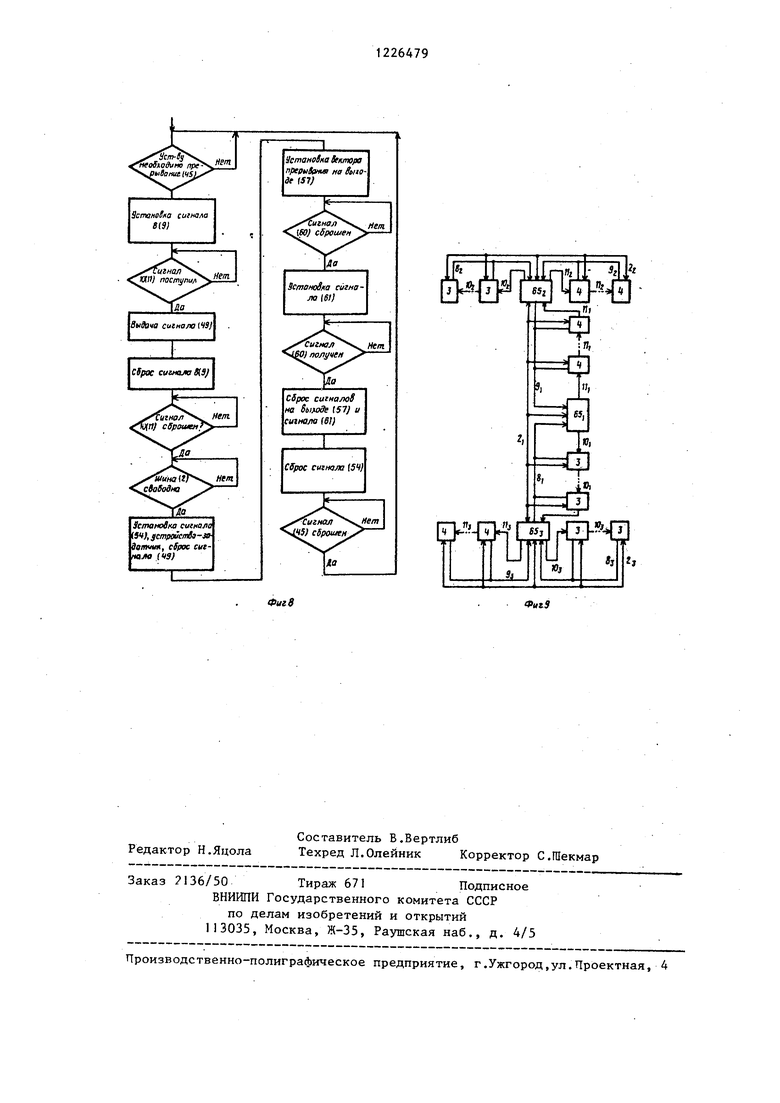

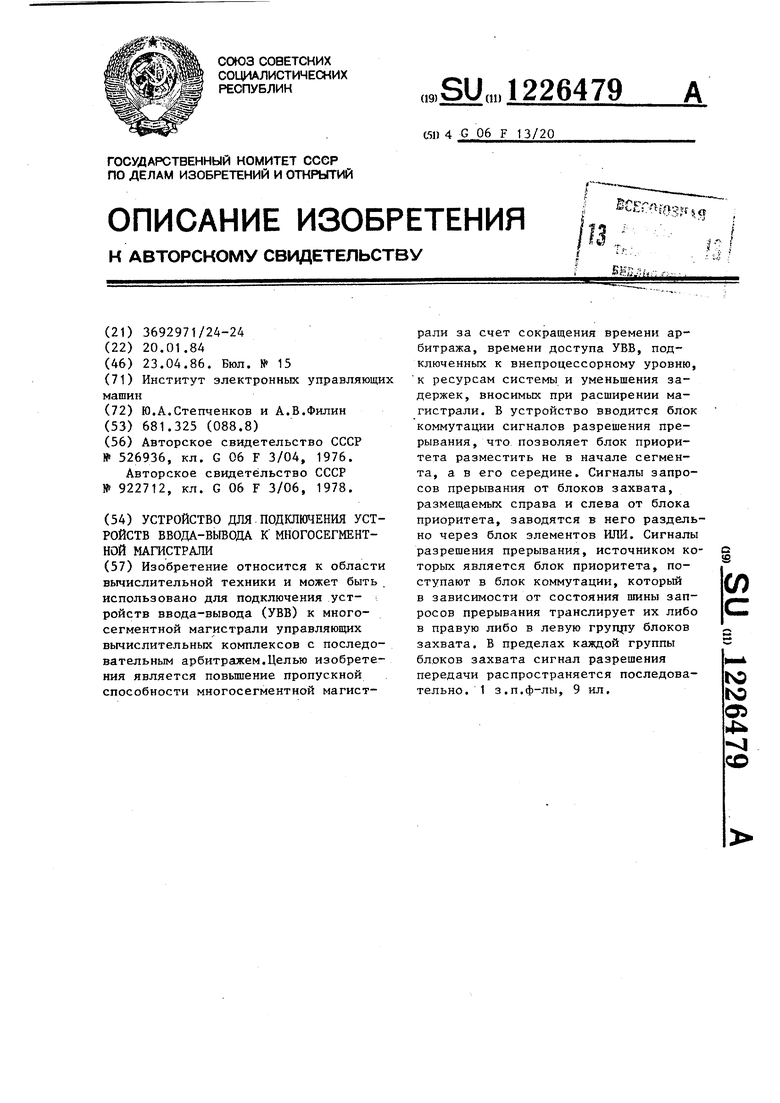

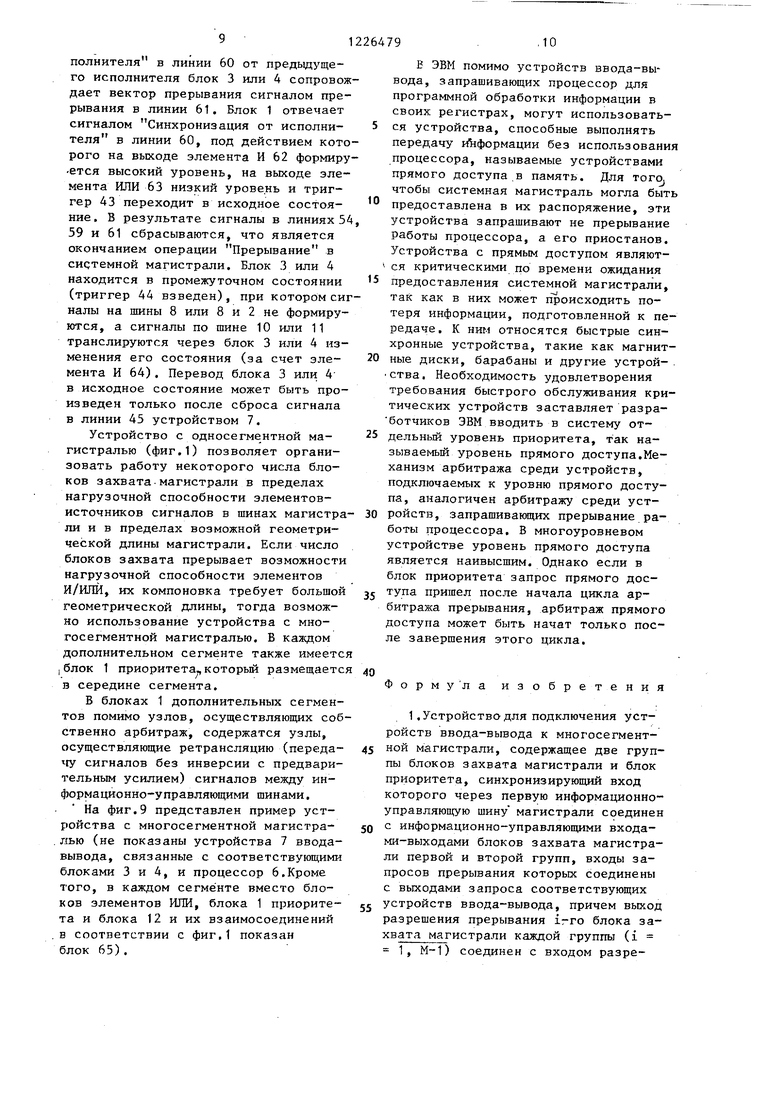

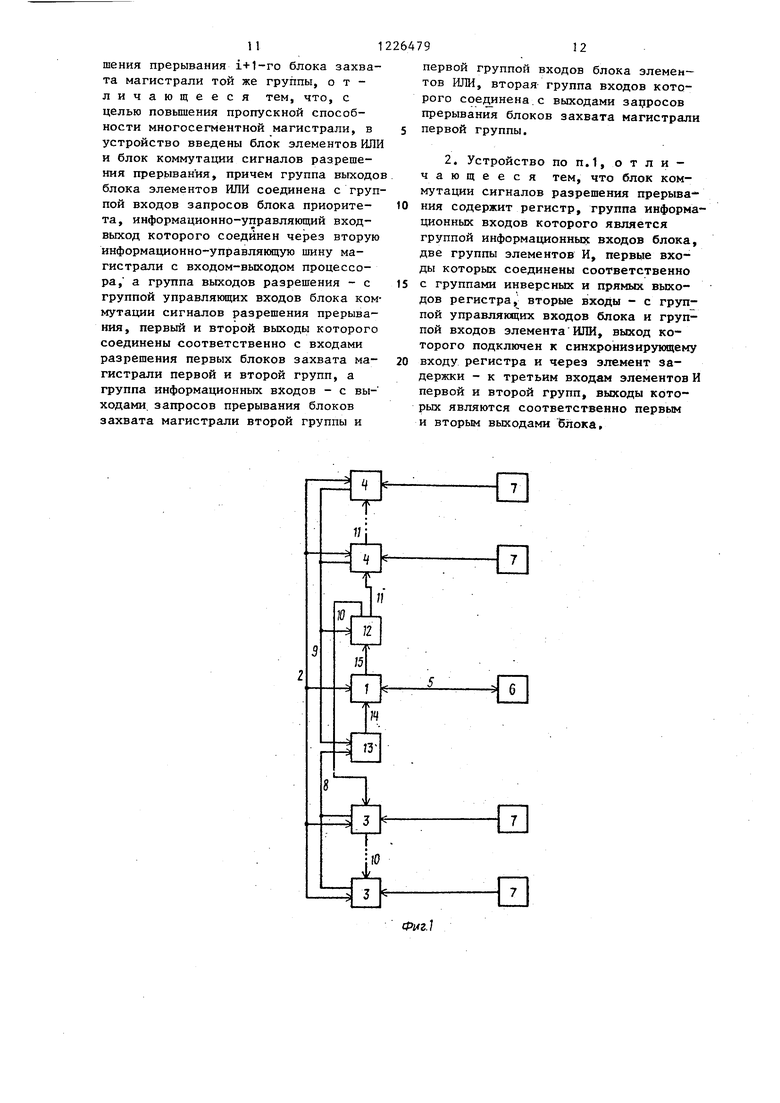

На фиг,1 приведена блок-схема устройства; на фиг.2 и 3 - функциональные схемы блока коммутации сигналов разрешения прерывания и блока приоритета; на фиг.4 и 5 - временная диаграмма и блок-схема алгоритма работы блока приоритета; на фиг.6-8 функциональная схема, временная диаграмма и блок-схема алгоритма работы блока захвата магистрали; на фиг.9 - пример многосегментной магистрали, использующей предлагаемое устройство.

Устройство (фиг.1) содержит блок приоритета, первую информационно-управляющую шину 2 магистрали, блоки 3 и 4 захвата магистрали первой и второй групп, вторую информационно-управляющую шину 5 магистрали, процес- сор 6, устройства 7 ввода-вывода, первую и вторую шины 8 и 9 запросов прерывания, первую и вторую шины 10 и 11 разрешений прерывания, блок 12 коммутации сигналов разрешения прерывания, блок 13 элементов ИЛИ, шины 14 и 15 запросов и разрешений прерьшания.

Блок 12 (фиг.2) содержит элемент ИЛИ 16, регистр 17, элемент 18 задержки и первую 19 и вторую 20 группы элементов И,

Блок 1 (фиг.З) содержит регистр 2 запросов прерывания, управляющий вход 22 регистра 21, дешифратор 23, вторую шину 24 дешифратора 23,, элементы И 25, схему 26 сравнения, первую группу входов 27 схемы 26, элемент И 28, линию 29 сигнала Подтверждение выборки, триггер 30, элемент И 31, вторую линию 32 сигнала Прерывание, входную шину 33 данных элементы И 34 и 35, элементы 36 задержки, триггер 37, регистр 38, линию 39 сигнала Синхронизация исполнителя, вьтходную линию 40 сигнала Прерывание, выходную шину 41 данных и линию 42 сброса.

Блок 3 (4) (фиг.6) содержит триггеры 43 и 44, линию 45 сигнала Запрос прерывания элемент И 46, элемент ИЛИ-НЕ 47, элемент И 48, линию 49 сигнала Подтверждение выборки,

элементы И-НЕ 50, элемент И 51, элементы 52 задержки, элементы И 53, линию 54 сигнала Занято, элемент И 55,, элемент И-НЕ 56, элементы И-НЕ 57, наборное поле 58 вектора

прерывания, шину 59 данных, линию 60 сигнала Синхронизация исполнителя, линию 61 сигнала Прерывание, элемент И-НЕ 62, элемент ИЛИ-НЕ 63 и элемент И-НЕ 64.

Устройство работает следующим образом,

В отличие от известного в предлагаемом устройстве блок 1 располагается не в начале сегмента, а в его

середине (фиг,1). Это достигается за счет введения блока 12, блока 13 и изменения характера подключения блока 1 к шинам запросов и разрешений прерывания магистрали.

В устройстве для организации параллельной работы высокопроизводительного процессора 6 с устройствами. 7 используется многоуровневая система прерываний. В качестве устройства 7 могут быть использованы как медленно действующие устройства ввода-вывода, запрещающие прерывание работы процессора 6 на обработку информации в своих регистрах, так и

высокоскоростные; устройства внепро- цессорного уровня, запрашивающие блок 1 об использовании шины 2. Если у устройства 7 появилась необходи- г мость прервать работу процессора, то

оно инициирует работу соответствующего блока 3 или 4, Первая группа блоков 3 запрашивает прерывание,формируя высокий уровень на шину 9, а вторая группа блоков 4 - на вторую

шину 8. Запросы прерывания от первой и второй групп блоков 3 и 4, подключенные к соответствующему уровню приоритета,, объединяются блоком 13 и по шине 14 поступают в блок 1, который про1- з водит их арбитраж - выделение наиболее приоритетного уровня. Процесс арбитража начинается с приводом высокого уровня синхрониэирующего сигнала по шине 5 от процессора 6, В результате арбитража на одной из линий шины 15, соответствующей наиболее приоритетному поступившему запросу, в блоке 1 появляется высокий уровень, которьй поступает в блок 12. В каждом цикле арбитража высокий уровень в шине 15 может быть только на одной из линий, соответствующей наиболее приоритетному запросу.

Назначение блока 12 состоит в. трансляции сигнала разрешения прерывания с шины 15 либо в первую 10, либо во вторую 11 шину разрешений прерывания. Появление высокого уровня в шине 15 представля ет собой результат реакции блока 1 на запрос на прерывание, поступивший или от группы блоков-3,или от группы блоков 4-, или от обеих групп одновременно. Информационный вход блока 12 подсоединен к шине 9. Такой способ подключения блока 12 означает, что приоритет блоков 4 выше приоритета блоков 3, подключенных к одному и тому же системному уровню. Поэтому при наличии высокого уровня на соответствующей линии второй шины запросов пре- рывания (имеется запрос от второй, группы блоков захв.ата) сигнал разрешения прерывания буде.т передан на ши- ну 11.

К каждому системному приоритетному уровню может быть подключено достаточно большое (в архитектурном смысле неограниченное) число блоков захвата. Чтобы блок приоритета (имеется в виду известное устройство или блок коммутации в предлагаемом) мог выделить из группы запрашивающих блоков захвата, подключенных к данному уровню приоритета, блок захвата, имеющий высший приоритет на данном уровне приоритета, в систему вводятся однонаправленные шины 10 и 11, число которых равно числу уровней приоритета Эти шины последовательно проходят через все блоки захвата, подключенные к данному уровню приоритета, причем чем ближе в электрической цепи к блоку 12 находится блок 3 или 4, тем более высокий приоритет на данном уровне он имеет.

Высокий уровень сигнала на шине 11 (при наличии запроса от блоков 4) поступает на вход первого блока 4 из второй группы, в котором он подвергается анализу. Если устройство 7,

связанное с данным блоком захвата, не-является источником сигнала на шине 9, то высокий уровень передается на продолжение шины 9 на вход следующего блока в данной группе. И так до тех пор, пока не достигнет блока захвата, который запрашивает прерывание. Запрашивающий блок 4 запрещает дальнейшую трансляцию сигнала по шине 11

и отвечает блоку 1 формированием низкого УРОВНЯ сигнала Подтверждение выборки на шине 2, в ответ на который блок 1 сбрасывает сигнал на шине 15 (устанавливает низкий уровень) ,

что вызывает сброс сигнала на шине 11 блоком 12.

В рассматриваемой системе принцип связи между устройствами асинхронный. В каждый момент времени в системе могут обмениваться только два устройства. Одно устройство управляет передачей информации по магистрали системы и является задающим (задатчик), другое устройство, привлекаемое к этой передаче, становится исполнительным устройством (исполнитель). Каждый задатчик при работе с исполнителем формирует на соответствующей линии ши- ны 12 сигнал Занято, и-нформируя все

устройства системы, что магистраль системы занята. Когда задатчик заканчивает обмен информацией с исполнителем, он сбрасывает сигнал Загшто и одно из устройств системы, имеющее

самый высший приоритет в данный момент времени среди прочих устройств, которым необходима магистраль системы, становится задатчиком. Выбранное устройство, которое в результате

арбитража сформировало сигнал Подтверждение выборки, является будущим задатчиком, которое станет тако- - вым после освобождения шины 12 текущим задатчиком.

Блок захвата - задатчик - формирует на первой информационной шине свой сигнал Занято, сбрасывает сигнал Подтверждение выборки, вьщает на шину данных информацию, однозначно

определяющую блок, захвата - источник прерывания, и стробйрует ее синхронизирующим сигналом Прерывание. Блок 1, получив сигнал Прерывание, производит вьщержку времени, достаточную для окончания переходных процессов в шине 2, принимает данные и отвечает задатчику синхронизирующим сигналом Синхронизация от исполнителя. Блок захвата - задатчик 4, получив сигнал Синхронизация исполнителя по шине 2 снимает информацию с шины данных, сбрасывает сигнал Прерывание и освобождает шину 2 для дру-5 шине 9) . Поэтому соответствующий триггих передач, снимая низкий уровень сигнала Занято. Блок 1, получив сброс сигнала Прерывание, сбрасывает сигнал Синхронизация исполнителя

и система возвраш;ается в исходное состояние.

В исходном состоянии блока 12 (фиг.2) отсутствуют сигналы на входах элемента ИЛИ 16 - удерживаются низкие уровни блоком 1 на шине 12 Соот- ветственно нет сигналов на выходах первой и второй групп элементов И. Состояние входов 9 регистра 17 безразлично.

Предположим, что один из блоков 4 требует ресурсы системы, формируя высокий уровень сигнала на шине 9. Блок 1 производит арбитраж, а если позволяют условия, формирует сигнал на соответствующей линии шины 15,ко- торый .поступает на вход схемы ИЛИ 16 и на первые входы соответствующей пары элементов И 19 и 20. Пара элементов представляет собой элементарный коммутатор, и их число равно числу уровней приоритета в системе.

Назначение элементарных коммутаторов - произвести коммутацию сигнала с шины 15 в шины 10 или 11 .В каждый момент времени блок 1 формирует сигнал разреше ния прерьшания только в одной из линий шины 15, поэтому в блоках 19 и 20 будет подготовлен к работе только один из элементарных коммутаторов. Высокий уровень с выхода элемента ИЛИ 16 поступает на вход элемента 18 и производит запись информации в регистр 17.

Через некоторое время, отрабатываемое элементом 18, на вторых входах элементов в блоках 19 и 20 появляется высокий уровень, разрешающий анализ состояния того триггера регистра 17, который связан с входами ранее подготовленного элементарного коммутатора. Если этот триггер установлен в состояние логической 1, то сигнал Разрешен1 е прерывания транслируется в шину 11.

Допустим, что источником сигнала Запрос прерывания, поступившим в блок 1, является один из блоков 3. В этом случае к моменту записи в регистр 17 на соответствующей линии его входной информационной шины 9 сохраняется уровень логического О (отсутствие запросов прерывания в

0

5

0 5 0

з 0

5 0

гер регистра 17 установится в состояние логического О и в этом случае сигнал Разрешение прерывания будет передан на соответствующую линию 10. Число линий в соответствующих шинах блока 12, разрядность регистра 17, число элементов в блоках 19 и 20 элементов равно числу уровней приоритета в предлагаемом устройстве.

В блоке 1 (фиг.3-5) триггеры 30, 37 и 38 к регистру 21 в исходном состоянии сброшены.

Сигналы шины 14 поступают на входы регистра 21 ,С приходомстроба опроса сигналов запросов прерывания по линии 22 от процессора 6 состояние шины 14 фиксируется в регистре 21, выходы которого подсоединены к дешифратору 23, представляющему собой схему выбора наиболее приоритетного запроса и выполненного на элементах И-НЕ.

На одном из выходов дешифратора 23, -.соответствующему наиболее приоритетному запросу на шине 14 в данньй момент времени, формируется низкий уровень (логическая 1). На первую группу входов схемьГ 26 сравнения приходит информация из шины 5 состояний разрядов регистра команд и состояний процессора, в котором фиксируется приоритет программы, выполняемьй в текущий момент времени.Схема 26 сравнения сравнивает приоритет процессора с наиболее приоритетным запросом шины 14. Если приоритет процессора ниже приоритета запрашивающего блока 3 или 4, на выходе схемы 26 сравнения формируется высокий уровень, который поступает на первьй вход схемь: И 28. При отсутствии сигнала Подтверждение выборки в линии 29 на выходе элемента И 28. появляется высокий уровень, которьй поступает на входы элементов И 25 и триггера 30. В результате триггер 30 переходит в состояние, логической 1, а на одном из выходов элементов И 25, соответствующем наиболее приоритетному запросу, появляется высокий уровень, которьй поступает в шину 15.

Блок захвата - источник соответствующего сигнала запроса прерывания в шине 8 или 9 в ответ на приход сигнала по шине 10 или 11 формирует в линии 29 сигнал Подтверждение выборки что приводит к появлению на выходе элемента И 31 высокого уровня. В результате, регистр 21 переходит в ис- ходное состояние, а сигнал в шине 15 сбрасывается.

Когда блок захвата - источник запроса, становится задатчиком в системе, он формирует на шине 2 сигнал Прерывание (линия 32) и информацию на шине 33. Сигнал по линии 32 поступает на первые входы элементов И 34 и 35 и через время, отрабатываемое элементом 36 задержки высокий уро- вень поступает на управляющие входы триггера 37 и регистра 38. Триггер 37 формирует факт прихода по линии 32 сигнала Прерывание, а регистр 38 запоминает содержимое линий 33 дан- ных в шине 2. Блок 3 или 4 - задат- . чик по линиям 33, передает информацию, однозначно определяющую устройство - источник прерывания. Вьщержка времени элементом 36 задержки необ- ходима для завершения переходных процессов в шине 2 и записи в регистр 38 достоверной информации. Высокий уровень вьпсода триггера 37 вызывает сброс триггера 30 и формирование в (ЛИНИИ 39 шины 2 сигнала СинхронизаI

ция от исполнителя. После сброса сигнала в линии 32 сигнал в линии 39 также сбрасывается. На этом процедура арбитража и операция прерывания в ма- гистрали заканчиваются.

Информация о факте прерывания (линия 40) и об источнике прерывания (линия 41) поступает в процессор,который после ее обработки сбрасывает триггер 37 и регистр 38 сигналом в линии 42, и схема возвращается в исходное состояние.

Б исходном состоянии триггеры 43 и 44 блока 3 (4) сброшены. Блок 3 (4) запускается в работу при появлении высокого уровня сигнала в линии 45, источником которого является устройство 7. В устройстве 7 необходимость в формировании сигнала в линии 45 воз никает при завершении операций, которые раньше были запущены процессором (или при появлении ошибки в результате их выполнения). Устройство 7 прерывает работу процессора для обработки последним информации в своих регистрах

Высокий уровень сигнала в линии 45 приводит к формированию высокого уровня на выходе элемента И 46 - в шине 8 или 9. Приход от блока 12 высокого уровня по шине 10 или 11 приводит к установке триггера 43, высокий уровень с выхода которого поступает на первый вход элемента ИЛИ-НЕ 47, что вызывает сброс сигнала на шине 8 (9), на вход элемента И-НЕ 48, что вызывает формирование в линии 49 сигнала Подтверждение выборки, и на первый вход элемента И-НЕ 50, в результате чего на его выходе появляется низкий уровень. Этот низкий уровень поступает на пер- вьй вход элемента И 51 и подтверждает низкий уровень на его выходе, а через время, отрабатываемое элементом 52 задержки высокий уровень появляется н втором входе элемента И 51. Сигнал Разрешение прерывания в шине 10 или 11, источником кохррого является блок 12, последовательно проходит через все блоки 3 (4), подключенные к данному уровню приоритетов. Этот сигнал, поступая на вход первого блока 3 или 4, подвергается анализу и в случае требования обслуживания ему дается право пользоваться ресурсами системы (рассматриваемый случай), в противном случае сигнал 10 или 11 поступает на ее продолжение (выход элемента И 51) .

Блок 1 в ответ на сигнал Подтверждение выборки в линии 49 сбрасывает сигнал на шине 10 или 11. Элемент И 53 отслеживает освобождение шины предыдущим задатчиком (сброс низкого уровня - на линии 54 сигнал Занято, и сброс сигнала в шине 10 или 11 блоком 12. При совпадении этих условий на выходе элемента И 53 формируется высокий уровень, и триггер 44 переходит в состояние логической 1. Б результате сигнал Подтверждение выборки в линии 49 сбрасывается, сигнал Занято в линии 54 устанавливается, и устройство становится задатчиком. Высокий уровень на прямом выходе элемента И 55 поступает на входы элемента И 56 и элементов И-НЕ 57, к другим входам которых подсоединено наборное поле 58 вектора прерывания - идентификатор блока 3 (4). Наличие перемычки в данном разряде поля 58 соответствует логическому О и наоборот, отсутствие перемычки - логической 1. Вектор прерывания по линиям 59 поступает в блок 1. При сбросе сигнала Синхронизация от исот предыдуще- или 4 сопровож

полнителя в линии 60 го исполнителя блок 3 дает вектор прерывания сигналом прерывания в линии 61. Блок 1 отвечает сигналом Синхронизация от исполни- теля в линии 60, под действием которого на выходе элемента И 62 формиру ется высокий уровень, на выходе элемента ИЛИ 63 низкий уровень и триггер 43 переходит в исходное состоя- ние, В результате сигналы в линиях 5 59 и 61 сбрасываются, что является окончанием операции Прерывание в системной магистрали. Блок 3 или 4 находится в промежуточном состоянии (триггер 44 взведен), при котором синалы на шины 8 или 8 и 2 не формируются, а сигналы по шине 10 или 11 транслируются через блок 3 или 4 изменения его состояния (за счет элемента И 64). Перевод блока 3 или 4 в исходное состояние может быть произведен только после сброса сигнала в линии 45 устройством 7.

Устройство с односегментной магистралью (фиг.1) позволяет организовать работу некоторого числа блоков захвата.магистрали в пределах нагрузочной способности элементов- источников сигналов в шинах магистрали и в пределах возможной геометрической длины магистрали. Если число блоков захвата прерывает возможности нагрузочной способности элементов И/ИЛИ, их компоновка требует большой геометрической длины, тогда возможно использование устройства с многосегментной магистралью. В каждом дополнительном сегменте также имеетс I блок 1 приоритета,которьй размещаетс в середине сегмента.

В блоках 1 дополнительных сегментов помимо узлов, осуществляющих собственно арбитраж, содержатся узлы, осуществляющие ретрансляцию (переда- ty сигналов без инверсии с предварительным усилием) сигналов между информационно-управляющими шинами.

На фиг.9 представлен пример устройства с многосегментной магистра- лью (не показаны устройства 7 ввода- вывода, связанные с соответствующими блоками 3 и 4, и процессор 6.Кроме того, в каждом сегменте вместо блоков элементов ИЛИ, блока 1 приорите- та и блока 12 и их взаимосоединений в соответствии с фиг,1 показан блок 65) .

Е ЭВМ помимо устройств ввода-вывода, запрашивающих процессор для программной обработки информации в своих регистрах, могут использоваться устройства, способные выполнять передачу информации без использования процессора, называемые устройствами прямого доступа в память. Для тога чтобы системная магистраль могла быть предоставлена в их распоряжение, эти устройства запрашивают не прерывание работы процессора, а его приостанов. Устройства с прямым доступом являют- ся критическими по времени ожидания

предоставления системной магистрали, так как в них может происходить потеря информации, подготовленной к передаче. К ним относятся быстрые синхронные устройства, такие как магнитные диски, барабаны и другие устрой- . ства. Необходимость удовлетворения требования быстрого обслуживания критических устройств заставляет разработчиков ЭВМ вводить в систему отдельный уровень приоритета, так на- зывае1чый уровень прямого доступа.Механизм арбитража среди устройств, подключаемых к уровню прямого доступа, аналогичен арбитражу среди уст- ройств, запрашивающих прерывание работы процессора. В многоуровневом устройстве уровень прямого доступа является наивысшим. Однако если в блок приоритета запрос прямого доступа пришел после начала цикла арбитража прерывания, арбитраж прямого доступа может быть начат только после завершения этого цикла.

Форму л а изобретения

1.Устройстводля подключения устройств ввода-вывода к многосегментной магистрали, содержащее две группы блоков захвата магистрали и блок приоритета, синхронизирующий вход которого через первую информационно- управляюшую шину магистрали соединен с информгщионно-управляющими входами-выходами блоков захвата магистрали первой и второй групп, входы запросов прерывания которых соединены с выходами запроса соответствующих устройств ввода-вывода, причем выход разрешения прерывания irro блока за- хвата магистрали каждой группы (i М-1) соединен с входом разрешения прерывания i+1-го блока захвата магистрали той же группы, отличающееся тем, что, с целью повышения пропускной способности многосегментной магистрали, в устройство введены блок элементов ИЛИ и блок коммутации сигналов разрешения прерывания, причем группа выходов блока элементов ИЛИ соединена с группой входов запросов блока приоритета, информационно-управляющий вход- выход которого соединен через вторую информационно-управляющую шину магистрали с входом-выходом процессора, а группа выходов разрешения - с группой управлякицих входов блока коммутации сигналов разрешения прерывания, первый и второй выходы которого соединены соответственно с входами разрешения первых блоков захвата магистрали первой и второй групп, а группа информационных входов - с выходами запросов прерывания блоков захвата магистрали второй группы и

первой группой входов блока элементов ИЛИ, вторая группа входов которого соединена.с выходами запросов прерывания блоков захвата магистрали первой группы.

2. Устройство по п.1, о т л и - чающееся тем, что блок коммутации сигналов разрешения прерывания содержит регистр, труппа информационных входов которого является группой информационньк входов блока, две группы элементов И, первые входы которых соединены соответственно

с группами инверсных и прямых выходов регистра, вторые входы - с группой управляющих входов блока и группой входов элемента ИЛИ, выход которого подключен к синхронизирующему

входу регистра и через элемент задержки - к третьим входам элементов И первой и второй групп, выходы которых являются соответственно первым и вторым выходами блока.

ФигЛ

1226479

Фиг.6

Т 60

61

Устано яа Itiunopa npeptilOHUf на ft/ia-, dtlS7}

Зстгювка fuenajiA fS4),3Ctni oui:inet-ja aomuiat, cfpac cut-

ПМ (49)

т.

Фигв

Редактор Н.Яцола

Составитель В.Вертлиб

Техред Л.Олейник Корректор С.Шекмар

Заказ 2136/50 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород,ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Многоканальное устройство приоритетного обслуживания | 1989 |

|

SU1675886A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| Устройство управления передачей информации в резервированной многопроцессорной вычислительной системе | 1988 |

|

SU1562923A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1427368A1 |

| Процессор для мультипроцессорной системы | 1988 |

|

SU1541626A1 |

Изобретение относится к области вычислительной техники и может быть . использовано для подключения устройств ввода-вывода (УВВ) к многосегментной магистрали управляющих вычислительных комплексов с последовательным арбитражем.Целью изобретения является повьшение пропускной способности многосегментной магистрали за счет сокращения времени арбитража, времени доступа УВВ, подключенных к внепроцессорному уровню, к ресурсам системы и уменьшения задержек, вносимых при расширении магистрали. В устройство вводится блок коммутации сигналов разрешения прерывания, что позволяет блок приоритета разместить не в начале сегмента, а в его середине. Сигналы запросов прерывания от блоков захвата, размещаемых справа и слева от блока приоритета, заводятся в него раздельно через блок элементов ШШ. Сигналы разрешения прерывания, источником которых является блок приоритета, поступают в блок коммутации, который в зависимости от состояния шины запросов прерывания транслирует их либо в правую либо в левую грущгу блоков захвата. В пределах каждой группы блоков захвата сигнал разрешения передачи распространяется последовательно. 1 з.п.ф-лы, 9 ил. сл to tc сх со

| Устройство для приема и передачи информации | 1975 |

|

SU526936A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система обработки информации | 1978 |

|

SU922712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-01-20—Подача