1

(21)4683075/24

(22)24.04.89

(46) 30.04.91. Бюл, Р 16

(71)Житомирский филиал Киевского политехнического института

(72)Л.В.Корчев, И.А.Коноплицкий и Ю„С.Каневский

(53) 681.32(088.8)

(56) Авторское свидетельство СССР

Р 1196894, кл. G 06 F 15/332, 1984.

Системы параллельной обработки/Под ред. Д.Ивенса. - М.: Мир, с. 349,

27

- -,7

(54) УСТРОЙСТВО Для ВЫЧИСЛЕ1ИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ (57) Изобретение относится к вычислительной технике, предназначено для вычисления одномерного и двумерного ДРФ и может быть использовано в системах цифровой обработки различного рода сигналов. Цель изобретения - расширение Функциональных возможностей за счет вычисления двумерного дискретного преобразования Фурье. Поставленная цель достигается за счет того.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1781684A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1721610A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1988 |

|

SU1589289A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1596347A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1545230A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1988 |

|

SU1575202A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1644158A1 |

26

2k 1

207

М

§ (Л

I

-Н ш

С

15 M-i

Ш

СП

х 0} J

л

221

что в устройство входят блок управления, N (N - рцзмер преобразования), вычислительных модулей 3.1-3.N, каждый из которых содержит буферный регистр 8, умножитель 9, блок 10 постоянной памяти коэффициентов, сум

Изобретение относится к вычислительной технике, предназначено для вычисления двумерного и одномерного ДПФ и может быть использовано в системах цифровой обработки различного рода сигналов.

Цель изобретения - расширение Функциональных возможностей за счет вы- числения двумерного дискретного преобразования Фурье.

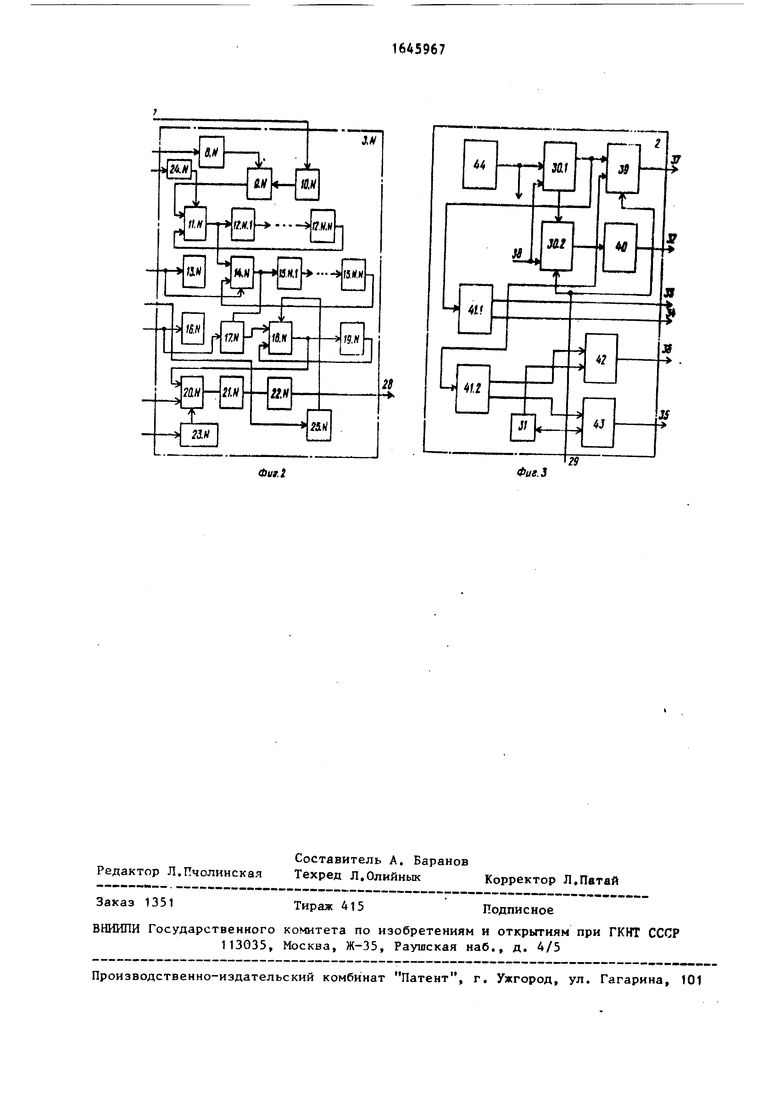

На фиг. 1 и 2 приведена структурная схема Устройства для вычисления на фиг. 3 - структурная схема блока управления устройством для вычисления двумерного ДПФ.

Устройство содержит информационный вход 1, блок 2 управления, К вычислительных модулей 3.1-3.N (N - размер преобразования), каждый из которых содержит вход 4 коэффициента, инЛорма ционный вход 5, тактовые входы 6 и 7, буферный регистр 8, умножитель 9, блок 10 постоянной памяти коэффициен

тов, сумматор 11, группу регистров

12, триггер 13, коммутатор 14, группу регистров 15, регистр 16 коэффициентов, умножитель 17, сумматор 18, регистр 19, коммутатор 20, регистры . 21 и 22, триггеры 23-25, тактовый вход 26, адресный вход 27 и информационный выход 28„

Блок 2 управления (фиг. 3) содержит управляющий вход 29, счетчики 30. и 30,2, элемент НЕ 31, выходы 32-37, установочный вход 38, коммутатор 39, узел 40 постоянной памяти, дешифраторы 41„1 и 41.2, элемент И 42, элемент ИЛИ 43 и генератор 44 импульсов.

Рассмотрим работу устройства в режиме вычисления двумерного ДПФ.

Для определенности полагаем , допускаем, что коммутаторы 39, 14.1 и 20.1 при О на управляющем входе 5 передают информацию со второго своего выхода, а сумматоры 11.1 и 18.1 при О на управляющем входе производят

матор 11, группа регистров 12, триггер 13, коммутатор 14, группа регистров 15, регистр коэффициентов 16, умножитель 17, сумматор 18, регистр 19, коммутатор 20, регистры 21, 22 и триггеры 23, 24, 25. 3 ил.

5

0

5

0

35

40

50

5

сложение содержимого на первом входе с нулем и при 1 на управляющем входе производят сложение содержимого первого и второго входов„

Входные отсчеты непрерывным потоком поступают на вход 1:

А(11) А(12) А(21) А(22)

1-й такт. Операнд А(11) заносится в регистр 801„ На выходе блока 10.1 имеется значение W(0), на выходе умножителя 9с1 - значение A(11)-W(0), которое передается на выход сумматора 11„1, поскольку на управляющем входе у него присутствует

2-й такт. Значение А(12) заносится в регистр 8.1, на выходе блока 10„1 имеется значение W(0), на выходе умножителя 9.1 и сумматора 11.1 - значение A(12)-W(0), в регистре

3-й такт. Значение А(21) заносится в регистр 8.1, значение А(12) - в регистр 8.2, на выходе блока 10.1 - имеется значение W(0), на выходе блока 10C2 - W(0), на выходе триггера 24„1 - 1, которая разрешает суммировать сумматору 11„1 по обоим входам, на выходе сумматора 11.1 имеется значение У(11)А(11)+А(21), W(0), на выходе сумматора 11„2 - A(12)«W(0), в регистре 12.1„1 - A(12).W(0), в регистре

ппскопьку нл его управляющем {;хопе присутствует О, на выходе 33 - 1

4-й такт. Значение А(22) заносится в регистр 8,1, а значение А(21) - в регистр R.2, на выходе блока 0.| имеется значение W(0), на выходе блока 10.2 - W(1), на выходе триггера 24.2 - 1, которая разрешает суммировать сумматору 11.2 по обоим входам, на выходе триггера 24.1 - 1, на выходе сумматора 11.1 - y(12)A(l2)+A(22)-W(0), на выходе сумматора 1К2 - У(2 1)А( 1 1) W(P) + +A(21)-W(1), в регистре 12,1.2 - A(22).W(0), в регистре 12.2.1 - A(12)«W(0), в регистре 12,2.2 - A(11)«W(0), на выходе 35 - 1, которая разрешает коммутатору 14.1 передавать информацию с первого входа, на выходе коммутатора 14,1 значение У(12), на выходе 32 значение V(0), на выходе умножителя 17.1 - У(12)Х XW(0), на выходе 34 - О, на выходе триггера 25.1 - 1, которая разрешает сумматору суммировать по обоим входам, в регистре 19.1 - У(11 W(0), на выходе сумматора 18.1 - F(0,(11)+y(l2) W(0), на выходе триггера 23.1 - 1, которая разрешает коммутатору 2001 передавать ин- сЬормацию с первого входа, на выходе коммутатора 20.1 - значение F(0,1), на выходе триггера 13П - 1, которая разрешает коммутатору 1402 пере- павать информацию с первого входа, на выходе коммутатора 14,2 - значение У(21), в регистре 16 „ 1 - W(0) 0 на выходе умножителя 17,2 - У(21)к xW(0), на выходе сумматора 18.2 - У(21)«И(0), поскольку на его управляющем входе имеется На выходах 33 и 36 присутствует О, в регистре 15.1.1 - У( 1.1).

5-и такт. На выходе триггера 24.1 имеется О, в регистре 8.1 - значение А(11) следуклдей последовательности, поэтому в умножителе 9.1 и сумматоре 1101 происходят процессы, аналогичные 1-му такту., В регистре 8.2 имеется значение А(22), на выходе блока 10.2 - W(1), на выходе сумматора 11„2 - У(22)А(12) У(0)+А(22)х KW(0), на выходе 35 - О, на выходе 32 - W(0), на выходе умножителя 17.1 - ydl)«W(0), в регистре 15.1.1 У(12), в регистре 15.1.2 - У(11), на выходе триггера 21 „1 - F(0,1), в регистре 12„2.2 - А(12)-W(0)s на вы

10

459676

V H1P . ОМ м у т ЧТО Г Я 1/Ё. (27, в регистра 15.2.1 - У(2 О, на выходе .f- гистра 16.1 - WfO), на умно-/ 5 жителя 17.2 - У(2)«У(0), нл выходе триггера .2 - 1, на выходе сумматора U 2 - Г(0,2)-У(21)+У(22)« W(.0), в регистре 1.2 - y(21)-W(0), на выходе триггера 23.2 - Г , на выходе коммутатора 20.2 - Г;(0,7).

Дальше работа устройства проходит но описанному алгоритму„ Коэффициенты друмг-рного преобразования Фурье выходят на выход 2Я в следующей последовательности по цепочке регистров 21,1 и 22.1: Г(0,2); F(1,2); Г(1,1).

R режиме -дномерного преобразования Лурье работа данного устройства проходит следующим образом.

На управляющий вход 29 подается

15

20

0

1, что обеспечивает переключение коммутатора 39 на первый вход, т.е. на блок 10,1 полаются адреса со чика 20.1, что обеспечивает нотакто- вую смену значений коэффициентов. Сигнал 1 с входа 29 подар ся и на упрагляющий вход счетчика Ю„2, что обеспечивает установку последнего в О, а с узла 40 на выход 32 идут только нулевые коэффициенты. Сигнал 1 на входе 29 также обеспечивает постоянство О на выходе 36 и постоянство 1 на выходе 35. что за5 ставляет сумматор 11„1 передавать содержимое первого входа на выход, а коммутатор 14.1 - информацию постоянно с первого входа. Все остальные блоки устройства работают аналогич0 но, как при вычислении коэффициентов двумерного ДГФ.

Формула изобретения

Устройство для вычисления дискрет- ного преобразования Лурье, содержащее N-1 (N - размер преобразования) вычислительных модулей и блок управления, первый тактовый вход которого подключен к первым тактовым входам всех вычислительных модулей, каждый из которых содержит первый умножитель, первый сумматор и первый, второй и третий, регистры, тактовые входы которых подключены к первому тактовому входу вычислительного модуля, отличающееся тем, что, с целью расширения Функциональных возможностей за счет вычисления двумерного пре0

5

образования Фурье, в него введен N-й вычислительный модуль, причем первый и второй информационные, первый, второй, третий и четвертый тактовые вых ды и выход коэффициента i-го (,N-1) вычислительного модуля подключены соответственно к первому и второму иформационным, второму, третьему и четвертому и пятому тактовым входам и входу коэффициента (i-H)-ro вычислительного модуля, второй, третий, четвертый и пятый тактовые выходы, адресный выход и выход коэффициента блока управления подключены соответ- ственно к второму, третьему, четвертому и пятому тактовым входам, адресному входу и входу коэффициента первого вычислительного модуля, первый информационный вход которого яв- ляется информационным входом устройства , информационным выходом которого является второй информационный выход N-го вычислительного модуля, причем в каждый вычислительный модуль введены буферным регистр, бло постоянной памяти коэффициентов, две группы из N последовательно соединенных регистров,четыре триггера, второй сумматор, второй умножитель, два коммутатора, регистр коэффициентов, выход которого является выходом коэффициента вычислительного модуля, выход первого умножителя подключен к первому информационному входу пер- вого сумматора, выход которого подключен к первому информационному входу первого коммутатора и информационному входу первого регистра, выход которого подключен к второму информационному входу первого сумматора, выход буферного регистра является первым информационным выходом вычислительного модуля и подключен к первому входу второго умножителя, выход которого подключен к первому информационному входу второго сумматора , выход которого подключен к информационному входу первого регистра первой группы и первому информационному входу второго коммутатора, выход которого подключен к информационному входу первого регистра второй

группы, первому входу первого умножителя, второй вход которого соедине с информационным входом регистра коэффициента и является входом коэффициента вычислительного модуля, первым информационным и вторым тактовыми входами которого являются соответственно информационный вход буферного регистра и тактовый вход первого триггера, выход которого подключен к входу синхронизации первого сумматора и является первым тактовым выходом вычислительного модуля, вторым информационным выходом которого является выход второго регистра, информационный вход которого подключен к выходу третьего регистра, информационный вход которого подключен к выходу первого коммутатора, второй информационный вход которого является вторым информационным входом вычислительного модуля, третьим тактовым входом которого являются соединенные между собой управляющий вход второго коммутатора и тактовый вход второго триггера, выход которого является вторым тактовым выходом вычислительного модуля, четвертым тактовым входом которого является тактовый вход третьего триггера, выход которого подключен к входу синхронизации второго сумматора и является третьим тактовым выходом вычислительного модуля, пятым тактовым входом которого является тактовый вход четвертого триггера, выход которого подключен к управляющему входу первого коммутатора и является четвертым тактовым выходом вычислительного модуля, адресным входом которого является адресный вход блока постоянной памяти коэффициентов, выход которого подключен к второму входу второго умножителя, выходы К-х регистров первой и второй групп подключены к вторым информационным входам соответственно второго сумматора и второго коммутатора, тактовые входы буферного регистра, регистра коэффициентов, всех регистров первой и второй групп подключены к первому тактовому входу вычислительного модуля.

8,И

-&

гг

п.н

/ш

1

ни

м

&

..lt

f

Lr

Фиг.

Составитель А. Баранов Редактор Л.Пчолннская Техред Л.Олийнык Корректор Л.Патай

Заказ 1351

Тираж 415

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

;.«

п

Фиг.З

Подписное

Авторы

Даты

1991-04-30—Публикация

1989-04-24—Подача