и с Р-входами второго счетчика импульсов, второго триггера и первого регистра, подключенного синхровходом к выходу второго элемента И, к синхровходу второго счетчика импульсов и к первому входу второго элемента ИЛИ соединенного вторым входом с вычитающим входом второго cчeтчиka импульсов, с выходом шестого элемента И и с вторым входом первого элемента ИЛИ, а вькодом - со счетным входом первого счетчика импульсов, подключенного синхровходом к выходу четвертого элемента И, причем второй счетчик импульсов подключен выходами к входам третьего элемента ИЛИ, а информационными входами - к информационным входам второго регистра, сзя эанного синхровходом с выходом треть его элемента И, а выходами - с выходом устройства, один из разрядов которого подключен к управляющему входу первого коммутатора, а другой к R-входу первого триггера, блок сравнения соединен вторым входом с Iвыходом первого регистра, а выходом - с вторым входом шестого элемен та И, а второйуправляющий вход ана-. лизатора логических условий подключен к первому входу второго элемента. И. 2. Устройство ПОП.1, отлич а ю. щ е е с я тем, что анализатор логических условий содержит мультиплексор, седьмой и восьмой элементы И и четвертый элемент ИЛИ, подключенный выходом к первому выходу анализатора логических условий, первым входом - к второму информации рнному входу анализатора логических условий, а вторьм входом - к выходу восьмого элемента И, связанного пер:вым входом с вторым управляющим входом анализатора логических условий и с вторым входом седьмого элемента И, соединенного выходом с вторым выходом анализатора логических условий, а первым входом - с вторым входом восьмого элемента И и с выходом мультиплексора, подключенного первым входом к первому управляющему входу анализатора логических условий, а 1|ервым информационным входом - к шине Логические условия устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256025A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

Г. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ, содержащее шесть элементов И, первый триггер, подключенный 6-входом к пусковому входу устройства, а выходом - к входу тактового генератора, первый коммутатор связанный первым информационным входом с шиной Код операции устройства, а выходом - с информационным входом первого счетчика импульсов, соединенного выходом с адресным входом постоянного запоминающего устройства, подключенного первыми выходами к информационным входам первого регистра, а вторыми выходами - к информационным входам второго регистра, третий регистр, подключенный выходом к первому управляющему входу анализатора логических условий, связанного первым информационным входом с шиной Логические условия устройства, а также второй триггер соединенньй С-входом с выходом первого элемента И и с синхровходом третьего регистра, а единичным выходом - с первым входом второго элемента И, отличающееся тем, что, с целью расширения области применения, в него введены три элемента ИЛИ, блок сравнения, второй и третий счетчики и второй коммутатор, подключенный первым информационным входом к первому выходу анализатора логических условий, связанного вторым выходом с младшим разрядом второго информационного входа первого коммутатора, вторым информационным входом - с третьим выходом постоянного запоминакицего устройства, соединенного первыми выходами с вторыми информационными входами первого коммутатора, четвертыми выходами - с информационными 5 входами третьего регистра, а пятьм выходом - с О входом второго триг гера, подключенного нулевым выходом к первым входам третьего элемента И и первого элемента И, соединенного вторым входом с вторыми входами второго и третьего элементов И, с первым входом шестого элемента И, с управляющим входом второго коммуСО татора и с первым выходом тактового со генератора, подключенного вторым 9) входом к первым входам пятого эле. мента И и четвертого элемента И, связанного инверсным входом с инверсными входами второго и третьего элементов И, с выходом третьего элемента ИЛИ, с вторым информационным входом второго коммутатора и с вторым входом пятого элемента И, соединенного выходом со счетным входом третьего счетчика, подключенного вы-, ходами к первым входам блока сравнения, а R-входом - к выходу первого элемента ИЛИ, связанного первым входом с выходом второго коммутатора

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении устройств контроля и управления технологическими процессами.

Цель изобретения - распшренйе области применения устройства.

Для реализации контроля и управлния объектом с учетом динамики процессов функционирования вводится специальный тип логических условий (ЛУ) - интервальные ЛУ.

Интервальным ЛУ х- называется логическое условие, которое обращается в единицу после прихода от объ екта управления единичного сигнала по i-му выходу в один из интервалов

o.sl. .7....

ПС« , где С, - интервал времени, задаваемый дпя данного ЛУ, Г, « C°tp, t - минимальныйкратньй интервал, . ; - суммарный интервал проверки ЛУ.

Для проверки интервальных логических условий задается код интервала времени (квант проверки) и количество интервалов, т.е. суммарное время

проверки. В зависимости от номера интервала времени, в течение которого пришел сигнал от объекта, осуществляется ветвление в микропрограмме и переход к соответствующей микрокоманде .

Введение и реализация с помощью специальных технических средств проверки интервальных логических условий позволяет в процессе контроля и управления объектом учитывать не только.факт формирования им соответствующего сигнала (готовности, достижения параметров требуемого значения и т.д.), но и момент его поступления

-fOT объекта в геальном масштабе времени. Кроме того, это исключает необходимость введения большого числа холостых микрокоманд, а следоJ

вательнр, обеспечивает значительное сокращение объема блока памяти,

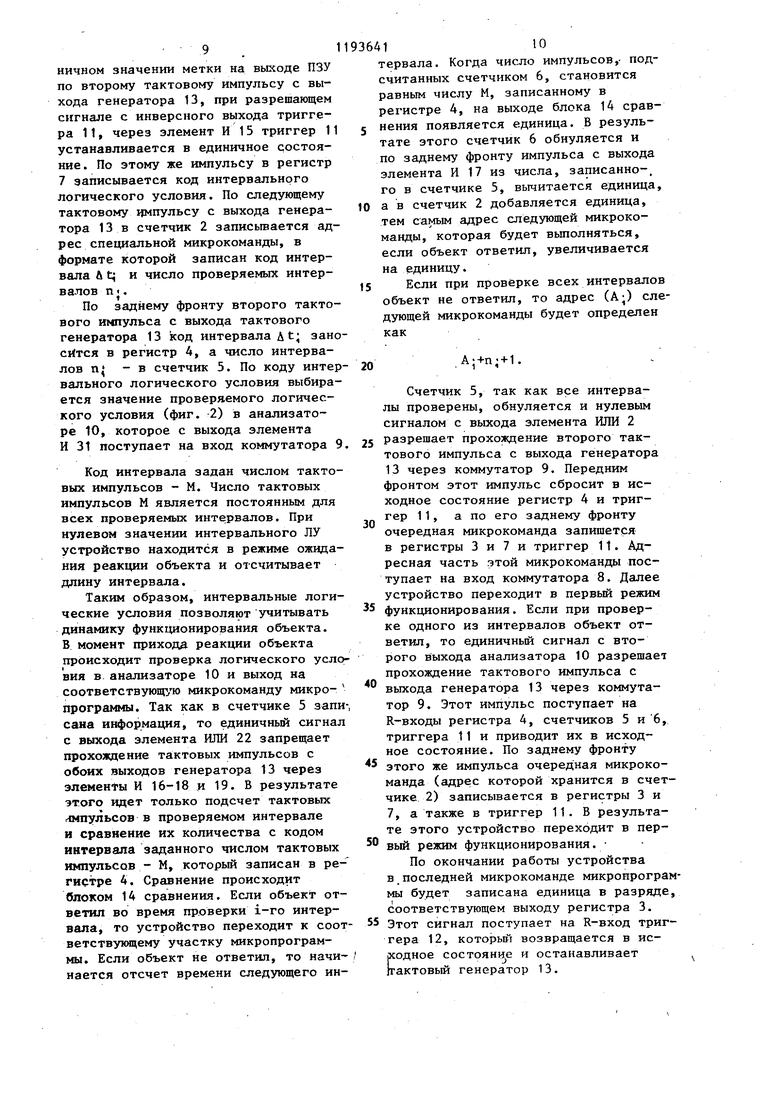

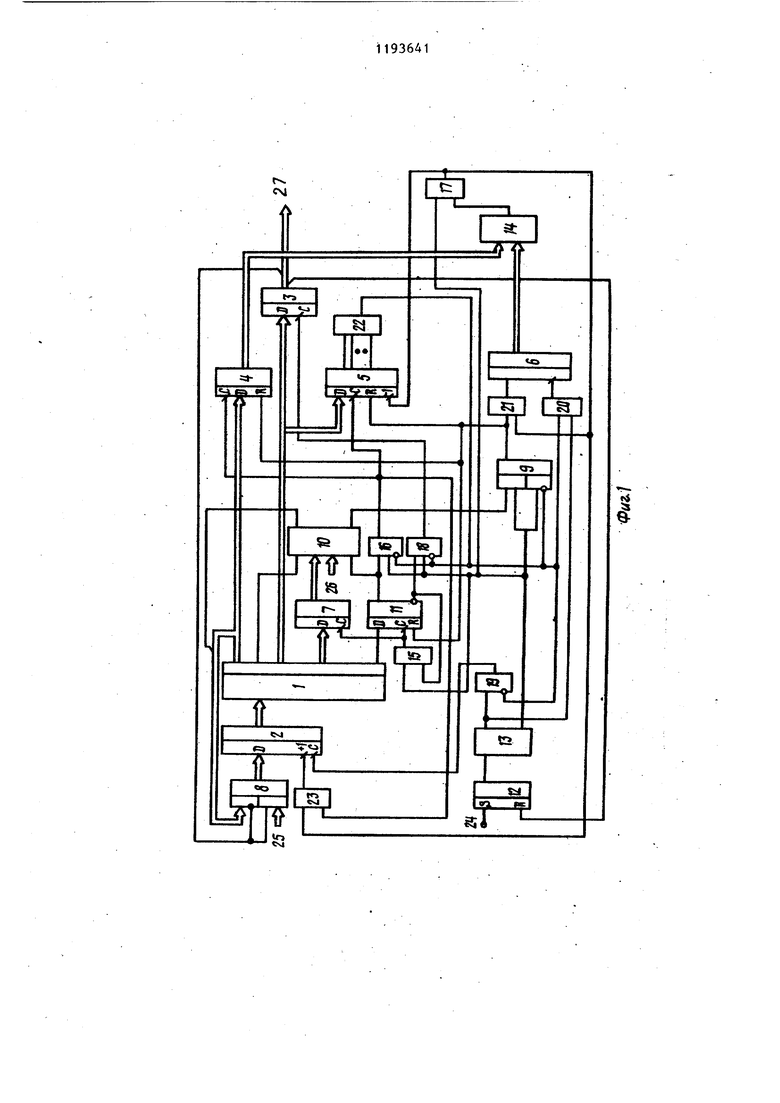

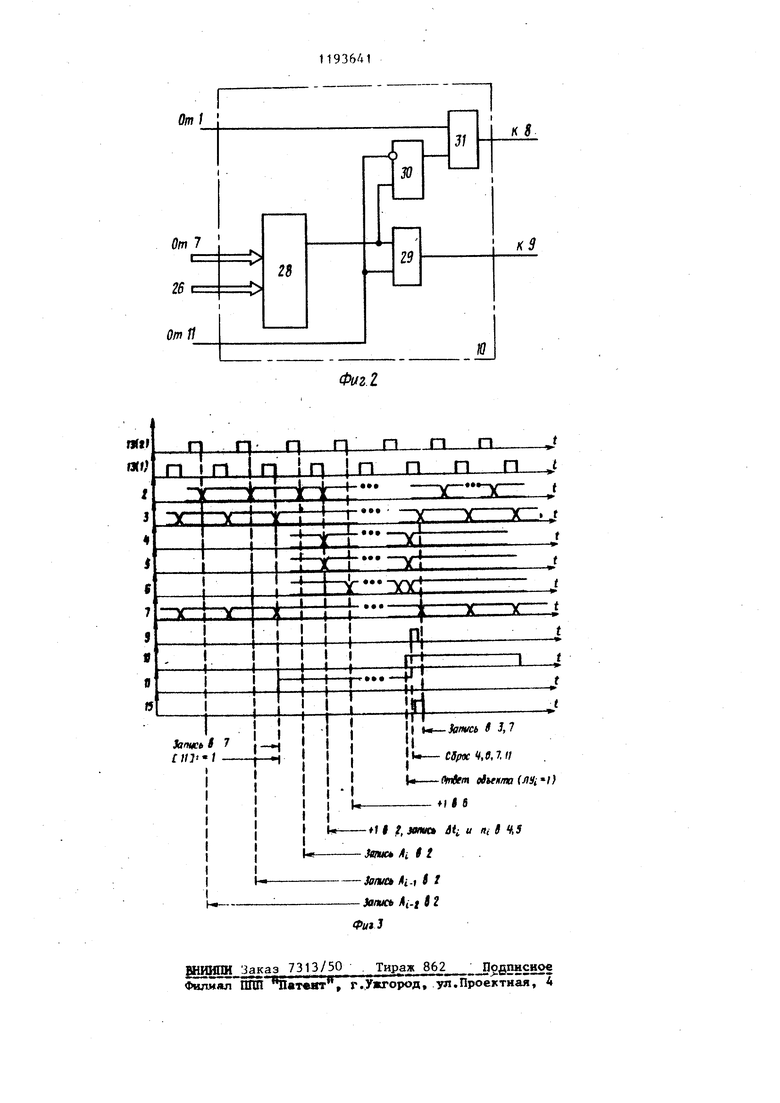

На фиг. 1 приведена функциональная .схема устройства для контроля и управления технологическими процесами; на фиг. 2 - функциональная схема анализатора логических условий; на фиг. 3 - временная диаграмма работы устройства.

Устройство для контроля и управления (фиг. 1) содержит постоянное запоминающее устройство 1, первьш счетчик 2 импульсов (счетчик адреса), второй регистр 3 (регистр микроопераций) , первый регистр 4 (ре,гистр кода интервалов), второй счетчик 5 импульсов (счетчик числа интервалов), третий счетчик 6 импульсов (счетчик интервала), третий регистр 7 (регистр логических условий) первый коммутато р 8 (коммутатор адреса), второй коммутатор 9 (коммутатор сигналов сброса), анализатор

10логических условий, второй тригге

11(триггер зшравлення), первый триггер 12 (триггер пуска), тактовый генератор 13, блок 14 сравнения, первый 15, второй 16, шестой 17, третий 18, четвертый 19, пятый 20 элементы И, первый 21, третий 22, второй 23 элементы ИЛИ пусковой 24 вход устройства, шину 25 Код операции, шину 26 Логические условия, микрооперационный выход 27 устройства.

Блок 10 анализа логических условий (фиг. 2) содержит мультиплексор 28 логических условий, седьмой 29 и восьмой 30 элементы И, четвертый элемент ИЛИ 31.

Первые управляющий и информационные входы анализатора 10 логических условий соединены с управляющим и информационным входами мультиплексора 28 соответственно, выход которого соединен с первыми входами элементов И. Второй информационный вход блока 10 анализа логических условий соединен с первым входом элемента ИЛИ 31, выход которого является выходом .модифицированного разряда адреса анализатора 10. Второй управляющий вход анализатора 10 соединен с вторыми входами элементов И 29 и 30, выходы которых соединены соот-вётственно с выходом конца ожидания анализатора 10 и вторым входом элемента ИЛИ 31.

Постоянное запоминающее устройство (ПЗУ) 1 предназначено для хранения микропрограмм, реализуемых устройством. ПЗУ 1 имеет пять выходов.

С первого выхода ПЗУ 1 считываются коды немодкфицируемой части адреса очередной микрокоманды, либо коды интервалов. ПЗУ 1 считывается младший (модифицируемый) разряд адIQ реса очередной микрокоманды. С второго выхода ПЗУ 1 считывают операционные части микрокоманд, реализуемых устройством, либо коды числа интервалов. С третьего выхода ПЗУ 1

.f .считывается младший (модифицируемый) разряд адреса очередной микрокоманды. С четвертого выхода ПЗУ I считьшаются коды проверяемых логических условий, в том числе и интер- вальных. С пятого выхода ПЗУ 1 считывается сигнал метки, которой отмечаются микрокоманды, содержащие код интервального логического условия. ПЗУ 1 представляет собой запоминающее устройство статического типа. Адрес, поступающий на вход ПЗУ, формируется счетчиком 2.

Счетчик 2 (адреса микрокоманд) предназначен .для приема, хранения и выдачи кодов адресов текущих микрокоманд и формирования адреса очередной микрокоманды при проверке иитервальных логических условий. Так как в ПЗУ 1 для каждого иитервальиого логического условия х вьщеляется

3 область памяти, число ячеек в которой равно п,- +2 (где п - число интервалов проверки интервального логи-. ческого условия), а их адреса отличаются на единицу, то.в счетчике 2

добавлением единицы к текущему адресу происходит формирование адреса очередной микрокоманды, выполняемой после проверки интервального логического условия.

5 Увеличение содержимого счетчика 2 на единицу осуществляется по задиему фронту импульса с выхода элемеита ИЛИ 23. Запись текущего адреса с выхода коммутатора 8 осуществляется

50 через D-входы счетчика 2 по заднему фронту синхроимпульса, поступившего на его С-вход с выхода элемеита И 19, который открывается, если счетчик 5 находится в исходном состоянии.

55 i Регистр 3 (микроопераций) предназначен для приема, хранения и выдачи сигналов микроопераций. Запись информации в регистр 3 осуществляется

S

по заднему фронту второго тактового импульса с выхода тактового генератра 13, поступающего на С-вход регисра 3 через элемент И 18 при исходном состоянии триггера 11 и счетчика 5.

Регистр 4 (кода интервалов) предназначен для приема, хранения и вьщчи кода интервала.

Код интервала задается числом тактовых импульсов, записанных в ПЗУ 1 при реализации специальной шкpoкoмaнды, которая считывается после выполнения микрокоманды, помеченной меткой. Запись информации в регистр происходит по заднему фронту второго тактового импульса с выхода генератора 13 при разрешающем единичном сигнале с прямого выхода триггера 11 и исходном состояни счетчика 5. Длительность всех проверяемых интервалов для одного инте вального логическогб условия одинакова .

Счетчик 5 (импульсов) предназначен для приема, хранения и выдачи числа интервалов, в течение которых проверяется выполнение интервального логического услория. Запись информации (числа интервалов) осуществляется в счетчик 5 по заднему фронту второго тактового импульса с выхода генератора 13 при разрешанщем .сигнале с прямого выхода триггера il управления. После записи ко|да числа интервалов в счетчик 15 на в№{оде элемента ИЛИ 22, входы которого подключены к прямым выходам разрядов счетчика, появляется единичный сигнал, который запрещает прохождение очередных тактовых i-мпульсов через элемент И 16 на вход синхронизации (С) счетчика 5 .

Счетчик 5 имеет вычитающий вход (-1). При поступлении на этот вход импульсов по их заднему фронту содержимое счетчика 5 уменьшается на единицу. Сброс счетчика 5 в исходное состояние осуществляется импульсами, поступающими на его R-вход с выхода коммутатора 9.

Счетчик 6 (счетчик интервала) предназначен для подсчета длины интервала проверки интервального логического условия. На его счетный вход () поступают импульсы с выхода генератора 13 через элемент

936416

И 20, который управляется выходным сигналом элемента ИЛИ 22. Сброс счетчика 6 в исходное состояние осуществляется выходным сигналом 5 элемента ИЛИ 21, через который проходят импульсы с выходов коммутатора 9, либо элемента И 17.

Регистр 7 предназначен для приема, хранения и выдачи кодов проверяемых логических условий. Код проверяемых интервальных логических условий хранится в регистре 7 до тех пор, пока не придет сигнал реакции объекта (выполнение интервального

J5 ЛУ), а если ответа от объекта нет, то до начала выполнения следующей . микрокоманды.

Коммутатор 8 предназначен для коммутации адреса следующей микрокоманды. При отсутствии микрооперации на выходе регистра 3 на первый информационный вход счетчика 2 адреса поступают разряды адреса очередной микрокоманды с выхода ПЗУ. В

25 противном случае в счетчик 2 передается код вьшолняемой операции с входа 25 устройства, который определяет адрес первой микрокоманды выполняемой микропрограммы.

Коммутатор 9 предназначен для формирования сигналов установки в исходное состояние элементов схемы регистра 4, счетчика 5, счетчика 6 и триггера 11, при поступлении второго тактового импульса с выхода генератора 13 при поступлении реакции от объекта контроля и управления (единичный сигнал с второго выхода анализатора 10), либо при окончании времени проверки интервального логического условия (единичньй сигнал с выхода элемента ИЛИ 22).

Анализатор логических условий (фиг. 2) состоит из мультиплексора 28, который по коду логического условия с выхода регистра 7 выбирает значение проверяемых логических условий, элементов И 29 и 30 и элемента ИЛИ 31. Элемент И 29 предназначен для формирования сигнала управления на коммутатор 9 при проверке интервального логического условия и ответа объекта, а элементы И 30, ИЛИ 31 - для формирования младшего модифицированного разряда адреса следующей микрокоманды при реализации микрокоманд ветвления и выполняемой микропрограмме. 7 Триггер 11 предназначен для фиксации факта появления метки в форматемикрокоманды, т.е. микрокоманды, задающей проверку интервал ного ЛУ. Триггер 11 изменяет свое состояние по заднему фронту второго тактового импульса, формируемого генератором 13 при наличии в формат микрокоманды з равляющей метки. Триггер 12 предназначен для управления запуском тактового генератора 13. Его включение происходит по сигналу Пуск, поступаннцему на вход 24 устройства, а выключение по сигналу Конец работы с выхода регистра 3. Блок 14 сравнения предназначен для сравнения информации с выхода регистра 4 (код интервала задается числом тактовых импульсов) и информации с выхода счетчика 6 о числе тактовых импульсов, поступивпшх за проверяемый интерв ал. При совпадении этих кодов на выходе блока 14 сравнения появляетс единичный сигнал. Устройство работает следукяцим образом. В исходном состоянии все элемент схемы находятся в нулевом состояний а в разряде регистра 3, соответству щем микрооперации Конец команды, записана 1. Цепи приведения схемы в исходное состояние условно не показаны. Устройство функционирует в двух основных режимах. Первый режим. По сигналу Пуск, поступаницему на вход 24 устройства, триггер 12 устанавливается в единич ное состояние и включает тактовый генератор 13. . По первому тактовому импульсу с выхода генератора 13 в счетчик 2 с входа 25 через коммутатор 8 записывается код реализуемой операции, который определяет адрес первой микрокоманды, соответствзпощей микро программы. С выходов ПЗУ 1 считывается микрокоманда, адресная часть которой поступает на коммутатор 8. По второму тактовому импульсу с выхода генератора 13 операционная часть микрокоманды-(код микрооперацнй) поступает в регистр 3 и вьщается на выход 27 устройства. По очередному тактовому импульсу при реализации линейных участков 418 микропрограмм работа устройства повторяется . Если в микропрограмме необходимо реализовать ветвление по значению логического условия, то код этого условия записывается в регистр 7. По этому коду мультиплексор 28 анализатора 10 выбирает его значение, которое через элементы И 30 и ИЛИ 31 передается на первый выход анализатора 10 и в качестве младшего модифицированного разряда адреса очередной микрокоманды постутхает на вход коммутатора 8. Таким образом, если .значение проверяемого логического условия равно нулю, то очередная микрокоманда считывается по четному адресу, а при единичном значении логического условия - по нечетному. Далее устройство работает аналогично. Второй режим. Рассмотрим функционирование устройства в случае реализации микрокоманд с интервальными логическими условиями, обеспечиваю1ЦИМИ многонаправленное ветвление в микропрограмме. ,При проверке таких условий, если оно равно нулю, устройство находится в режиме ожцдания. Вторым параметром лвляется время. В зависимости от времени реакции объекта на такую микрокоманду реализуется -ветвление в микропрограмме. Далее такие условия будем называть интервальными логическими условиями. Микрокоманды, в формате которых записан код интервального логического условия, помечаются специальной меткой. Для этого введен один дополнительный разряд в формат микрокоманды. Для каждого логического условия задаются длительность и число п, интервалов времени, в течение которых оно может быть реализовано. Выделяется область памяти, число ячеек памяти в которой равно . Адреса этих микрокоманд отличаются на единицу. За микрокомандой, отмеченной меткой, следует специальная м:1крокоманда, в формате которой задается код интервала Аt (числом тактовых импульсов в интервале) и п - число интервалов. В данном режиме устройство функционирует следующим образом. После считывания микрокоманды которая содержит метку, очередной считывается специальная микрокоманда. При единичном значении метки на вькоде ПЗУ по второму тактовому импульсу с выхода генератора 13, при разрешающем сигнале с инверсного выхода триггера 11, через элемент И 15 триггер 11 устанавливается в единичное цостояние. По этому же импульсу в регистр

7записывается код интервального логического условия. По следующему тактовому импульсу с выхода генератора 13 в счетчик 2 записьтается адрес специальной микрокоманды, в формате которой записан код интервала Л ti и число проверяемых интервалов П J ,

По заднему фронту второго тактового импульса с выхода тактового генератора 13 код интервала At; заносится в регистр 4, а число интервалов п{ - в счетчик 5. По коду интервального логического условия выбирается значение проверяемого логического условия (фиг. 2) в анализаторе 10, которое с выхода элемента И 31 поступает на вход коммутатора 9

Код интервала задан числом тактовых импульсов - М. Число тактовых импульсов М является постоянным для всех проверяемых интервалов. При нулевом значении интервального ЛУ устройство находится в режиме ожидания реакции объекта и отсчитывает длину интервала.

Таким образом, интервальные логические условия позволяют учитывать динамику функционирования объекта.

8момент прихода реакции объекта происходит проверка логического услрвия в анализаторе 10 и выход на соответствующз.ю микрокоманду микропрограммы. Так как в счетчике 5 запи сана информация, то единичный сигнал с выхода элемента ИЛИ 22 запрещает прохождение тактовых импульсов с обоих выходов генератора 13 через элементы И 16-18 л 19. В результате этого идет только подсчет тактовых готульсов в проверяемом интервале

и сравнение их количества с кодом интервала заданного числом тактовых импульсов - М, который записан в регистре 4. Сравнение происходит блоком 14 сравнения. Если объект ответил во время проверки i-ro интервала, то устройство переходит к соответствукнцему участку микропрограммы. Если объект не ответил, то начинается отсчет времени следующего интервала. Когда число импульсов,- подсчитанных счетчиком 6, становится равным числу М, записанному в регистре 4, на выходе блока 14 сравнения появляется единица. В результате этого счетчик 6 обнуляется и по заднему фронту импульса с выхода элемента И 17 из числа, записанно-. го в счетчике 5, вычитается единица,

а в счетчик 2 добавляется единица, тем самым адрес следующей микрокоманды, которая будет выполняться, если объект ответил, увеличивается на единицу.

Если при проверке всех интервалов объект не ответил, то адрес (А;) следующей микрокоманды будет определен как

А;+П;+1.

Счетчик 5, так как все интервалы проверены, обнуляется и нулевым сигналом с выхода элемента ИЛИ 2

5 разрешает прохождение второго тактового импульса с выхода генератора 13 через коммутатор 9. Передним фронтом этот импульс сбросит в исходное состояние регистр 4 и триггер 11, а по его заднему фронту очередная микрокоманда запишется в регистры 3 и 7 и триггер 1t. Адресная часть этой микрокоманды поступает на вход коммутатора 8. Далее устройство переходит в первый режим

5 функционирования. Если при проверке одного из интервалов объект ответил, то единичный сигнал с второго выхода анализатора 10 разрешает прохождение тактового импульса с выхода генератора 13 через коммутатор 9. Этот импульс поступает на R-входы регистра 4, счетчиков 5 и 6, триггера 11 и приводит их в исходное состояние. По заднему фронту

5 этого же импульса очередная микрокоманда (адрес которой хранится в счетчике 2) записывается в регистры 3 и 7, а также в триггер 11. В результате этого устройство переходит в первый режим функционирования.

По окончании работы устройства в последней микрокоманде микропрограммы будет записана единица в разряде, соответствующем выходу регистра 3.

5 Этот сигнал поступает на R-вход триггера 12, который возвращается в исходное состояние и останавливает {тактовый генератор 13.

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955057A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-11—Подача