О«-

00

4 СЛ

ел

Изобретение относится к электросвязи и может быть использовано для оценки готовности и качества передачи при эксплуатации и испытанияк много- канальных цифровых систем передачи с временным уплотнением.

Цель изобретения - расширение функциональных возможностей путем определения параметров потоков оши- бок одновременно для нескольких низкоскоростных цифровых сигналов.

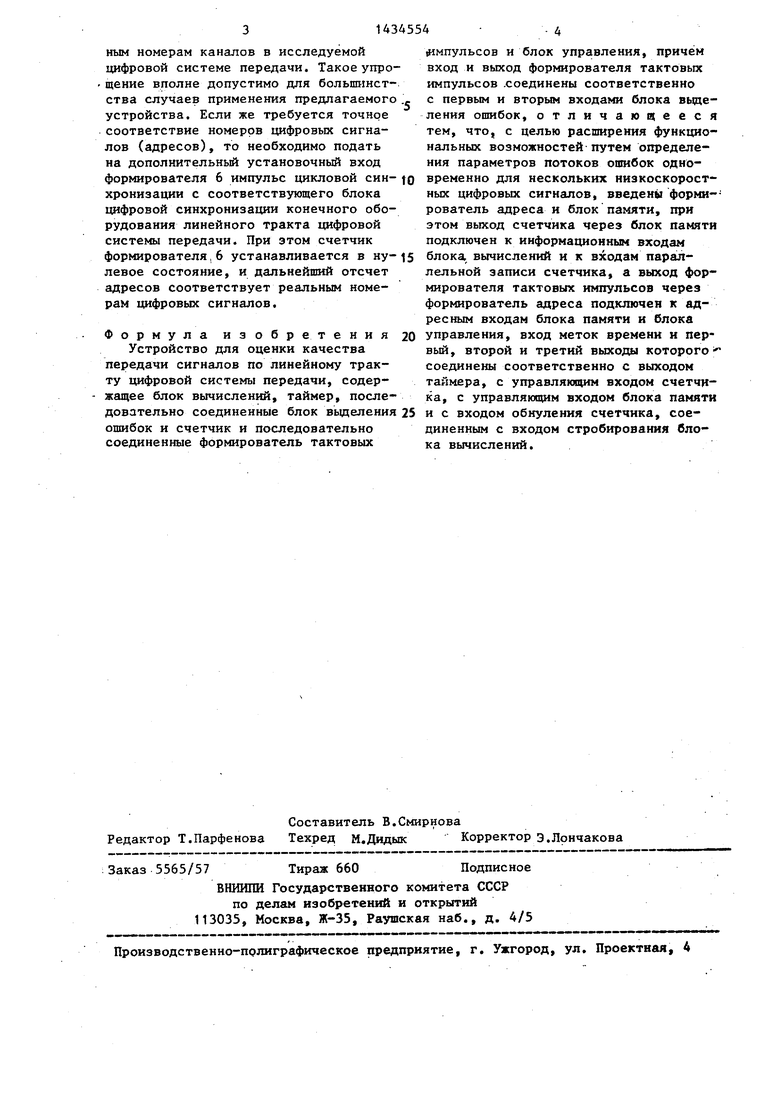

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство для оценки качества передачи сигналов по линейному траК ту цифровой системы передачи содержит блок 1 выделения ошибок счетчик 2, блок 3 памяти, блок 4 управления, формирователь 5 тактовых и myльcoв формирователь 6 адреса, таймер 7 и блок 8 вычислений.

Устройство работает следующим об разом.

Исследуемый сигнал образуется в результате прохождения высокоскоростного цифрового сигнала, сгруппированного из нескольких низкоскоростных сигналов (1), (2), (3)j .„.$ через линейный тракт, в котором некоторые из его символов О, 1 принимают ошибочные значения, превращающие . исходный идеальньй сигнал в сигнал с ошибками,, параметры которого (коэффициент ошибок и т.д.) подлежат измерению Этот сигнал с ошибками подается одновременно на входы блока 1 выделения ошибок и формирователя 5 тактовых импульсов, на выходах кото- рых. образуются импульсы ошибок и тактовые импульсы соответственно.

Измерение количества ошибок в цифровых сигналах (1),(2),(3),... производится следующим образом. В бло- ке 3 памяти для каждого низкоскоростного цифрового сигнала вьщелено требуемое количество ячеек памяти, в которых в течение одного цикла сохраняется измеренное значение суммы ошибок данного сигнала. В каждом такте последовательно выполняются следующие операции: перенесение значения суммы ошибок данного цифрового сигнала (с данным номером) в счетчик 2 измерения ошибок (режим считывания из блока 3 памяти и параллельной записи в счетчик 2)| прибавление единицы к записанному (перенесенному) значению при наличш 1 ошибки в цифровом сигнале; запись полученной суммы в соответствующие ячейки блока 3,па- мяти.

.Записанное значение хранится до следующего цикла, а в следующем такте выполняются аналогичные операции для цифрового сигнала со следующим номером, задаваемым формирователем 6. Накопление информации об ошибках в каждом цифровом сигнале (1),(2), (3),... производится до конца периода измерения. .Окончание периода измерения определяется выдачей импульса с таймера 7. При поступлении этого импульса по сигналу блока 4 начинается считывание накопленных значений сумм ошибок из блока 3 памяти в 8. Это производится в первой половине каждого такта по стробирующему сигналу. Этим же сигналом осуществляется установка в нулевое состояние счетчика 2.. Во второй половине каждого такта производится прибавление к нулевому значению единицы (при наличии ошибки в цифровом сигнале) и запись полученного значения (нулевого или единичного) в соответствующей ячейке блока 3 памяти. Тем самым поочередно осуществляется подготовка к новому периоду измерения в ячейках памяти для каждого цифрового сигнала Эта процедура продолжается до тех пор пока содержимое всех ячеек памяти не .будет перенесено в блок 8, и все они не будут подготовлены к следующе му периоду измерений. При поступлении очередного тактового импульса устройство продолжает работу в режиме измерения (накопления) ошибок.

В блоке 8, функции которого может выполнять, например, микроЭВМ, в соответствии с заданньм алгоритмом осуществляется обработвга результатов измерений с целью определения параметров цифровых сигналов и цифровых трактов: коэффициента готовности, длительностей перерывов связи и т.д. Результаты обработки регистрируются в форме таблиц, графиков на соответствующих приборах, сопряженных с мик- роЭВЫ.

В предлагаемом устройстве при проведении измерений подразумевается, что все каналы (цифровые сигналы) одинаковые, поэтому присваиваемьш им номера (1),(2),(3),„.. условны и в общем случае не соответствуют реальным номерам каналов в исследуемой цифровой системе передачи. Такое упрощение вполне допустимо для болыпинст- ства случаев применения предлагаемого устройства. Если же требуется точное соответствие номеров цифровых сигналов (адресов), то необходимо подать на дополнительньй установочный вход формирователя 6 импульс цикловой син- хронизации с соответствующего блока цифровой синхронизации конечного оборудования линейного тракта цифровой системы передачи. При этом счетчик формирователя,6 устанавливается в нулевое состояние, и дальнейший отсчет адресов соответствует реальным номерам цифровых сигналов.

Формула изобретения

Устройство для оценки качества передачи сигналов по линейному тракту цифровой системы передачи, содержащее блок вычислений, таймер, последовательно соединенные блок вьщеления ошибок и счетчик и последовательно соединенные формирователь тактовых

«импульсов и блок управления, причём вход и выход формирователя тактовых импульсов .соединены соответственно с первым и вторым входами блока вьщеления ошибок, отличающееся тем, что, с целью расширения функциональных возможностей путем определения параметров потоков ошибок одновременно для нескольких низкоскоростных цифровых сигналов, введены формирователь адреса и блок памяти, при этом выход счетчика через блок памяти подключен к информационным входам блока вычислений и к входам параллельной записи счетчика, а выход формирователя тактовых импульсов через формирователь адреса подключен к адресным входам блока памяти и блока управления, вход меток времени и первый, второй и третий выходы которого соединены соответственно с выходом таймера, с управляющим входом счетчика, с управляющим входом блока памяти и с входом обнуления счетчика, соединенным с входом стробирования блока вычислений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оценки качества передачи дискретных сигналов | 1988 |

|

SU1525923A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Устройство избирательного вызова и передачи кодограмм | 1983 |

|

SU1136326A1 |

| Способ измерения ошибок в цифровом канале передачи данных и устройство для его осуществления | 1987 |

|

SU1501294A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1984 |

|

SU1223373A2 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Устройство кодовой синхронизации | 1985 |

|

SU1328941A1 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

| Устройство для определения времени фибринолизиса | 1985 |

|

SU1323566A1 |

Изобретение относится к электросвязи и м.б. использовано для оценки готовности и качества передачи при эксплуатации и испытаниях многока- нальнъпс цифровых систем передачи с временным уплотнением. Цель изобретения - расширение функциональных возможностей путем определения параметров потоков ошибок одновременно для нескольких низкоскоростных цифровых сигналов (ЦС); Устр-во содержит блок 1 вьщеления ошибок, счетчик 2, блок 4 управления, формирователь (Ф) 5 тактовых импульсов, таймер 7 и блок 8 вычислений. В устр-во введены Ф 6 адреса, блок 3 памяти (ВП). В БП 3 для каждого низкоскоростного ЦС вьщелено требуемое кол-во ячеек памяти, в которых в течение одного цикла сохраняется измеренное значение суммы ошибок данного сигнала. В каждом такте последовательно выполняются след, операции: перенесение значения суммы ошибок данного ЦС в счетчик 2 измерения ошибок, прибавление единицы к записанному значению при наличии ошибки в ЦС, запись полученной суммы в соответствующие ячейки БП 3. Записанное значение хранится до следующего цикла, а в следующем такте вьшолняются аналогичные операции для ЦС со следующим номером, задаваемым Ф 6. Накопление информации об ошибках в каждом ЦС производится до конца периода измерения. 1 ил. (Л

| Устройство для контроля дуплексного канала связи | 1982 |

|

SU1061280A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР № 1380585, кл, Н 04 J 3/14, 1986. | |||

Авторы

Даты

1988-10-30—Публикация

1986-07-23—Подача