Изобретение относится к злектро- С вязи н может быть использовано для исследования статистических характеристик потоков ошибок в цифровых системах передачи.

Цель изобретения - расширение функциональных возможностей путем обеспечения измерения распределения длшн пакетов ошибок и пауз между ними .

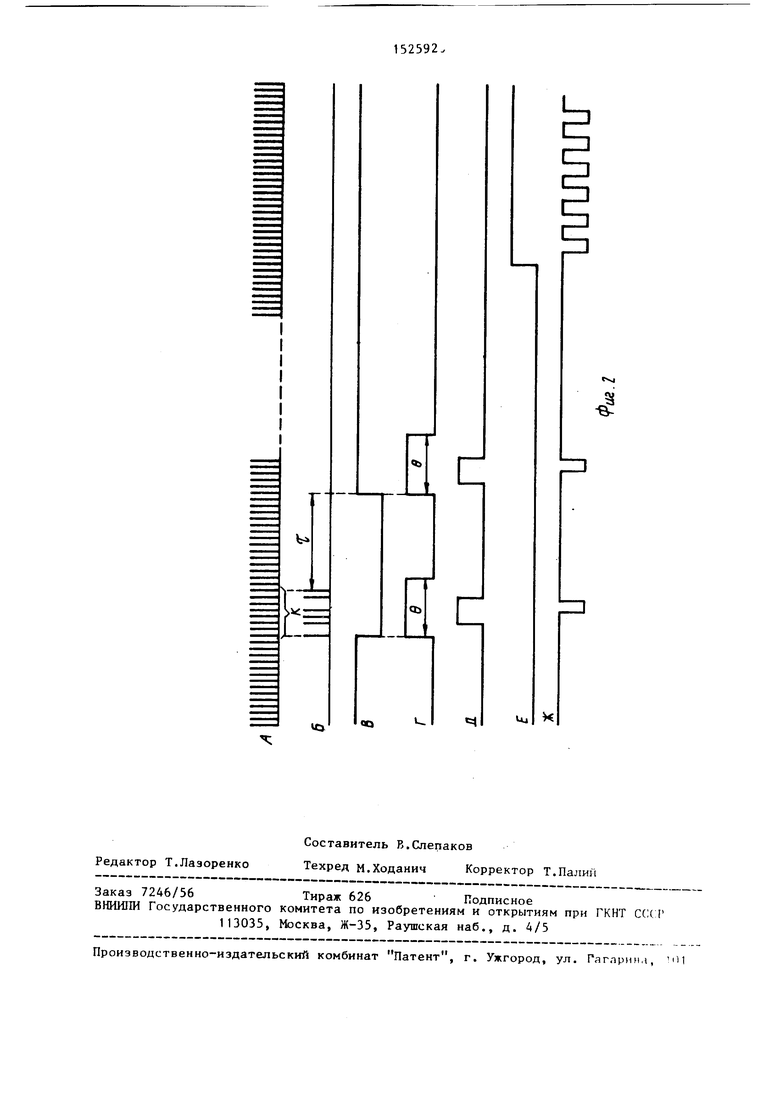

На фиг.1 приведена структурная электрическая схема предлагаемого устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство для оЦенки качества передачи сигналов содержит блок 1 выде цения ошибок, формирователь 2 тактовых импульсов, счетчик 3, блок 4 памяти, блок 5 вычислений, таймер 6, блок 7 управления, измеритель 8 длин пакета, регистр 9, измеритель 10 паузы, триггер 11, элемент 12 задержки, фop пфoвaтeль 13 коротких импульсов, элемент 1-ШИ 14 и формирователь 15 адреса, причем измеритель 8 длины пакета содержит делитель 16 частоты, мультиплексор 17 и счетчик 18, а измеритель 10 пауз содержит делитель 19 частоты, мультиплексор 20 и счетчик 21.

Устройство работает следуюидим образом.

Исследуемый сигнал поступает ил.новременно на входы формирователя 2 тактовых импульсов и блока 1 выделения ошибок, на выходах которых образуются соответственно тактовые и тульсы (фиг,2А) и импульсы ошибок (фиг.2Б). Состояние исследуемого сигнала (Ошибки или Пауза ) фиксирует триггер 11, для чего на один его вход поступают импульсы ошибок, переводящие триггер 11 в нулевое состояние, а на другой вход поступает ш-шульс, отмечающий момент времени, отстоящий от последней ошлбки пакета на защитный интервал о (фиг.2В) .

Длительность пакета ошибок определяется в измерителе 8. На его вход поступают тактовые импульсы, подсчет которых в делителе 16 возможен только при нулевом состоянии триггера 1 1 (режим Ошибки), В исходном состоянии на выходах счетчика 18 установлены уровни 000. При этом включен певый мультиплексор 17. При первой ошибке с первого выхода делителя 16 че0

5

0

5

0

5

0

5

0

5

рез мультиплексор 17 на вход счетчика 18 поступает импульс, который переводит его в состояние 001 и, следовательно, переключает мультиплексор 17 на второй вход. По мере поступления тактовых импульсов на выходах делителя 16 поочередно появляются импульсы (или потенциалы), отмечающие прохождение второго, четвертого, восьмого и т.д. тактового импульса. Каждый импульс (потенциал) переводит счетчик 18 в следующее состояние и одновременно открывает следующий вход мультиплексора 17. Таким образом, на выходе счетчика 18 формируется код, отображающий в логарифмическом масштабе (по основанию 2) количество прошедших тактовых импульсов.

Предложенная реализация измерителя 8 обеспечивает сжатие информации о длительности пакетов с целью упрощения аппаратной реализации устройства и программного обеспечения. Хотя при этом увеличивается погрешность измерения пакетов большой ;и1ительности, зато обеспечивается эффективное использование ячеек блока 4 памяти и облегчается последующая обработка результатов измерений. При других вариантах построе ия измерителя 8 зависимость его выходного кода от количества тактовых импульсов, соот- ветствующих длительности пакета, может быть другая.

Регистр 9 фиксирует значение выходного кода измерителя 8 в каждый момент прохождения ошибки, тем самыл обеспечивается текущая регистрация длительности пакета независимо от наличия правильно принятых символов внутри пакета ошибок. По окончании пакета ошибок информация о его длительности сохраняется в регистре 9 до поступления следующего пакета.

Подсчет длительности паузы осуществляется в измерителе 10, который построен и функционирует аналогично измерителю 8. Однако импульсы на выходах делителя 19 отмечают прохождение, например, сотого, тысячного и т.д. тактового импульса, что обеспечивает еще более плотное представление информации о длительности паузы.

Импульсы ошибок поступают на управляющий вход измерителя 10 и устанавливают делитель 19 в нулевое состояние. После каждой ошибки измери

тель 10 начинает подсчет тактов. Если ошибок больше нет, то наступление состояния Пауза отмечается появлением потенциала (или импульса) на управляющем выходе измерителя 10 через защитный интервал после ошибки. Затем измеритель 10 продолжает от счет тактовых импульсов, и на его вькоде присутствует код, соответствующий длительности паузы в логарифмическом масштабе (по основанию 10).

При-поступлении следующей ошибки информация в счетчике 21 стирается не сразу, а через интервал времени 0, задаваемый элементом 12 задержки, после обнуления триггера 11. Это не- обхо;1имо для записи информации об измеренной длительности паузы. Сброс счетчика 21 осуществляет короткий импульс с формирователя 13.

В течение каждого цикла измерения (например, 1 с) информация об измеренных длительностях пакетов ошибок и пауз накапливается в блоке 4 памяти, для чего в нем предусмотрено требуемое количество ячеек памяти для хранения сумм пакетов и пауз всех диапазонов длительности, причем коды длительностей пакетов (с выхода регистра 9) и коды длительностей пауз (с выхода измерителя 10) являются адресами соответствующих ячеек памяти.

Через формирователь 15 адреса код длительности пакета (или паузы) пода стся на блок 4 памяти, при этом на его выходы поступает значение суммы пакетов (или пауз) дачной длительности, записанной ранее. По мере изменения кода длительности пакета в регистре 9 (или паузы в счетчике 21) соответственно изменяется и адресный код. Таким образом, к моменту окончания каждого состояния на выходах блока 4 памяти установлено записанное ранее значение суммы пакетов (или пауз) той же длительнос

ти, что и измеренная в данный момент. При изменении состояния исследуемого сигнала зто значение суммы на некоторое время сохраняется на выходах блока 4 памяти, так как формирователь 15 переключается сигналом с выхода элемента 12 задержки через элемент ИЛИ 14.

При каждом изменении состояния контролируемого сигнала за время 0 последовательно выполняются следую0

0

5

1дие операции: перенесение значения записанной ранее суммы пакетов (или пауз) данной длительности из блока 4 памяти в счетчик 3 (режим параллельной записи в счетчик 3 задается импульсами фиг.2Г); прибавление единицы к записанному значению (режим Счет осуществляют импульсы фиг.2Л); запись полученной суммы в те же ячейки блока 4 памяти (под упрарле.нием импульсов фиг.2Ж).

Окончание цикла измерений (1 с или др.) определяется вьщачей им- 5 пульса с таймера 6. К этому моменту tio ячейкам блока 4 памяти распределена информация о зафиксированных пакетах и паузах. Эта информация переносится для последующей обработки в блок 5 вычислений. Одновременно проводит ся очистка ячеек блока 4 памяти. После поступления с таймера 6 управляюп ;его импульса блок 5 вычислений начинает вырабатывать следующие сигналы: управляющий сигнал (фиг.2К), переключающий формирователь 15 и устанавливающий в нулевое состояние счетчик 3; коды адресов запрашиваемых ячеек памяти, которые поступают на адресные входы блока 4 памяти через формирователь 15 адреса; сит-нал стирания в виде последовательности импульсов, каждьш из которых появляется перед выдачей следуюшег о кода адреса с блока 5 вычислений.

Сигнал фиг.2Е поступает на первый управляющий вход бормирователя 15 непосредственно, а на второй - через элемент 1ШИ 14. При этом обеспечивается прохождение через формирователь 15 адресных кодов с блока 5 вычислоний.

По каждому адресноьг колу блок 4 памяти выдает на информационные входы блока 5 вычислений соответствующее значение суммы пакетов (или пауз). После принятия этой инАормации код адреса еще некоторое время не меняется, при этом с блока 5 вычислений на второй вход блока 7 поступает импульс стирания, KOTopbrfi в нем инвертируется и включает режим записи блока 4 памяти. В ячейки блока 4 памяти записывается нулевое состояние, так как на установочный вход счетчика 3 подан сигнал сброса ((Ьиг.2Е). Таким образом, ячейки блока 4 памяти по адресу подготовлены к следующем циклу измерений. Затем с блока 5 выдается следующий код адреса.

0

0

5

0

5

Эти операции вьтолняются до тех пор, пока содержимое всех ячеек блока

4памяти не будет перенесено в блок

5вычислений, и все они не будут подготовлены к следующему циклу измерений. После этого устройство продолжит работу в режиме измерения пакетов и пауз.

В блоке 5 вычислений в соответствии с заданным алгоритмом осуществляется обработка результатов измерений с целью определения зaкoнoмepнocteй появления и группирования ошибок в исследуемом дискретном канале. Результаты обработки регистрируются в форме таблиц, графиков на соответствующих приборах, сопряженных с процессором блока 5.

Формула изобретения

1. Устройство для оценки качества передачи днскретньпс сигналов, содержащее блок выделения ошибок, таймер, формирователь адреса и последовательно соединенные формирователь тактовых импульсов, вход и выход которого соединен соответственно с сигнальным и тактовым входами блока выделения ошибок, блок управления, счетчик блок памяти и блок вычислений, адресные и управляющий входы и выходы блока памяти соединены соответственно с выходами формирователя адреса, с вторым выходом блока управления и с входами параллельной записи счетчика, отличающееся тем, что с целью расширения функциональных возможностей путем обеспечения измерения распределения длин пакетов ошибок и пауз между ними, введены формирователь коротких импульсов, измеритель паузы, последовательно соединенные измеритель длины пакета и регист и последовательно соединенные триггер, элемент задержки и элемент ИЛИ, при этом выход блока выделения ошибок подключен к первому управляющему входу измерителя паузы, к управляющему входу регистра и к входу установки триггера, выход которого подключен к управляющему входу измерителя длины.пакета и к второму входу блока управления, третий вход которого соединен с выходом

Г,

59238

элемента задержки и с входом формирователя коротких импульсов, выход которого подключен к второму управляющему входу измерителя паузы, сигнальный вход которого соединен с сигнальным входом измерителя длины пакета и с первым входом блока управления, третий выход которо10 го подключен к входу разрешения счета счетчика, установочный вход которого соединен с первым управляющим выходом блока вычислений, с первым управляющим входом формирователя

15 адреса, с четвертым входом блока

управления и с вторым входом элемента ИЛИ, выход которого подключен к второму управляющему входу формирователя адреса, первый, второй и третий

20 сигнальные входы которого соединены

5

0

5

0

5

0

5

соответственно с выходом регистра, с сигнальным выходом измерителя паузы, управляющий выход которого подключен к входу сброса триггера, и с адресным выходом блока вычислений, вход меток времени и выход стираний которого соединены соответственно с выхо дом таймера и с пятьм входом блока управления.

2.Устройство по п.1, о т л и - чающе.еся тем, что измеритель длины пакета выполнен в виде последовательно соединенных делителя частоты, мультиплексора и счетчика, выход которого соединен с управляющим входом мультиплексора и является выходом измерителя длины пакета, сигнальным и управляющим входами кото-- рого являются соответственно сигнальный вход делителя час готы и установочный вход счетчика, соединенный с установочным входом делителя частоты,

3,Устройство по п.1, о т л и - чающееся тем, что измеритель паузы выполнен в виде последовательно соединенных делителя частоты, мультиплексора и счетчика, выход которого соединен с управляющим мультиплексора и является сигнальным выходом измерителя паузы, управляющим выходом, сигнальным и первым и вторым управляющими входами которого являются соответственно соответствующий выход, сигнальный и установочный входы делителя частоты и установочный вход счетчика.

«V4

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1525694A1 |

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1984 |

|

SU1185617A2 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Устройство для записи и воспроизведения цифровой информации | 1990 |

|

SU1742856A1 |

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1982 |

|

SU1016845A1 |

Изобретение относится к электросвязи. Цель изобретения - расширение функциональных возможностей. Устройство для оценки качества передачи сигналов содержит блок выделения 1 ошибок, формирователь 2 тактовых импульсов, счетчик 3, блок памяти 4, блок вычислений 5, таймер 6, блок управления 7, измеритель 8 длины пакета, состоящий из делителя 16 частоты, мультиплексора 17 и счетчика 18, регистр 9, измеритель 10 паузы, состоящий из делителя 19 частоты, мультиплексора 20 и счетчика 21, триггер 11, эл-т задержки 12, формирователь 13 коротких импульсов, эл-т ИЛИ 14 и формирователь 15 адреса. Цель достигается путем измерения распределения длин пакетов ошибок и пауз между ними. Устройство по пп.2 и 3 ф-лы отличается выполнением измерителей 8 и 10. 2 з.п. ф-лы, 2 ил.

0

ф

г

u

Uj

| Устройство адаптивного приема дискретных сигналов | 1982 |

|

SU1113891A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для оценки качества передачи сигналов по линейному тракту цифровой системы передачи | 1986 |

|

SU1434554A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-11-30—Публикация

1988-02-10—Подача