, 1328941

относится к электросвяноци чи ам пр да ва

зи и может быть использовано в цифровых системах передачи с многоуровневыми сигналами.

Цель изобретения - увеличение времени удержания и уменьшение времени восстановления синхронизма.

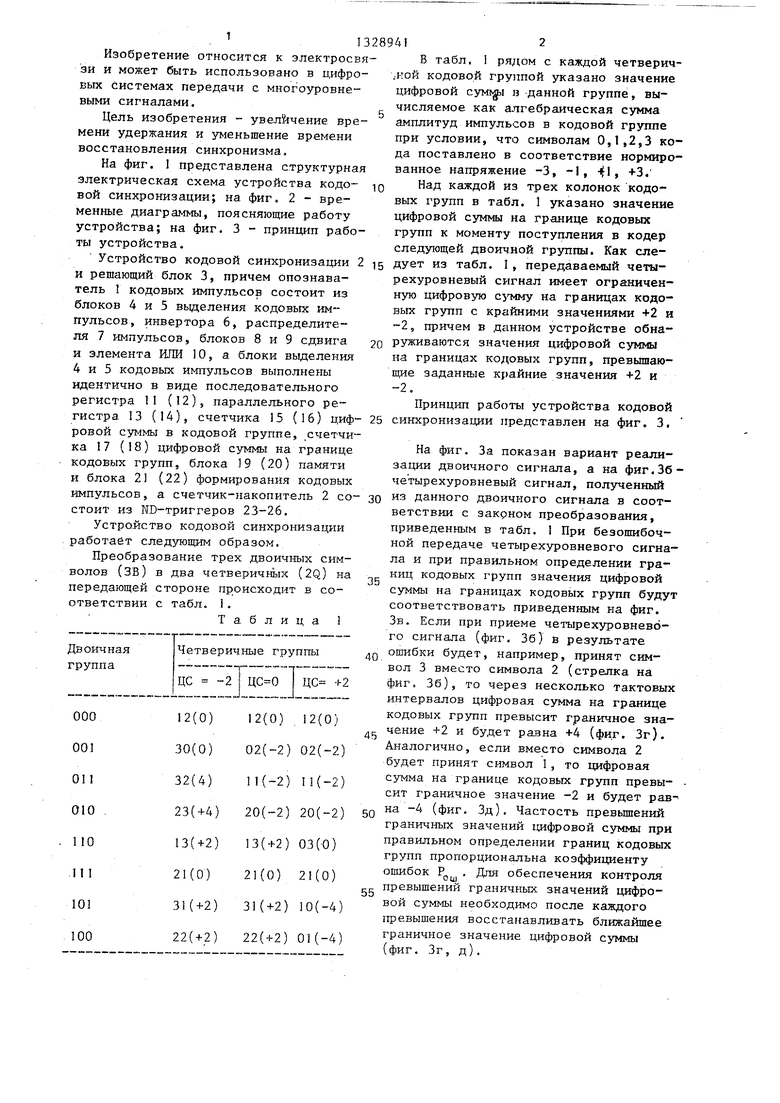

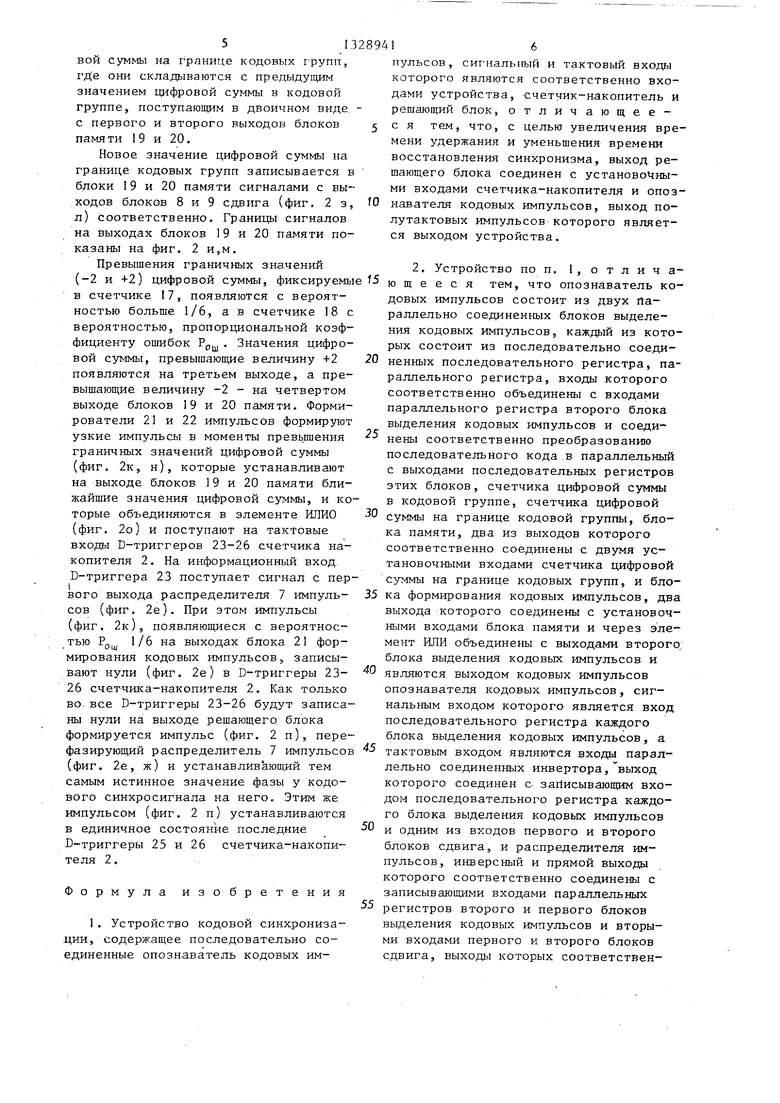

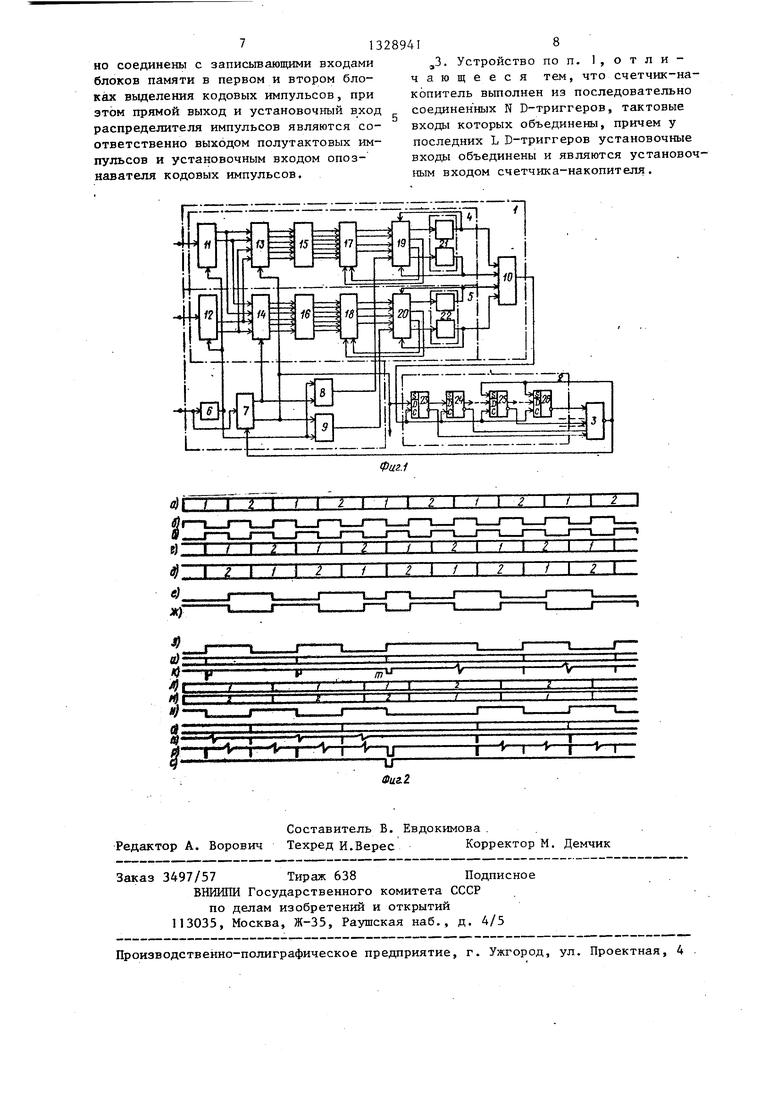

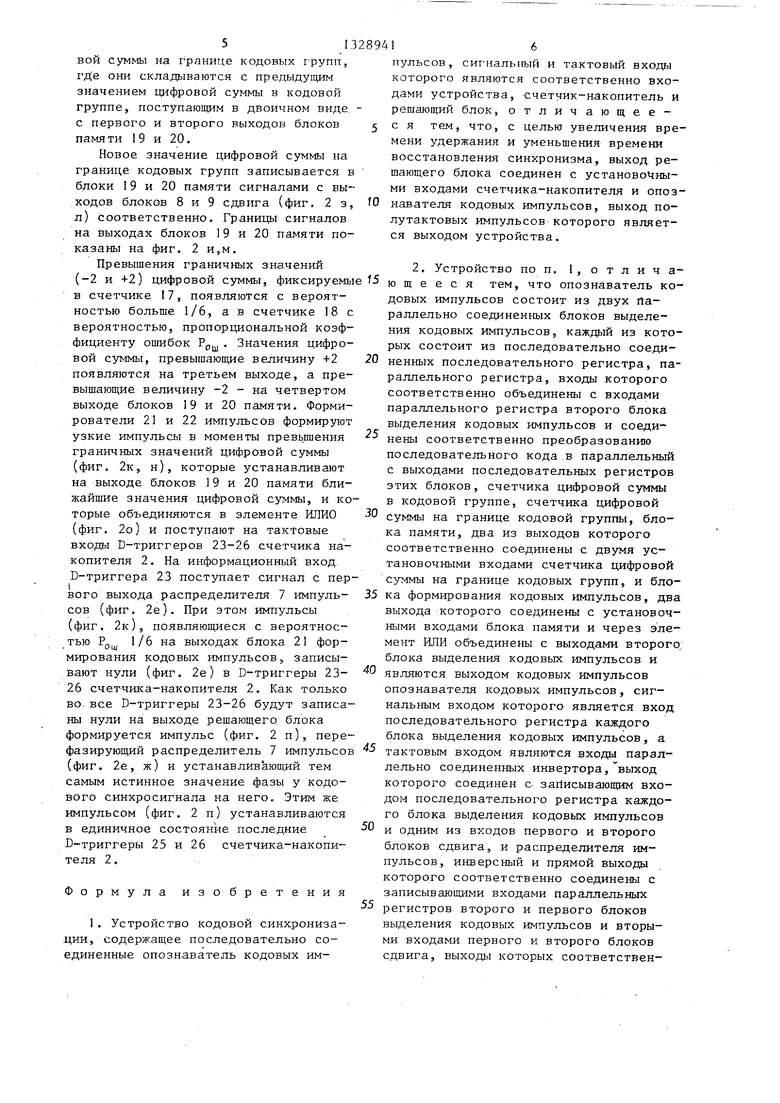

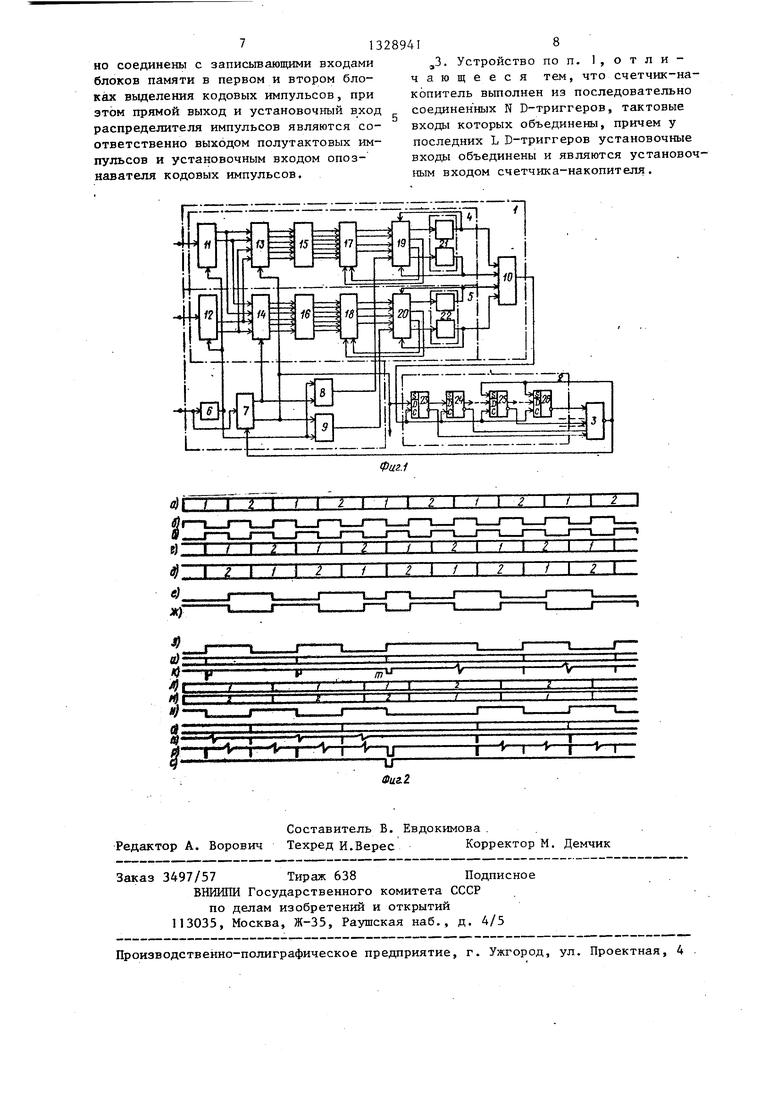

На фиг. I представлена структурная электрическая схема устройства кодовой синхронизации; на фиг. 2 - временные диаграммы, поясняющие работу устройства; на фиг. 3 - принцип работы устройства.

Устройство кодовой синхронизации 2 5 ДУет из табл. I, передаваемый четы20

рехуровневый сигнал имеет ограниченную цифровую С5ТЧМУ на границах кодо- вьпс групп с крайними значениями +2 и -2, причем в данном устройстве обнаруживаются значения цифровой суммы на границах кодовых групп, превышающие заданные крайние значения +2 к

и решающий блок 3, причем опознава- тель 1 кодовых импульсов состоит из блоков 4 и 5 вьвделения кодовых им-- пульсов, инвертора 6, распределителя 7 импульсов, блоков 8 и 9 сдвига и элемента ИЖ 10, а блоки вьщеления 4 и 5 кодовых импульсов выполнены идентично в виде последовательного -2.

регистра 11 (12), параллельного ре- Принцип работы устройства кодовой гистра 13 (14), счетчика 15 (16) циф- 25 синхронизации представлен на фиг. 3. ровой суммы в кодовой группе, счетчика 17 (18) цифровой суммы на границе кодовых групп, блока 19 (20) памяти и блока 21 (22) формирования кодовых импульсов, а счетчик-накопитель 2 состоит из ND-триггеров 23-26.

Устройство кодовой синхронизации работает следующим образом.

Преобразование трех двоичных символов (ЗВ) в два четве.ричнь1х (2Q) на передающей стороне происходит в соответствии с табл. i.

30

35

На фиг. За показан вариант реализации двоичного сигнала, а на фиг.Зб четырехуровневый сигнал, полученный из данного двоичного сигнала в соответствии с закрном преобразования, приведенным в табл. I При безошибочной передаче четырехуровневого сигнала и при правильном определении границ кодовых групп значения цифровой суммы на границах кодовых групп будут соотыетствовать приведенным на фиг. Зв. Если при приеме четырехуровневого сигнала (фиг. Зб) в результате оЕпибки будет, например, принят символ 3 вместо символа 2 (стрелка на фиг. 36), то через несколько тактовых интервалов цифровая сумма на границе кодовых групп превысит граничное значение +2 и будет равна +4 (фиг. Зг). Аналогично, если вместо символа 2 будет принят символ 1, то цифровая сумма на границе кодовых групп превысит граничное значение -2 и будет рав на -4 (фиг. Зд). Частость превьшений граничных значений хщфровой суммы при правильном определении границ кодовых групп пропорциональна коэффициенту ошибок Рр . Для обеспечения контроля (-р. превышений граничных значений цифровой суммы необходимо после каждого превышения восстанавливать ближайшее граничное значение цифровой суммы (фиг. Зг, д).

Таблица 1

Б табл. 1 рядом с каждой четверичной кодовой группой указано значение цифровой в данной группе, вычисляемое как алгебраическая сумма амплитуд импульсов в кодовой группе при условии, что символам 0,1,2,3 кода поставлено в соответствие нормированное напряжение -3, -1, , +3.

Над каждой из трех колонок кодовых групп в табл. 1 указано значение цифровой суммы на границе кодовых групп к моменту поступления в кодер следующей двоичной группы. Как еле-

рехуровневый сигнал имеет ограниченную цифровую С5ТЧМУ на границах кодо- вьпс групп с крайними значениями +2 и -2, причем в данном устройстве обнаруживаются значения цифровой суммы на границах кодовых групп, превышающие заданные крайние значения +2 к

-2.

Принцип работы устройства кодовой синхронизации представлен на фиг. 3.

На фиг. За показан вариант реализации двоичного сигнала, а на фиг.Зб- четырехуровневый сигнал, полученный из данного двоичного сигнала в соответствии с закрном преобразования, приведенным в табл. I При безошибочной передаче четырехуровневого сигнала и при правильном определении границ кодовых групп значения цифровой суммы на границах кодовых групп будут соотыетствовать приведенным на фиг. Зв. Если при приеме четырехуровневого сигнала (фиг. Зб) в результате оЕпибки будет, например, принят символ 3 вместо символа 2 (стрелка на фиг. 36), то через несколько тактовых интервалов цифровая сумма на границе кодовых групп превысит граничное значение +2 и будет равна +4 (фиг. Зг). Аналогично, если вместо символа 2 будет принят символ 1, то цифровая сумма на границе кодовых групп превысит граничное значение -2 и будет рав- на -4 (фиг. Зд). Частость превьшений граничных значений хщфровой суммы при правильном определении границ кодовых групп пропорциональна коэффициенту ошибок Рр . Для обеспечения контроля превышений граничных значений цифровой суммы необходимо после каждого превышения восстанавливать ближайшее граничное значение цифровой суммы (фиг. Зг, д).

3

Случай неправильного определения границ кодовых групп для того же четырехуровневого сигнала изображен на фиг. Зе. Значения цифровой суммы на границах кодовых групп в этом случае представлены на.фиг. Зж. Причем вероятность превышения граничных значений цифровой суммы при неправильном определении границ кодовых групп больше 1/6.

Различия в вероятностях превышений граничных значений цифровой суммы при правильном и неправильном определении границ кодовых групп являются основой для построения устройства кодовой - синхронизации ,в цифровой системе передачи с кодом ЗВ2Й.

Устройство кодовой синхронизации предназначено для работы в системах передачи цифровой информации с кодом по радиотрактам с частотной модуляцией. -При приеме частотно-модулированного сигнала на корреляционный детектор квадратурных составляющих на его выходах образуются два двоичных сигнала Ч и у , являющиеся представлением в коде Грея четверичных символов 0,1,2,3 (фиг. 3 з,и).

Двоичные цифровые сигналы у и у границы импульсов которых показаны на фиг. 2а поступают на входные пгины соответственно и записываются в последовательные регистры 11 и 12 сигналом тактовой частоты с выхода инвертора 6 (фиг. 2в). Границы первого и второго импульсов (фиг. Зи, з) Z и Z в кодовой группе находятся на первом и втором выходах первого последовательного регистра 11 и первого и второго импульсов Zj и Z (фиг. Зи) на первом и втором выходах второго последовательного регистра 12 (фиг. 2г, д).. Распределитель 7 импульсов, который для кода 3B2U является делителем. на 2 с прямым и инверсным выходами, формирует две импульсные последовательности (фиг. 2 е,ж), одна из которых является кодовым синхросигналом.

Рассмотрим процесс вхождения в син хронизм, т.е. процесс, приводяш;ий к совпадению положительного фронта импульса в кодовом синхросигнале (фиг. 2е) с началом первого импульса в кодовой группе (фиг. 2а).

Первые Z , Z и вторые Z , Z импульсы (фиг. 2г,д) двоичных сигналов Y записываются в параллельный регистр 13 сигналом с первого

10

15

28941

выхода распределителя 7 импульсов (фиг. 2е), а в параллельный регистр 14- сигналом с второго выхода распределителя 7 (фиг. 2ж). Сигналы с выходов параллельных регистров 13 и 14 поступают соответственно на входы счетчиков I5 и 16 цифровой суммы в кодовой группе, причем в счетчике 15 подсчитывается цифровая сумма второго импульса в данной кодовой группе и первого импульса в следующей, а в C4et4mce 16- цифровая сумма импульсов в кодовой группе.

Алгоритм подсчета цифровой суммы двух соседних импульсов представлен в табл. 2.

Таблица2

С выходов счетчиков 15 и 16 цифровой суммы в кодовой группе значения цифровой суммы, представленные в двоичном виде, поступают соответственно на входы счетчиков 17 и 18 цифро513

вой суммы на границе кодовых г рупп, где они складываются с предыдущим значением цифровой суммы в кодовой групне, ноступающим в двоичном виде, с первого и второго выходов блоков памяти 19 и 20.

Новое значение цифровой суммы на границе кодовых групп записывается в блоки 19 и 20 памяти сигналами с вы- .ходов блоков 8 и 9 сдвига (фиг, 23, л) соответственно. Границы сигналов на выходах блоков 19 и 20 памяти показаны на фиг. 2 и,м,

Превышения граничных значений (-2 и +2) цифровой суммы, фиксируемы в счетчике 17, появляются с вероятностью больше 1/6, а в счетчике 18 с вероятностью, пропорциональной коэффициенту опгабок РОЩ, Значения цифровой суммы, превышающие величину +2 появляются на третьем выходе, а превышающие величину -2 - на четвертом выходе блоков 19 и 20 памяти. Формирователи 21 и 22 импульсов формируют узкие импульсы в моменты превьппения граничных значений цифровой суммы (фиг, 2к, н), которые устанавливают на выходе блоков 19 и 20 памяти ближайшие значения цифровой суммы, и которые объединяются в элементе ИЛИО (фиг, 2о) и поступают на тактовые входы D-триггеров 23-26 счетчика накопителя 2, На информационшзш вход, D-триггера 23 поступает сигнал с первого выхода распределителя 7 импуль- сов (фиг, 2е), При этом импульсы (фиг, 2к), появляющиеся с вероятностью Р,щ 1/6 на выходах блока 21 формирования кодовых импульсов, записывают нули (фиг, 2е) в D-триггеры 23- 26 счетчика-накопителя 2, Как только во. все D-триггеры 23-26 будут записаны нули на выходе решающего, блока формируется импульс (фиг, 2 п), перефазирующий распределитель 7 импульсов (фиг. 2е, ж) и устанавлив ающий тем самым истинное значение фазы у кодового синхросигнала на него. Этим же импульсом (фиг, 2 п) устанавливаются

в единичное состояние последдие D-триггеры 25 и 26 счетчика-накопителя 2.

Формула изобретения

1. Устройство кодовой синхрониза- .ции, содержащее последовательно соединенные опознаватель кодовых им5

O

f5 0 0 5

0

5

пульсов, сиг яальный и тактовый входы которого являются соответственно входами устройства, счетчик-накопитель и решающий блок, отличающее- с я тем, что, с целью увеличения времени удержания и уменьшения времени восстановления синхронизма, выход решающего блока соединен с установочными входами счетчика-накопителя и опоз- навателя кодовых импульсов, выход полутактовых импульсов которого является выходом устройства,

2, Устройство по п, 1, о т л и ч а- ю щ е е с я тем, что опознаватель кодовых импульсов состоит из двух параллельно соедд1нен1л 1х блоков выделения кодовых импульсов, каждый из которых состоит из последовательно соединенных последовательного регистра, параллельного регистра, входы которого соответственно объединены с входами параллельного регистра второго блока выделения кодовых импульсов и соединены соответственно преобразованию последовательного кода ,в параллельный с выходами последовательных регистров этих блоков, счетчика цифровой суммы в кодовой группе, счетчика цифровой суммы на границе кодовой группы, блока памяти, два из выходов которого соответственно соединены с двумя установочными входами счетчика цифровой суммы на границе кодовых групп, и блока формирования кодовых импульсов, два выхода которого соединены с установочными входами блока памяти и через элемент ИЛИ объединены с выходами второго. блока выделения кодовых импульсов и являются выходом кодовых импульсов опознавателя кодовых импульсов, сигнальным входом которого является вход последовательного регистра каждого блока выделения кодовых импульсов, а тактовым входом являются входы параллельно соединенных инвертора,выход которого соединен с зайисывающим входом последовательного регистра каждого блока выделения кодовых импульсов и одним из входов первого и второго блоков сдвига, и распределителя импульсов, инверсный и прямой выходы которого соответственно соединены с записывающими входами параллельных регистров второго и первого блоков выделения кодовых импульсов и вторыми входами первого и второго блоков сдвига, выходы которых соответствен113289418

но соединены с записьгоающими входами ,3, Устройство по п, 1, о т л и - блоков памяти в первом и втором бло- чающееся тем, что счетчик-на- ках вьщеления кодовых импульсов, при копитель выполнен из последовательно этом прямой выход и установочный вход соединен ных N D-триггеров, тактовые распределителя импульсов являются со- входы которых объединены, причем у

ответственно выходом полутактовых импульсов и установочным входом опоз- навателя кодовых импульсов.

последних L D-триггеров установочные входы объединены и являются установочным входом счетчика-накопителя.

IГЦ

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер балансного кода 3B2Q | 1987 |

|

SU1531223A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Кодер кода 3В2 @ | 1984 |

|

SU1244803A1 |

| Кодер двоичного кода 3В4В-3 | 1986 |

|

SU1444964A1 |

| Устройство регистрации ошибок | 1985 |

|

SU1478346A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Устройство кодовой синхронизации | 1988 |

|

SU1640831A2 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

Изобретение м.б. использовано в цифровых системах передачи с многоуровневыми сигналами. Цель изобретения - увеличение времени удержания и уменьшение времени восстановления синхронизма. Устр-во содержит опозна- ватель кодовых импульсов, счетчик-накопитель и решающий блок. Принцип работы устр-ва представлен на фиг. 3. На фиг. За приведен двоичный сигнал, на ил. Зб - четырехуровневый сигнал (ЧУС). При безошибочной передаче ЧУС Чеп йеричные синК/1Ы JИ иу и при правильном определении границ кодовых групп (кг) значения цифровой суммы (ЦС) на границах КГ соответствуют приведенным на фиг. Зв. Если при приеме ЧУС в р зульта те ошибки будет принят символ 3 вместо 2, то ЦС на границе КГ превысит граничное значение +2 и будет равна +4 (фиг. Зг). Если вместо символа 2 будет принят символ 1, то ЦС на границе КГ превысит граничное значение -2 и будет равна -4 (фиг. Зд), Случай неправильного определения границ КГ показан на фиг. Зе. Значения ЦС на границах КГ приведены на фиг. Зж. Вероятность превышения граничных значений ЦС при неправильном определении границ КГ больше 1/6. Устр-во предназначено для работы в системах передачи цифровой информации с кодом ЗВ20 по радиотрактам с частотной модуляцией. 2 табл., 2 3. п. ф-лы , 3 ил. § (Л : эо :о 4;

Т I 2 I /

Т / Т

i 2

I

| Колтунов М.Н | |||

| и др | |||

| Синхронизация по циклам в цифровых системах связи | |||

| М.: Связь, 1980, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-08-07—Публикация

1985-03-11—Подача