(21)4176676/24-24

(22)06.01.87

(46) 07.11.88. Бюл. Р 41

(72) Е.А.Шурмухин и Л.Н.Ким

(53) 621.394 :681.325(088.8)

(56) Авторское свидетельство СССР

1141577, кл. Н 03 М 13/00, 1983.

Авторское свидетельство СССР 1249708, кл. Н 03 М 13/00-, 1985.

(54) УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ДЕКОДИРОВАНИЯ

(57) Изобретение относится к вычислительной технике. Его использование в системах передачи и обработки информации позволяет упростить схему устройства. Устройство для мажоритарного декодирования содержит блок 1 управления, элементы 2 памяти и мажоритарные элементы 4. Введение решающего блока 3 обеспечивает автоматическое управление выбором такта, декодирование для каждого символа входного циклического кода, благодаря чему схема устройства упрощается. 1 з.п. ф-лы, 3 ил. 2 табл.

(Л

С

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки информации,

Цель изобретения - упрощение устройства.

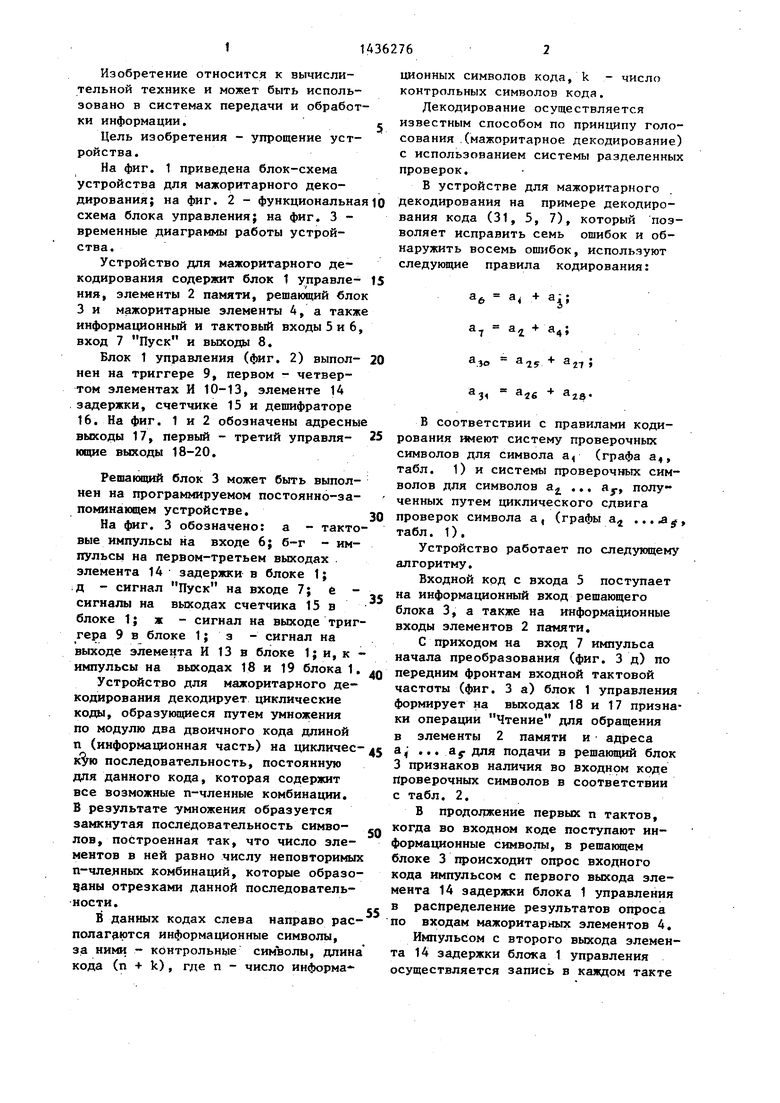

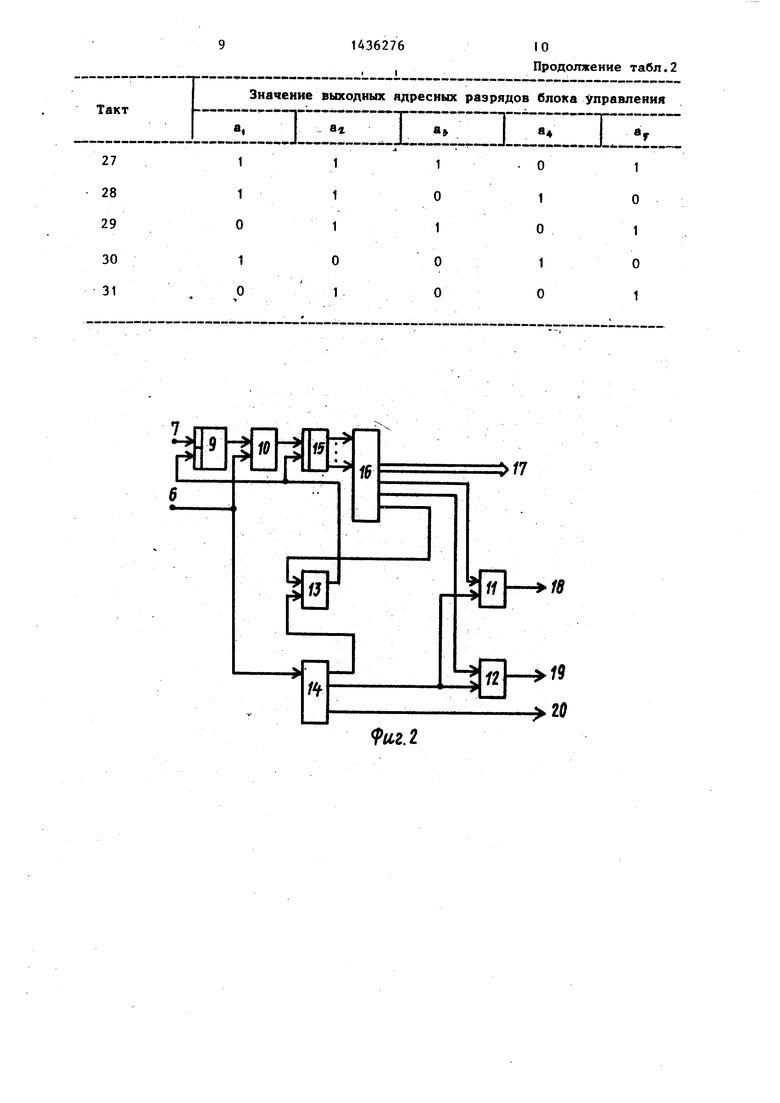

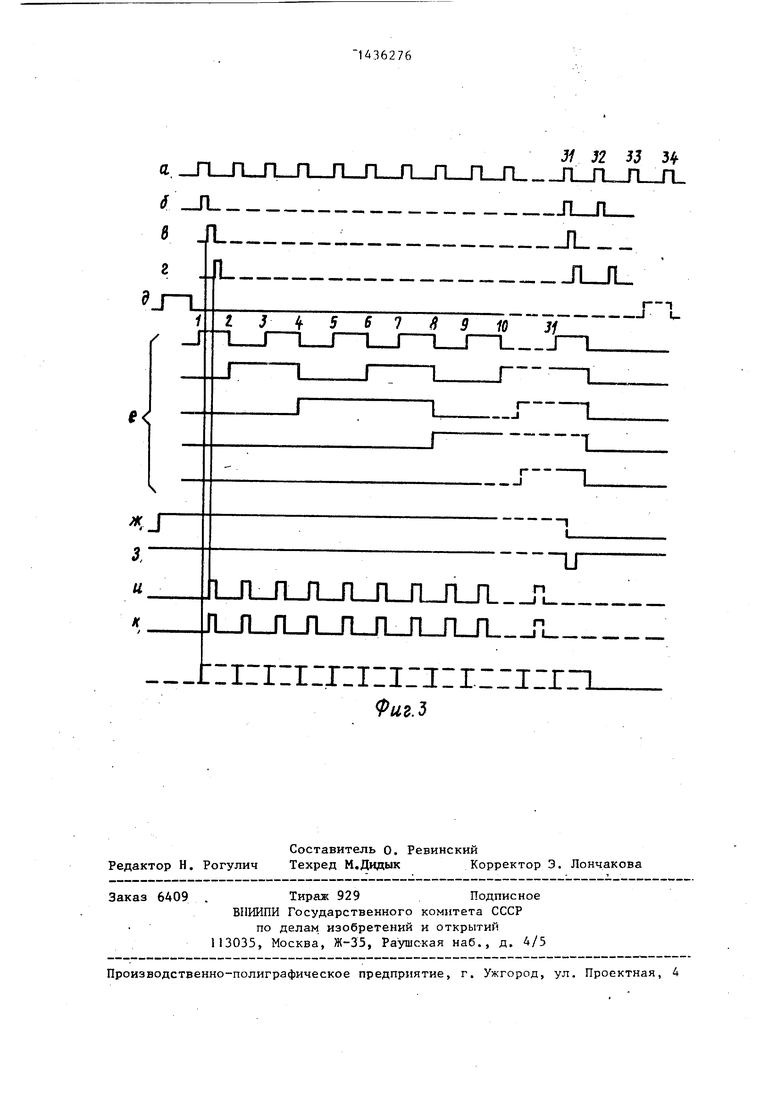

На фиг. 1 приведена блок-схема устройства для мажоритарного декодирования; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - временные диаграммы работы устройства.

Устройство для мажоритарного декодирования содержит блок 1 управле- ния, элементы 2 памяти, решающий блок 3 и мажоритарные элементы А, а также информационный и тактовый входы 5 и 6, вход 7 Пуск и выходы 8.

Блок 1 управления (фиг. 2) выпол- нен на триггере 9, первом - четвертом элементах И 10-13, элементе 14 . задержки, счетчике 15 и дешифраторе 16. На фиг. 1 и 2 обозначены адресные выходы 17, первый - третий управля- ющие выходы 18-20.

Решающий блок 3 может быть выполнен на программируемом постоянно-запоминающем устройстве.

На фиг. 3 обозначено: а - тактовые импульсы на входе 6; б-г - импульсы на первом-третьем выходах . элемента 14 задержки в блоке 1; .д - сигнал Пуск на входе 7; е - сигналы на выходах счетчика 15 в блоке 1; ж - сигнал на выходе триггера 9 в блоке 1; 3 - сигнал на выходе элемента И 13 в блоке 1; и, к - импульсы на выходах 18 и 19 блока 1.

Устройство для мажоритарного декодирования декодирует циклические коды, образующиеся путем умножения по модулю два двоичного кода длиной п (информационная часть) на цикличес- кЗгю последовательность, постоянную для данного кода, которая содержит все возможные п-членные комбинации. В результате умножения образуется замкнутая последовательность симво

лов, построенная так, что число элементов в ней равно числу неповторимых п-члелных комбинаций, которые образованы отрезками данной последовательности.

В данных кодах слева направо рас- полаг ются информационные символы, за ними - контрольные символы, длина кода (п + k), где п - число информа ционных символов кода, k - число контрольных символов кода.

Декодирование осуществляется известным способом по принципу голосования (мажоритарное декодирование) с использованием системы разделенных проверок.

В устройстве для мажоритарного декодирования на примере декодирования кода (31, 5, 7), который позволяет исправить семь ошибок и обнаружить восемь ошибок, используют следующие правила кодирования:

е, а -f aj; а- э.„ -I- а.;

.эо 25 + aj,7 ;

31

2fi

« а

28

в соответствии с правилами кодирования имеют систему проверочных символов для символа а (графа а4, табл. 1) и системы проверочных символов для символов а 2 ... а у, полученных путем циклического сдвига проверок символа а, (графы а ....а, табл. 1).

Устройство работает по следующему алгоритму.

Входной код с входа 5 поступает на информационный вход решающего блока 3, а также на информационные входы элементов 2 памяти.

С приходом на вход 7 импульса начала преобразования (фиг. 3 д) по передним фронтам входной тактовой частоты (фиг. 3 а) блок 1 управления формирует на выходах 18 и 17 признаки операции Чтение для обращения в элементы 2 памяти и адреса а i ... а j для подачи в решающий блок 3 признаков наличия во входном коде проверочных символов в соответствии с табл. 2.

В продолжение первых п тактов, когда во входном коде поступают информационные символы, в решающем блоке 3 происходит опрос входного кода импульсом с первого выхода элемента 14 задержки блока 1 управления в распределение результатов опроса по входам мажоритарных элементов 4.

Импульсом с второго выхода элемента 14 задержки блока 1 управления осуществляется запись в каждом такте

входных символов в элементы 2 памяти по соответствующим адресам,

В продолжение следующих k тактов, когда во входном коде поступают проверочные символы, в решающем блоке 3 происходит опрос импульсом опроса с выходного блока 1 запрограммированного результата сложения по модулю

В продолжение следующих k тактов решающий блок 3 по адресам из блока 1 управления формирует после опроса опросным импульсом запрограммированную проверочную сумму входного символа со считанным по тем же адресам из соответствующего элемента 2 памяти символом, который является вторым

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство мажоритарного декодирования | 1985 |

|

SU1249708A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Устройство для мажоритарного декодирования | 1975 |

|

SU607349A1 |

| Распределенная система для программного управления с мажоритированием | 1990 |

|

SU1727112A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА СБОРА И ОБРАБОТКИ ДАННЫХ ЭЛЕКТРОННОГО ГОЛОСОВАНИЯ ГАС "ВЫБОРЫ" | 2005 |

|

RU2291483C1 |

два символа входного кода с символом, ю слагаемым для входного символа, считанным из соответствующего элемен- После выдачи необходимых в данном та 2 памяти на вторые адресные входы такте проверочных сумм на мажоритар- решающего блока 3, с вьщачей резуль- ные элементы 4 производится запись в тата на входы мажоритарных элементов. Далее импульсвм с второго выхода элемента 14 задержки символ входэлементы 2 памяти входного сигнала по 15 адресам данного такта.

По окончании цикла декодирования (п + k тактов) в мажоритарных эле- . ментах 4 методом голосования принимается решение о значении i-ro симного кода записывается в элементы 2 памяти по соответствующим адресам. После прихода последнего импульса входного кода мажоритарные элемен- 20 вола, и это значение поступает на

ты принимают решение методом голосования по большинству о значении информационного символа и выдает его на выходы 8 устройства.

Устройство работает следующим образом.

Последовательный кой поступает на входы п элементов 2 памяти и символ .за символом записывается в них. Од- : новременно последовательный код поступает на информационный вход решающего блока 3.

Процесс декодирования начинается с приходом на вход 7 импульса начала преобразования, который соответствует началу кодовой посылки.

Импульс начала преобразования устанавливает в нулевое состояние счетчики мажоритарных элементов 4 и в единичное состояние - триггер 9 блока 1 управления, разрешая прохождение импульсов тактовой частоты через элемент И 10 на вход Счетчика 15 блока 1 управления.

Дешифратор 16 блока 1 управления вьфабатывает п + k адресов обращения к элементам 2 памяти. Эти же адреса подаются и на решающий блок 3, По этим адресам первые п тактов в решающем блоке 3 происходит опрос вход- них информационных символов импульсами с первого выхода элемента 14 задержки блока 1 управления и выдача их на соответствующие входы мажоритарных элементов 4 и осуществляется 55 Ройства, отличающееся

запись входных символов,в элементы 2 памяти по импульсам с второго выхода элемента 14 задержки блока 1 управ- ления.

тем, что, с целью упрощения устр ства, в него введен решающий блок выходы которого подключены к инфо мационным входам соответствующих

слагаемым для входного символа, После выдачи необходимых в данном такте проверочных сумм на мажоритар- ные элементы 4 производится запись в

элементы 2 памяти входного сигнала по адресам данного такта.

По окончании цикла декодирования (п + k тактов) в мажоритарных эле- ментах 4 методом голосования принимается решение о значении i-ro симвыходы 8 устройства.

В блоке 1 управления на дешифраторе 16 вьоделяется признак конца цикла декодирования, который после

опроса на элементе И 13 импульсом с третьего выхода элемента 14 задержки производит сброс счетчика 15 и триггера 9 блока 1 управления. Таким образом, в предлагаемом

устройстве для мажоритарного декодирования осуществляется автоматическое управление выбором такта декодирования для каждого a.j с помощью решающего блока, что позволяет исключить блок коррекции и кольцевой регистр и упростить блок управления.

Формула изобретения

с установочным входом блока управления и являются входом Пуск устройства, первый и второй управляющие выходы блока управления подключены соответственно к первым и вторым

управляющим входам элементов памяти, тактовый вход блока управления является тактовым входом устройства, выходы мажоритарных элемейтов являются соответствующими выходами устРойства, отличающееся

тем, что, с целью упрощения устройства, в него введен решающий блок, выходы которого подключены к информационным входам соответствующих

которого объединен с информационными входами элементов памяти и является яяфорйационным входом устройства, адресные выходы блока управления соединены с одноименными первыми адресными входами решаю1цего блока и сооТ9С ствунящми адресными входами

5143627$6

мажоритарных элементов, третий уп- элемента залержки и .является такто- равляювщй выход блока управления вым входом блока, выход первого эле- соединен с управляющим входом ре мента И подключен к счетному входу шакяцего блока, информационный вход счетчика, выходы которого соединены

с входами дешифратора, первые выходы которого являются адресными выходами блока, второй и третий выходы дешифратора подключены к первым входам со- 10 ответственно второго и третьего элементов И, выходы которых являются . соответственно первым и вторым управ- элементов памяти, выходы которых под- лямщими выходами блока, четвертый ключены к Соответствующим вторым ад-. , выход дешифратора соединен с Первым ресиЫм в содам peiffanatero блока, 1в входом четвертого элемента И, выход

2 Устройство по и 1, которого подключен к входам обнуления чающееся тем, что блок уйрав- триггера и счетчика, первый выход ления выполнен на счетчике, дешифра- элемента задержки является третьим торе элементе задержки, элементах управляюпщм выходом блока, второй И и триггере, установочный вход кото- 20 выход элемента эадержки соединен с рого является установочным входом вторыми входами второго и третьего блока, выход триггера соединен с пер- элементов И, третий выход элемента вым входом первого элемента И, второй задержки подключен к второму входу вход которого- объединен с входом четвертого элемента И.

VТаблица1

Таблица 2

tf ЛП Р

В JT« -JL«

г .П.TLJL

JL

3,Н-и

« rUT-JLJlJLJLJl, IJLJLJIJLJUIJI

iii:i:r:i:iri:ririrrn

W2.3

Составитель О. Ревинский Редактор Н. Рогулич Техред М.Дидык Корректор Э. Лончакова

Заказ 6А09 . Тираж 929Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

31 д2 33 3

J

-I

Авторы

Даты

1988-11-07—Публикация

1987-01-06—Подача