го

тей за счет обеспечения оперативной компоновки программ регулирования из типовых подпрограмм. Устройство содержит блок 1 памяти, регистр 2 адреса,, регистр 3 времени, делитель 4 частоты,, реверсивный счетчик 5, генератор 6 импульсов, регистр 7 задания, первый элемент И 8, первый 9 и второй 10 элементы ИЛИ, первый 11 и второй 12 элементы задержки, блок 13 хранения адресов, пульт 14 управления, управляющий счетчик 15, второй элемент И 16, третий элемент 17 задержки, В устройстве реализована можность скачкообразного изменения содержимого регистра (счетчика) адреса путем подстановки в него адреса

считываемой программы из блока хранения адресов, что приводит к организации произвольной очередности считывания программ. Изменение данной очередности выполнения программ осуществляется с помощью оперативного изменения программы, записанной в блоке хранения адресов, в результате подачи соответствующих сигналов с пульта управления. Таким образом обеспечивается возможность компоновки программ регулирования из типовых подпрограмм, т.е. возможно получение любых программ регулирования без изменения очередности следования элементарных программ регулирования в основном блоке памяти. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного регулирования | 1988 |

|

SU1524024A2 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Система для контроля и испытаний блоков памяти бортовых ЭВМ | 1984 |

|

SU1182526A1 |

| Устройство для программного управления | 1988 |

|

SU1520480A1 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для программного управления разгоном и торможением двигателя | 1986 |

|

SU1314309A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1476434A1 |

Изобретение относится к автоматике и вьгчислительной технике и предназначено для программного регулирования технологических процессов н является дополнительным к авт.св. N 1156006. Целью изобретения является расширение функциональных возможное

t

Изобретение относи тся к автоматике и вычислительной технике и пред- казначено для программного регулиро вания технологических процессов.

Цепью изобретения является расши-- рение функциональных возможностей за счет обеспечения оперативной компоновки программы регулирования из типовых подпрограмм.

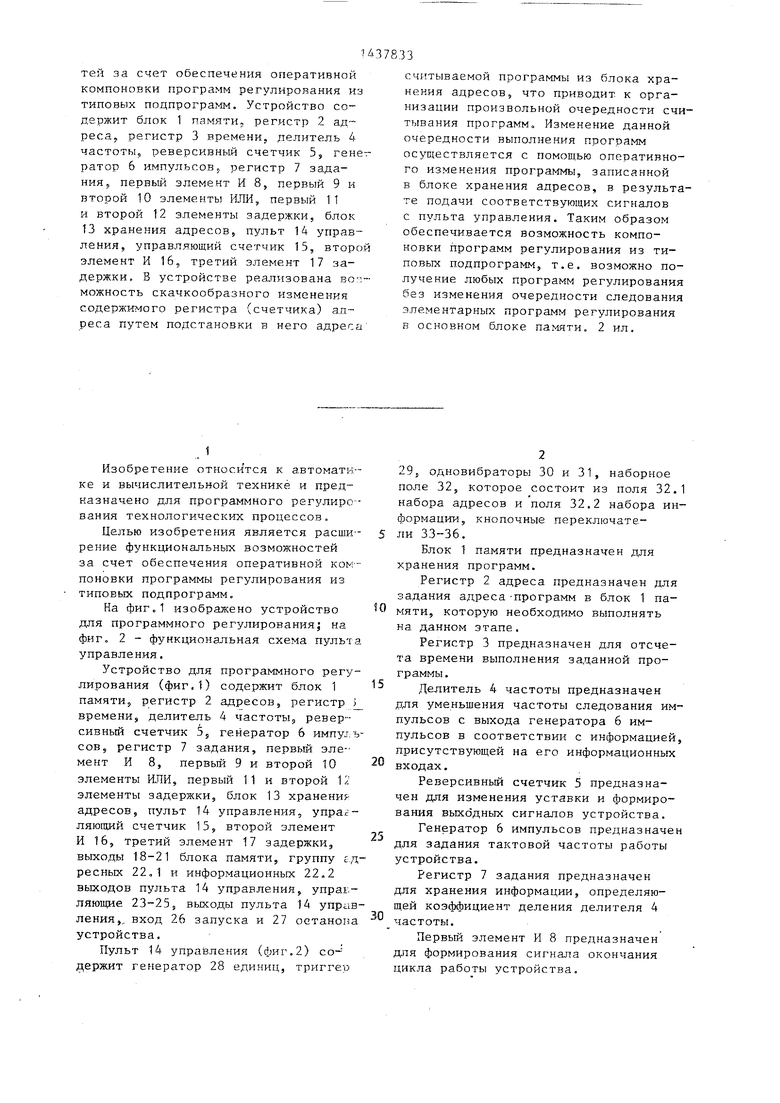

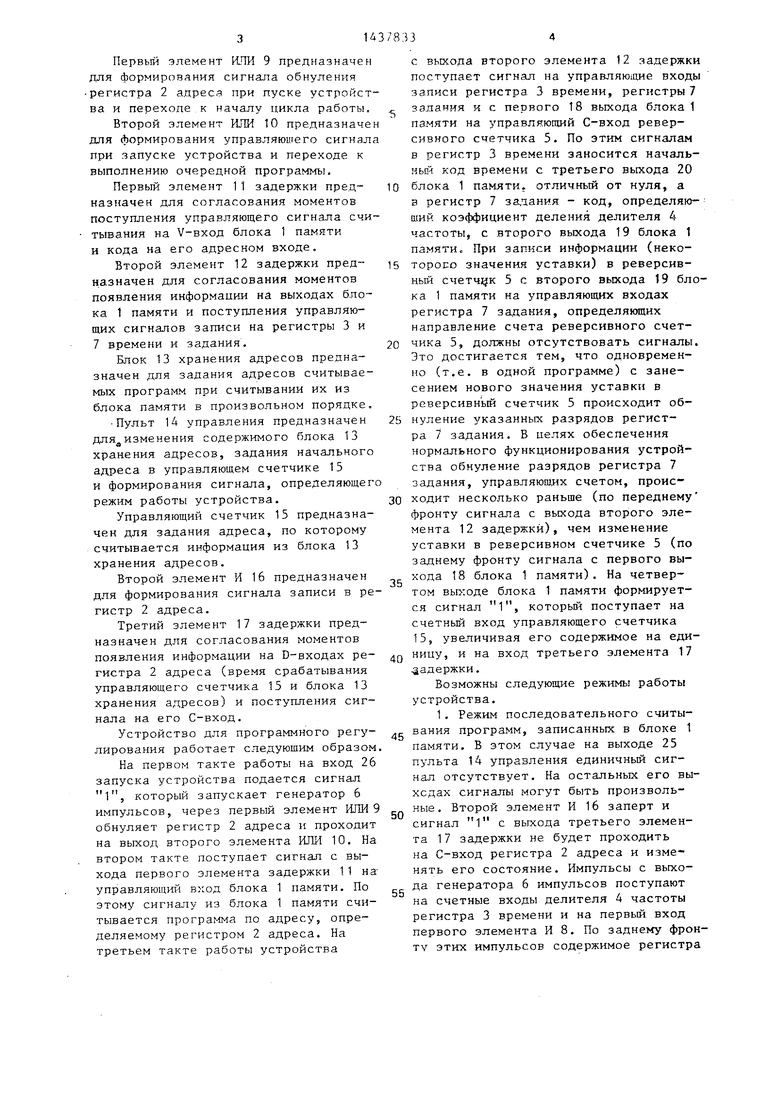

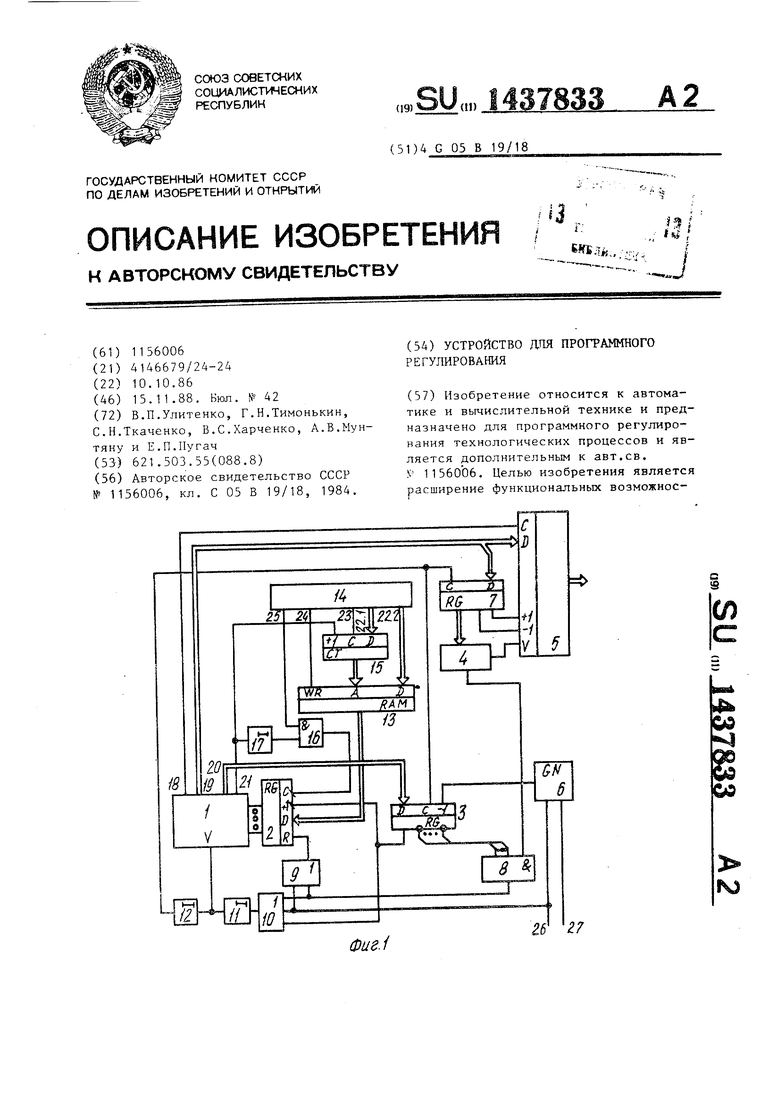

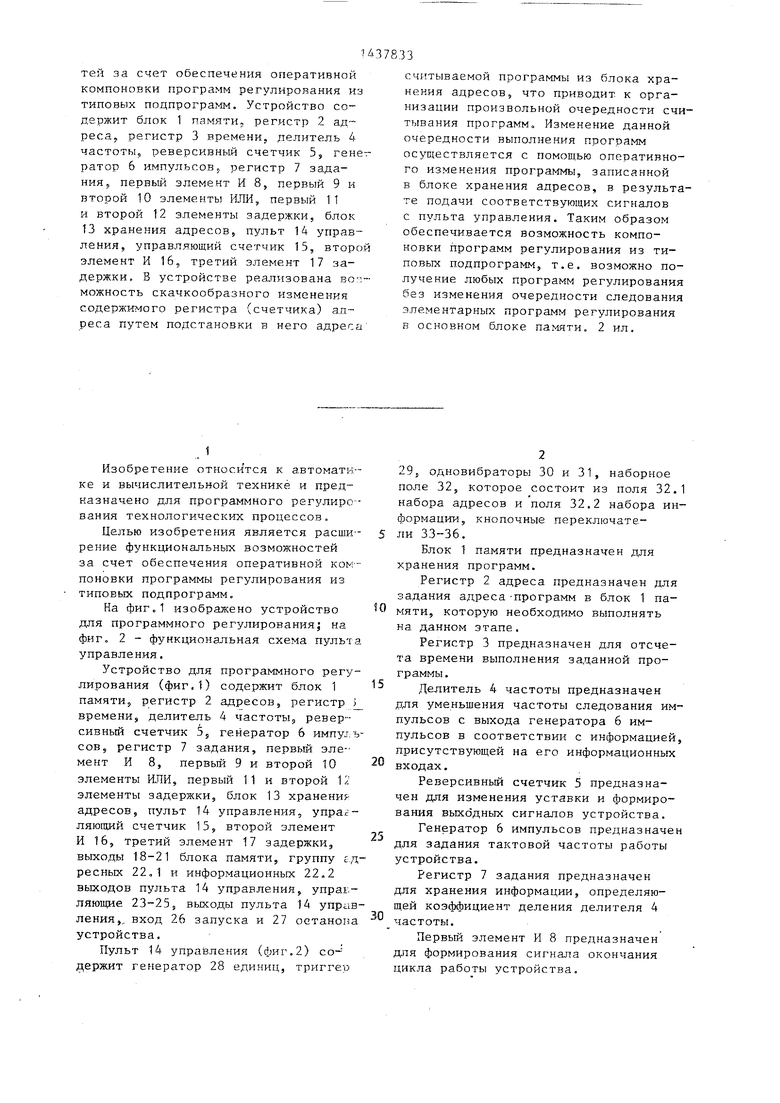

На фиг.1 изображено устройство для программного регулирования; на фиг о 2 - функциональная схема пульта управления.

Устройство для программного регулирования (фиг,1) содержит блок 1 памяти, регистр 2 адресов, регистр i времени, делитель 4 частоты, реверсивный счетчик 5j генератор 6 импу1;Ъ- сов, регистр 7 задания, первый эле-- мент И 8, первый 9 и второй 10 элементы ИЛИ, первый 11 и второй 12 элементы задержки, блок 13 хранения адресов, пульт 14 управления, управляющий счетчик 15, второй элемент И 16, третий элемент 17 задержки, выходы 18-21 блока памяти, группу Е.Д- ресных 22,1 и информационных 22,2 выходов пульта 14 управления, упраг,- ляющие 23-25, выходы пульта 14 управления,,, вход 26 запуска и 27 останопа устройства.

Пульт 14 управления (фиг.2) со- ; ержит генератор 28 единиц, триггер

29 одновибраторы 30 и 31, наборное поле 32, которое состоит из поля 32.1 набора адресов и поля 32.2 набора информации, кнопочные переключате- ли 33-36.

Блок 1 памяти предназначен для хранения программ.

Регистр 2 адреса предназначен для задания адреса -программ в блок 1 па- 0 мяти, которую необходимо выполнять на данном этапе.

Регистр 3 предназначен для отсчета времени выполнения заданной программы.

Делитель 4 частоты предназначен да;ля уменьшения частоты следования импульсов с выхода генератора 6 импульсов в соответствии с информацией, присутствующей на его информационных входах.

Реверсивный счетчик 5 предназначен для изменения уставки и формирования выходных сигналов устройства.

Генератор 6 импульсов предназначен для задания тактовой частоты работы устройства.

Регистр 7 задания предназначен для хранения информации, определяю- ш.ей коэффициент деления делителя 4 частоты.

Первый элемент И 8 предназначен для формирования сигнала окончания цикла работы устройства.

5

0

Первьй элемент ИЛИ 9 предназначен для формирования сигнала обнуления регистра 2 адреса при пуске устройства и переходе к началу цикла работы.

Второй элемент ИЛИ 10 предназначе для формирования управляюшего сигнал при запуске устройства и переходе к выполнению очередной программы.

Первый элемент 11 задержки пред- назначен для согласования моментов поступления управляющего сигнала считывания на V-вход блока 1 памяти и кода на его адресном входе.

Второй элемент 12 задержки пред- назначен для согласования моментов появления информации на выходах блока 1 памяти и поступления управляющих сигналов записи на регистры 3 и 7 времени и задания.

Блок 13 хранения адресов предназначен для задания адресов считываемых программ при считывании их из блока памяти в произвольном порядке.

Пульт 14 управления предназначен длЯдизменения содержимого блока 13 хранения адресов, задания начального адреса в управляющем счетчике 15 и формирования сигнала, определяющег режим работы устройства.

Управляющий счетчик 15 предназначен для задания адреса, по которому считывается информация из блока 13 хранения адресов.

Второй элемент И 16 предназначен для формирования сигнала записи в регистр 2 адреса.

Третий элемент 17 задержки предназначен для согласования моментов появления информации на D-входах ре- гистра 2 адреса (время срабатывания управляющего счетчика 15 и блока 13 хранения адресов) и поступления сигнала на его С-вход.

Устройство для программного регу- лирования работает следующим образом

На первом такте работы на вход 26 запуска устройства подается сигнал 1, который запускает генератор 6 импульсов, через первый элемент ИЛИ 9 обнуляет регистр 2 адреса и проходит на выход второго элемента ИЛИ 10. На втором такте поступает сигнал с выхода первого элемента задержки 11 на управляющий вкоц. блока 1 памяти. По этому сигналу из блока 1 памяти считывается программа по адресу, определяемому регистром 2 адреса. На третьем такте работы устройства

с выхода второго элемента 12 задержки поступает сигнал на управляю цие входы записи регистра 3 времени, регистры 7 задания и с первого 18 выхода блока 1 памяти на управляющий С-вход реверсивного счетчика 5. По этим сигналам в регистр 3 времени заносится начальный код времени с третьего выхода 20 блока 1 памяти, отличный от нуля, а в регистр 7 задания - код, определяющий коэффициент деления делителя 4 частоты, с второго выхода 19 блока 1 памяти. При записи информации (некоторого значения уставки) в реверсивный счетш к 5 с второго выхода 19 блока 1 памяти на управляющих входах регистра 7 задания, определяющих направление счета реверсивного счетчика 5, должны отсутствовать сигналы. Это достигается тем, что одновременно (т.е. в одной программе) с занесением нового значения уставки в реверсивн ый счетчик 5 происходит обнуление указанных разрядов регистра 7 задания. В целях обеспечения нормального функционирования устройства обнуление разрядов регистра 7 задания, управляющих счетом, происходит несколько раньще (по переднему фронту сигнала с выхода второго элемента 12 задержки), чем изменение уставки в реверсивном счетчике 5 (по заднему фронту сигнала с первого выхода 18 блока 1 памяти). На четвертом выходе блока 1 памяти формируется сигнал 1, который поступает на счетный вход управляющего счетчика 15, увеличивая его содержимое на единицу, и на вход третьего элемента 17 задержки.

Возможны следующие режимы работы устройства.

3 времени уменьшается на единицу. При полном обнулении регистра 3 времени на его выходе переполнения формируется единичный сигнал, который, поступая на счетный вход регистра 2 адреса,

увеличивает его содержимое на единицу,

а через второй элемент ИЛИ 10 определяет начало работы по новой программе. Если выполняемая программа преду-10 Работы устройства. Перед считыванием

гистр 2 адреса по сигналу, поступившему на С-вход регистра 2 адреса. Эта информация задает адрес, уменьшенный на единицу, той ячейки блока 1 памяти, где хранится программа, выполняемая на следующем этапе. Переход к выполнению очередной программы происходит, как и в первом режиме

программы из блока 1 памяти содержимое регистра 2 адреса увеличивается на единицу. При каждом появлении сиг нала на выходе 21 блока 1 памяти содержимое управляющего счетчика 15 увеличивается на единицу, из блока 1 хранения адресов считывается и записывается в регистр 2 адреса новая ин формация. Переход к новому циклу расматривает плавное изменение содержимого реверсивного счетчика 5 в течение некоторого времени, то в этом случае в регистр 7 задания записывается код, определяющий скорость из- менения уставки реверсивного счетчика 5 и направление изменения. Сигналы с выхода делителя 4 частоты, поступая на счетный вход реверсивного счетчика 5, в зависимости от сигналов на входах управления направлением счета увеличивают либо уменьшают содержимое реверсивного счетчика 5.

Выполнение последней программы, содержащейся в блоке 1 памяти, сопро- вождается вьздачей в регистр 3 времени нулевого кода. Б результате чего по сигналу, поступившему на С-вход

регистра 3 времени, состояние его не изменяется, на инверсных выходах будут по-прежнему присутствовать единичные сигналы. Очередной импульс с выхода генератора 6 импульсов проходит на выход первого элемента И 8 и далее поступает через первьш элемент ИЛИ на вход обнуления регистра 2 адреса, а через второй элемент ИЛИ 10 и первьй элемент 11 задержки на управляющий V-вход блока 1 памяти. Весь цикл работы устройства повторяется заново.. Останов устройства осуществляется подачей сигнала на вход 27 о станова устройства.

На выходе 25 пульта 14 управления присутствует единичный сигнал. На выходах 23 и 24 сигналы отсутствуют. Если после выполнения программы, хранящейся в блоке 1 памяти в ячейке с нулевым адресом (эта программа выполняется всегда первой в обоих режимах) , требуется выполнить некоторую заданную программу, то в управляющий счетчик 15 заносится некото- рьм начальный код. По адресу, .определяемому этим кодом, считывается информация из блока 13 хранения адресов, которая переписывается в регистр 2 адреса по сигналу, поступившему на С-вход регистра 2 адреса. Эта информация задает адрес, уменьшенный на единицу, той ячейки блока 1 памяти, где хранится программа, выполняемая на следующем этапе. Переход к выполнению очередной программы происходит, как и в первом режиме

5

программы из блока 1 памяти содержимое регистра 2 адреса увеличивается на единицу. При каждом появлении сигнала на выходе 21 блока 1 памяти содержимое управляющего счетчика 15 увеличивается на единицу, из блока 13 хранения адресов считывается и записывается в регистр 2 адреса новая информация. Переход к новому циклу ра0

0

5

боты и останов устройства в данном режиме сопровождается процессами, описанными выше.

Пульт 14 управления работает следующим образом.

С помощью переключателей наборного поля 32 набирается некоторая информация, поступающая на выход 22 пульта 14. С помощью кнопочных переключателей 33 и 34 триггер 29 устанавливается соответственно в единичное или нулевое состояние. Состояние триггера 29 определяет режим работы устройства в целом. С помощью кнопочных переключателей 35 и 36 запускаются одновибраторы 30 и 31 и сигналы, формируемые ими, поступают на выходы 23 и 24 пульта 14 управления.

В случае необходимости возможно перепрограммирование блока 13 хранения Q адресов и выполнение нового цикла, отличного от,предыдущего.

Для перепрограммирования блока 13 хранения адресов набирается информация на наборных полях 32.1 и 32.2 пульта 14 управления (см. фиг.2). По сигналу, сформированному на выходе 23 пульта 14, код, набранный на адресных выходах 22.1, записывается в управляющий счетчик 15, который задает адрес ячейки блока 13 хранения адресов, в которой происходит изменение информации. По сигналу, сформированному на выходе 24 пульта 14 управления, новая информация с информационных выходов 20.2 пульта 14 записывается в блок 13 хранения адресов. Далее на наборных полях набирается очередные адреса и информации и весь процесс записи повторяется. Так n.Do5

0

5

7

должается до тех пор, пока не будет закончено требуемое обновление со- .держимого блока 13 хранения адресов

Появление сигнала 1 на четвертом выходе 21 блока 1 памяти определяется при программировании. Этот сигнал может присутствовать в каждой программе. Тогда, подставляя в регистр 2 адреса кода из блока 13 хранения адресов, возможно выполнение программ, записанных в блоке 1 памяти в произвольном порядке. Если сигнал 1 на четвертом выходе 21 появляется только при выполнении определенных программ, то обеспечивается комбинирование первого и второго режима работы. На участках, когда на четвертом выходе 21 сигнал отсутствует, устройство будет работать, как в первом режиме (состояние регистра 2 адреса изменяется при поступлении импульсов на его счетный вход).

Таким образом, устройство обладает более широкими функциональными возможностями за счет обеспечения оперативной постановки программы регулирования из набора типовых подпрограмм без увеличения общего объема памяти программы регулирования. Кроме того, увеличивая объем блока хранения адресов, можно при том же количестве программ в результате многократного обращения к ним строить более длинные циклы работы устройства. Это приводит к значительному сокращению объема памяти.

10

15

20

25

30

35

8338

Формула изобретения Устройство для программного регулирования по авт, св. N- 1156006, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения оперативной компоновки программы регулирования из типовьгх подпрограмм, дополнительно содержит блок хранения адресов, пульт управления, управляющий счетчик, второй элемент И и третий элемент задержки, причем четвер- тьй выход блока памяти соединен со счетным входом управляющего счетчика . и вхсЩом третьего элемента задержки, выход которого соединен с первьм входом второго элемента И, группа выходов управляющего счетчика соединена с группой адресньск входов блока хранения адресов, группа выходов которого соединена с группой информационных входов регистра адреса, группа информационных выходов пульта управления соединена с информационными входами блока хранения адресов, а группа адресных выходов пульта управления с оединена с информационными входами управляющего счетчика, первый и второй управляющие выходы пульта управления соединены с управляющими входами управляющего счетчика и блока хранения .адресов соответственно, третий выход пульта управления соединен с вторыми входами второго элемента И, выход которого соединен с управляющим входом регистра адреса, при этом выход первого элемента И подключен к третьему входу второго элемента ИЛИ.

| Устройство для программного регулирования | 1983 |

|

SU1156006A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-11-15—Публикация

1986-10-10—Подача