каждого канала, выход которого и соот ветствующий управляющий вход устройва, через соединенные последовательно память и первый элемент И того же канала соединен с соответствующими синхронизирующим выходом устройства, вылод третьего элемента И соединен с входами первого элемента И и третьего счетчика каждого канала и через третий счетчик - с входом третьего триггера и входами второго и третьего элементов И каждого канала,выход первого триггера.каждого канала соединен с соответствующим входом четвертого элемента И, выход которого через второй коммутатор соединен с управляющим выходом устройства, выход второго регистра соединен с входом схемы сравнения, выходы первого регистра соединены с входами первого триггера и второго счетчика каждого канала, выходы второго счетчика каждого кана, ла соединены с входами третьего и чет вертого узлов элементов И и входами первого и второго триггеров того же канала,, первый выход второго триггера каждого канала соединен с входами второго элемента И, третьего узла элементов И и через первый элемент И-НЕс входом первого буферного регистра того же канала, второй выход второго. триггера каждого канапа соединен с входами третьего элемента И, четвертого узла элементов И и через второй элемент И-НЕ - с входом второго буферного регистра того же канапа, выходы второго элемента И и четвертого узла элементов и каждого канапа через второй узел элементов ИЛИ того же канала соединены с входом второго буферного регистра того же канала, выходы третьего элемента И и третьего узла элемента И каждого канала через третий узел элементов ИЛИ того же канала соединены с входом первого буферного регистра того же канала , вы ход первого счетчика каждого канала соединен с входом первого узла элементов И того же канаiha.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1986 |

|

SU1381523A2 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1987 |

|

SU1437870A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Многоканальное устройство для сопряжения | 1985 |

|

SU1282142A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

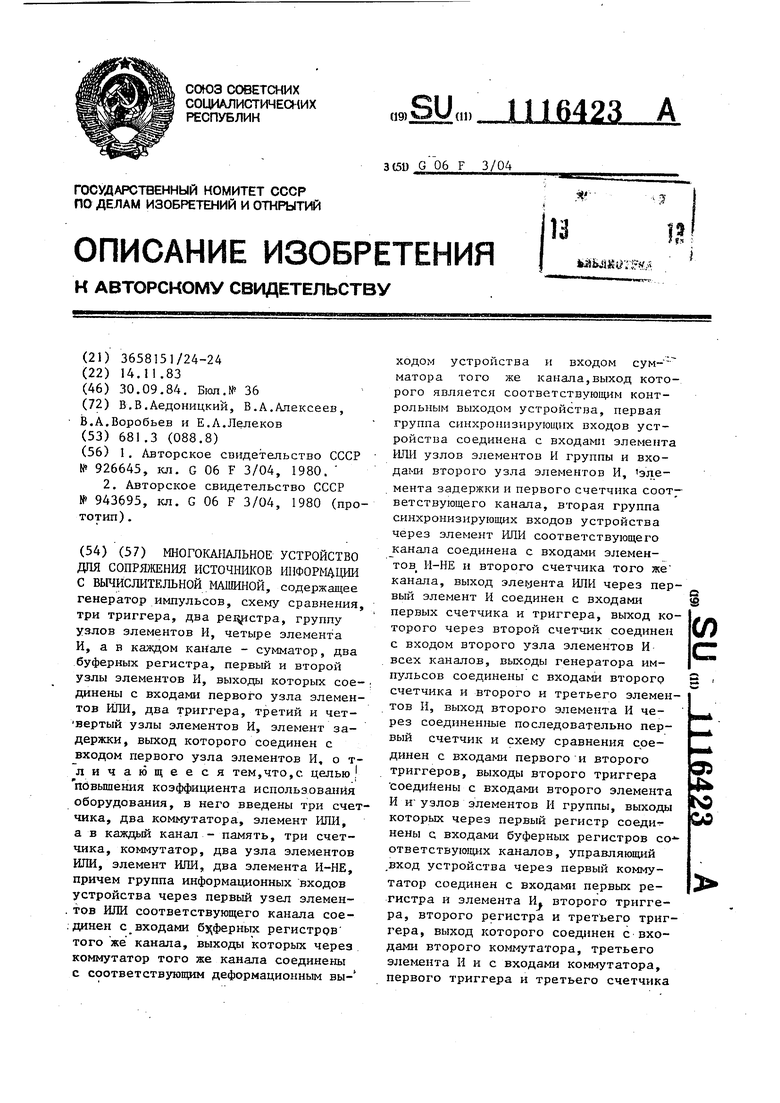

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНЖОВ ИНФОРМАЦИИ С ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ, содержащее генератор импульсов, схему сравнения, три триггера, два , группу узлов элементов И, четыре элемента И, а в каждом каНале - сумматор, два буферных регистра, первый и второй узлы элементов И, выходы которых соединены с входами первого узла элементов ИЛИ, два триггера, третий и четвертый узлы элементов И, элемент задержки, выход которого соединен с входом первого узла элементов И, о т личающееся тем,что,с целью . повышения коэффициента использования оборудования, в него введены три счетчика, два коммутатора, элемент ИЛИ, а в каждый канал - память, три счетчика, коммутатор, два узла элементов ИЛИ, элемент ШШ, два элемента И-НЕ, причем группа информационных входов устройства через первьШ узел элементов ШШ соответствующего канала сое. динен с входами б)ферных регистров того же канала, выходы которых через коммутатор того же канала соединены с соответствующим деформационным выff ; k bJiSil Bf ходом устройства и входом сум- матора того же канала,выход которого является соответствую1цим контрольным выходом устройства, первая группа синхронизирующих сходов устройства соединена с входами элемента ИЛИ узлов элементов И группы и входами второго узла элементов И, элемента задержки и первого счетчика соответствующего канала, вторая группа синхронизирующих входов устройства через элемент ИЛИ соответствующего канала соединена с входами элементов И-НЕ и второго счетчика того же канала, выход элемента ИЛИ через первый элемент И соединен с входами первых счетчика и триггера, выход ко(Л торого через второй счетчик соединен с: с входом второго узла элементов И всех каналов, выходы генератора импульсов соединены с входами второго счетчика и второго и третьего элементов И, выход второго элемента И через соединенные последовательно первый счетчик и схему сравнения соединен с входами первого и второго № Jd триггеров, выходы второго триггера соединены с входами второго элемента N0 И И узлов элементов И группы, выходы : которых через первый регистр соеди-г нены с, входами буферных регистров соответствуюц;их каналов, управляющий вход устройства через первый комму татор соединен с входами первых регистра и элемента И. второго триггера, второго регистра и третьего триггера, выход которого соединен с входами второго KOMT-iyTaTopa, третьего элемента И и с входами коммутатора, первого триггера и третьего счетчика

Изобретение относится к вычисли.тельной технике и может быть исполь;зовано в системах обработки многоканальной информации, поступающей в вычислительную машину (ВМ) от удаленных несинхронизированных между собой групп источников.

Известно многоканальное устройство для сопряжения источников информации с цифровой вычислительной машиной, содержаще блок формирования адреса, блок памяти, генератор, три регистра, элемент ИЛИ, коммутаторы, триггер, а в каждом канале - коммутатор, три регистра, память, два триггера, элементы ИЛИ, И Cl3 .

Недостатки этого устройства обус.ловлены большим объемом аппаратурных затрат и отсутствием привязки информационных потоков к времени,

Наиболее близким по технической сущности к изобретению является многоканальное устройство для сопряже ния, содержащее генератор импульсов.

схему сравнения, три триггера, два регистра, группу узлов элементов И, четыре элемента И, а в каждом канале сумматор, два буферных регистра, первый и второй узлы элементов И, выхо- ды которых соединены с входами первого узла элементов ИЛИ, два триггера, третий и четвертый узлы элементов И, элемент задержки, выход которого соединен с входом первого узла элементов И С 21 .

Недостатком устройства-прототипа является его низкая эффективность ввода в ВМ асинхронных информационных потоков.

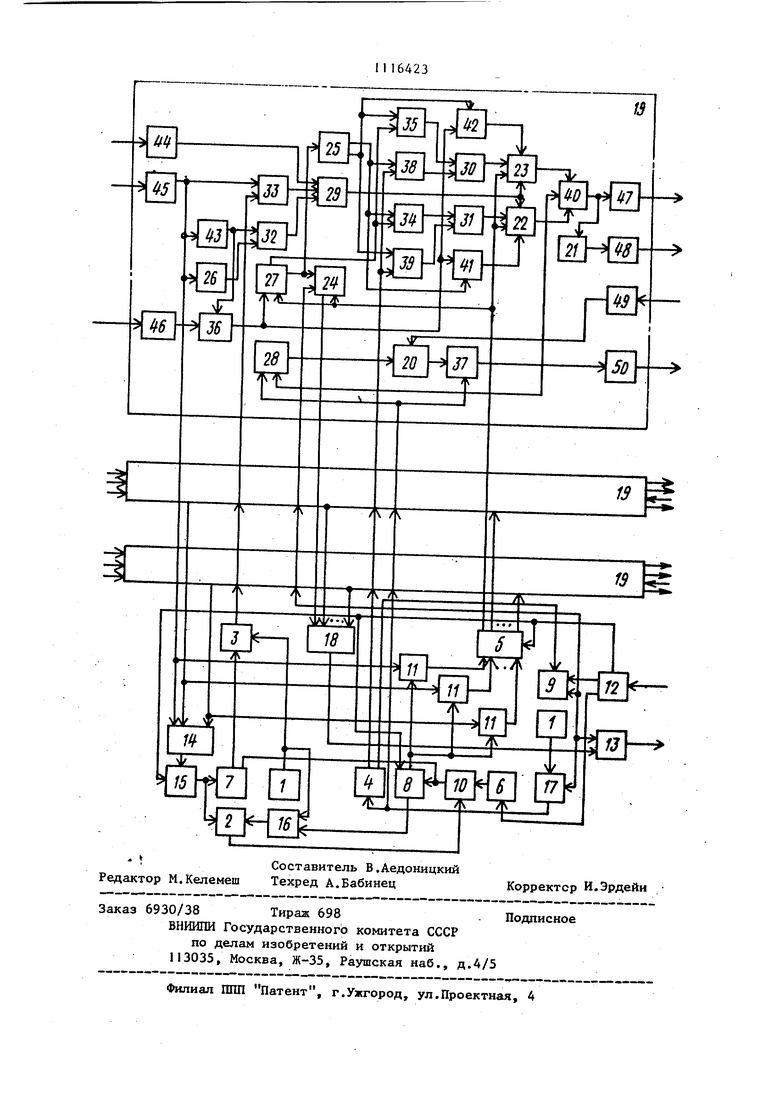

Устройство-прототип вводит информацию в ВМ непрерывно со скоростью ее поступления от внешних источников. Как правило эта скорость существенно ниже пропускной способности каналов ввода /вывода (вв/выв) ВМ. Однако максимальная пропускная способность каналов вв/выв не достигается, так как эти каналы оказываются занятыми в основном вводом ин(1юрмацин только от внешних источников и не могут производить внутримашинные н другие обмены информацией. Цель изобретения - повышение коэффициеата использования оборудования . Поставленная цель достигается тем что в многоканальное устройство для сопряжения источников информации с вычислительной машиной, содержащее генератор импульсов, схему сравнения три триггера, два регистра, группу узлов элементов И, четыре элемента И, а в каждом канале - сумматор,два буферных регистра, первый и второй узлы элементов И, выходы которых со динены с входами первого узла элемен тов ИЛИ. два триггера, третий и чет вертый узлы элементов И, элемент за держки, выход которого соединен с вх дом первого узла элементов И, введен три счетчика, два коммутатора, элеме ИЛИ, а в каждый канал - память,три счетчика, коммутатор, два узла элеме I тов или, элеме /iT ИЛИ, два элемента И-НЕ, причем группа информационных входов устройства через первый узел элементов ИЛИ соответствующего канала соединена с входами буферных регистров того же канала, выходы которых через коммутатор того же канала соединены с сответствующим информационным выходом устройства и входом сумматора того же канала, выход кото рого является соответствующим контрольным выходом устройства, первая группа синхронизирующих входов устройства соединена с входами элемента ИЛИ узлов элементов И группы и вхоДами второго узла элементов И, элеме та задержки и первого счетчика соответствующего канала, вторая группа синхронизирующих входов устройства через элемент ИЛИ соответствующего канала соединена с входами элементов И-НЕ и второго счетчика того же кана ла, выход элемента ИЛИ через первый элемент И соединен с входами первых счетчика и триггера, выход которого через второй счетчик соединен с входом второго узла элементов И всех ка налов, выходы генератора импульсов соединены с входами второго счетчика и второго и третьего элементов И, вы ход ..второго элемента И через соеди ненные последовательно первый счетчик и схему сравнения соединен с вхо дами первого и второго триггеров,выходы второго триггера соединены с входами второго элемента И и узлов элементов И группы, выходы которьпс через первьш регистр соединены с входами буферных регистров соответствующих каналов, управляющий вход устройства (Через первый коммутатор соединен с входами первых регистра и элемента И, второго триггера, второго регистра и третьего триггера, выход которого соединен с входами второго коммутатора, третьего элемента И и с входами коммутатора, первого триггера и третьего счетчика каждого канала, выход которого и соответствующий управляющий вход устройства через соединенные последовательно память и первый элемент И того же канала соединен с соответствующим синхронизирующим выходом устройства, выход третьего элемента И соединен с входами первого элемента И и третьего счетчика каждого канала и через третий счетчик - с входом третьего триггера и входами второго и третьего элементов И каждого канала,выход первого триггера дого канала соединен с соответствующим входом четвертого элемента И,выход которого через второй коммутатор соединен с управлякяцим выходом устройства, выход второго регистра соединен с входом схемы сравнения, выхо- . ды первого регистра соединены с вхо-дами первого триггера и второго счетчнка каждого канала, выходы второго счетчика каждого канала соединены с входами третьего и четвертого ,узлов элементов И и входами первого и второго триггеров того же канала, первый выход второго-триггера каждого канала соединен с вхбдамл второго элемента И, третьего узла элементов И и через первый элемент И-НЕ - с входом первого буферного регистра того же канала, второй выход второго триггера каждого канала соединен с выходами третьего элемента И, четвертого узла элементов И и через второй элемент И-НЕ - с входом второго буферного регистра того же канала, выходы второго элемента И и четвертого узла элементов И каждого канала через второй узел элементов ИЛИ того же канала соединены с входом второго буферного регистра того же канала, выходы третьего элемента И и третьего узла элементов И каждого канала через третий узел элементов Ш1И того же канала соединены с входом первого буферного регистра того же канала, }выход первого счетчика каждого канал соединен с входом первого узла элементов И того же канала. На чертеже пpiJвeдeнaблoк-cxeмa предлагаемого устройства. Устройство содержит генератор i импульсов,, счетчики 2-4, регистры 5 и 6, триггеры 7 - 9, схему Ш срав нения, группу уэлов 11 элементов И, коммутаторы 12 и 13, элемент РШИ 14, элементы И 5-18, каналы 19, Каждый канал 19 содержит память 20, сумматор 21, буферные регистры 22 и 23, триггеры 24 и 25, счетчики 26-28, узлы 29-31 элементов PlTIIi, узлы 32-35 элементов И, элемент ИЛИ 36, элементы И 37-39, коммутатор 40, элементы И-НЕ 41 и 42, элемент 43 задерлски, согласующие узлы 44-50, Устройство работает следующ.им образом. Все источники информации опрашиваются примерно с одинаковой частотой, которая для каждого из источников задается тактовыми импульсами (ТИ), поступающими через вторые тактовые входы, Однократньм опрос всех источников информации одной группы образует кадр, который сопровождается .кадровы импульсом (КИ), поступающим на входы первые тактовые. Каждая группа источников информации обслуживается своим каналом 19 и синхронизируется своим генератором импульсов, расположенным вместе с ис точниками информации И, Поэтому ( с учетом .нестабильности генераторов им пульсов, произвольности момента нача ла опроса Источников информации в каждой группе, а также задернсек пере дачи череЭ лиьши связи) КИ поступают в разные каналы в произвольные момен ты времени. Дпя одновременного ввода информации в ВМ со всех каналов необ ходимо произвести выравнивание момен тов окончания загрузки регистров 22 и 23 всех каналов к единому моменту времени, с которого может быть начат этот ввод. ,В работе устройства следует вьщелить два основных режима работы пбдготовительный и рабочий. Подготовительный режим начинается с момента записи кода времени в регистр 6, поступающего из ВМ через коммутатор 12 и определяющего максимальное значение временного интервала, .необходимого для ввода одного массива информации в ВМ, Одновременно с подачей кода времени Bi4 снимает сигнал прерывания ввода, поступающий на элемент И 15, триггер 8 управления, регистр 5 разрешения ввода, и триггер 9 считывания, снимая их блокировку и обеспечивая готовность устройства к работе, В каждом канале вторые синхросигналы через согласующие узлы 45 поступают на элемент ИЛИ 14, с выхода которого через элемент И 15 объединенный поток синхросигналов поступает на входы установки О счетчика 2 тактов и триггера 7 управления. Счетчик 2 тактов предназначен для измерения длите.льности временных интервалов между кадровььми синхросигналами. Он подсчитывает тактовые и мпульсы , поступающие с выхода генератора 1 импульсов через элемент И 16 при наличии разрешающего сигнала с триггера 8, предварительно установленного в исходное пололсение сигналом прерывания ввода. Схема 10 сравнения формирует сигнал при совпадении кодов счетчика 2 и регистра 6, т,е, при обнаружении временного интервала между первыми синхросигналами, равного или превышающего заданную длительность, определенную значением кода, записанного из ВМ в регистр 6, Сигнал совпадения поступает на входы триггеров 7 и 8, изменяя их состояние, С этого момента триггер 8 блокирует элемент И 16, запрещая подачу на счетчик 2 импульсов с генератора 1, Сигналом с другого выхода триггер 8 разрешает через узлы II вьщачу первых синхроимпульсов на регистр 5, С выхода регистраз сигналы разрешения поступают в каждом канале на входы счетчика 27 адреса записи, триггера 24 готовности, регистров 22 и 23, снимая их блокировку и переводя в рабочий режим. Триггер 7 готовности опорным первым синхросигналом, пришедшим после сигнала совпадения с вькода схемы 10 сравнения, вновь устанавливается в исходное состояние, формируя на своем выходе импульсный сигнал, которьй поступает на вход установки О счетчика 3 времени задержки, который подсчитывает тактовые импульсы с выхода генератора 4, формируя тем самым код времени задержки поступления

первых синхросигналов относительно опорного первого синхросигнала.

Рабочий режим устройства обеспечивает запись и считывание информации в регистрах 22 и 23 поочередно накапливаю1цих и считываюсцих массивы данных в объеме одного кадра информации. Запись информации осуществляется следующим образом.

Информационные сигналы в виде многоканального цифрового потока от группы источников информации на информационный вход канала и через узел 44 подаются на вход узла 29. На другие входы узла 29 поступают с выходов узлов 32 и 33 элементов И соответственно код времени задержки и код текущего номера кадра с выходов счетчика 3 и счетчика 26 кадров. Код текущего номера кадра формируется счетчиком 26 путем подсчета первых синхросигналов, поступаемых через узел 45. Ввод кода текущего номера кадра в информационный поток осуществляется узлом 29 в момент поступления задержанного кадрового импульса с элемента 43 задержки, задержка в котором равна половине периода вторых синхроимпульсов. Ввод кода времени задержки осуществляется узлом 29 в момент поступлепил первого синхросигнала. Сформированный информационный поток с выхода узла 29 записывается в регистры 22 и 23, которые работают в так называемом режиме качелей : оба, работают в одном из двух режимов пока в одном накапливается информация, из другого уже накопленная информация передается в ВМ; затем режимы работы меняются на противоположные.

Первые синхросигналы, поступакнцие i на вход канала через узел 46, а также задержанные вторые синхросигналы с выхода элемента 43 задержки объединяются на элементе ИЛИ 36 и далее поступают на вход счетчика 27 адреса записи и входы элементов И-НЕ 41 и 42 Сигнал разрешения поступает на счетчик 27 адреса записи и снимает его блокировку по входу установки О. После этого счетчик 27 начинает формировать код адреса записи информации, который поступает с его выхода через узлы 34, 35, 30 и 31 на входы регистров 22 и 23. Управление р(;жима- ми записи и считывания осуществляется сигналами с триггера 25 переполнения, работающего в счетном режиме от сигналов переноса счетчика 27.

После записи массива информации;В объеме одного кадра триггер 25 закрывает входы узла 35 элемента И 39, элемента И-НЕ 42 и открывает входы узла 34, элемента И 38, элемента И-НЕ 41, обеспечивая тем самым перевод регистра 22 в режим записи путем подачи на него кода адреса записи и первых синхросигналов, а также подготавливая регистр 23 для режима считывания.Кроме того, сигнал переноса подается на триггер 24 готовности, который при его поступлении формирует сигнал го7 товности канала к выходу информации в ВМ, который поступает на элемент И 18, который при наличии yкaзaннi Ix сигналов формирует сигнал запроса ввода, поступающий через коммутатор 13 в ВМ. Ответом .ВМ на сигнал запроса ввода является сигнал разрешения ввода, поступающий на вход триггера 9 через .коммутатор 12. Триггер 9 формирует сигнал строба считывания, который с его выхода поступает на элемент И 17, разрешая прохождение через него импульсов считывания с генератора 1 импульсов на вход счетчика 4 адреса считывания. Сигнал строба счнтыва1П1я поступает в качестве управляющего сигнала также в ВМ через коммутатор 13.

Сигналы кода адреса считывания с выхода счетчика 4 адреса считывания в зависимости от состояния триггера 25 переполнения поступают через один из элементов И 38, 39 и один из узлов 30, 31 на вход того регистра 22 и 23, который работает в режиме считывания. Считываемая информация через коммутатор 40 поступает через узел 47 в ВМ. Кроме того, выход коммутатора. 40 соединен с входом сумматора 21 контрольных разрядов, контрольные разряды в котором вычисляются дополнением до нечетности передаваемых инфомационных сообщений. Сформированные контрольные разряды через узел 48 поступают в ВМ.

По окончании режима считывания счетчик 4 адреса считывания формирует сигнал переноса, который возвращает триггер 9 в исходное положение и снимает сигнал строба считывания. По заднему фронту указанного сигнала сбрасываются триггеры 24 готовности во всех каналах. Это в свою очередб, приводит к прекращению формирования сигнала запроса ввода на выходе элемента И 18. При прекращении сигнала с выхода элемента И 18 ВМ снимает сигнал разрешения ввода, и описанный процесс считывания и ввода информации в ВМ повторяется с момента формирования нав 1ходе; элемента И 18 очередного сигнала запроса ввода.

Устройство обладает возможностью по инициативе ВМ производить в каждом канале селетивную синхронизацию только части информации, вводимой в ВМ. Дпя этого используется счетчик 28 каналов, память 20, элемент И 37, узел 50. Управляющая информация, содержащая адреса каналов и признаки их передач, поступает от ВМ через узел 49 в память 20. При вводе информации в ВМ производится считывание признаков передачи каналов из памяти 20 по адресам, iiocTjojaronmM с выхода счетчика 28 каналов при наличии сигнала строба считывания. Формирование кода адреса осуществляется от сигналов тактовой частоты считывания, получаемых с .выхода элемента И 17. Считанные;с .выхода памяти 20 признаки передачи каналов стробируются на элементе И 37 сигналами тактовой частоты считыва1шя и через узел 50 вводятся в ВМ.

Ввод предложенным устройством в информационньм поток меток времени дает возможность производить в ВМ межканальную обработку (например,взаимнокорреляционную) информации от различных групп источников. Это снимает необходимость создания для ВМ, входящих в многомашинную вычислительную систему (ВС),системы единого времени, что позволит упростить программное обеспечение и уменьшить аппаратурные затраты на ВС с одновременным увеличением процента полезной вычислительной Нагрузки используемых ВМ.

При скорости поступления информации в каждый блок сопряжения порядка нескольких сотен слов/ с и при объеме кадра, равном 600-800 двухбайтовых слов, ввод предлагаемым устройством информации в ВМ в виде массивов данных объемом, равным одному или нескольким кадрам, позволит уменьшить загрузку каналов ввода-вывода в селекторном режиме не менее, чем на 70% (по сравнению с пословным режимом ввода устройства-прототипа).

Таким образом, введение в многоканальное устройство для сопряжения с цифровой вычислетельной машиной дополнительных блоков и системных свзей повьш1ает эффективность использовния ВМ за счет уменьшения времени, необходимого для осуществления oneрации ввода информации.

Использование предложенного устройства совместно с экспедиционным геофизическим вычислительным комплексом (ЭГВК) ЛС-2000 дает возможность вводить в этот комплекс информацию по каналам прямого доступа в память, а не через его мониторную подсистему, что позволит высвободить для внутрисистемных обменов время работы каналов ввода-вывода вычислительных комплексов СМ-2, используемых в качестве мониторньпс подсистем ЦС-2000. Кроме того, наличие меток времени, поступающих вместе с информацией в ПС-2000, дает возможность производить межканальную обработку сигналов без применения специальной аппаратуры синхронизации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство связи для вычислительной системы | 1980 |

|

SU943695A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-30—Публикация

1983-11-14—Подача