(21)4236709/24-24

(22)29.04.87

(46) 15.11.88, Бюл. № 42

(72) С.В.Афанасьев, И.Е.Алимов,

А.П.Иванов и Л.Т.Кирьяк

(53) 681,327.6 (088.8)

(56)Авторское свидетельство СССР W 612287, кл, G 11 С 29/00, 1975,

Авторское свидетельство СССР № 1084901, кп. G 11 С 29/00, 1981.

.(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ .

(57)Изобретение относится к вычислительной технике и может быть использовано для контроля запоминанлцих устройств. Цель изобретения - повышение

достоверности контроля. Устройство содержит генератор 1 тактовых импульсов, делитель 2 частоты, расширитель 3 импульсов, элементы 4,10,16 задержки, элементы 5,14,15 И, адресный счетчик 6, формирователь 7 импульсов чтения, проверяемый блок 8 памяти, генератор 9 псевдослучайной последова . тельности, кольцевой регистр 11 сдвига, накапливающий сумматор 14, блок сравнения, триггер 17, элемент 18 индикации. В устройстве обеспечивается автоматическое изменение числа сдвигов, а также повьппается уровень достоверности контроля за счет назначения числа сдвигов случайным образом. 5 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1981 |

|

SU1084901A1 |

| Устройство для формирования тестов | 1984 |

|

SU1226472A1 |

| Генератор псевдослучайной последовательности | 1985 |

|

SU1305837A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| Устройство поиска псевдослучайных последовательностей | 1981 |

|

SU1042199A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих уст - ройств.

Цель изобратени я - повьштение достоверности контроля,

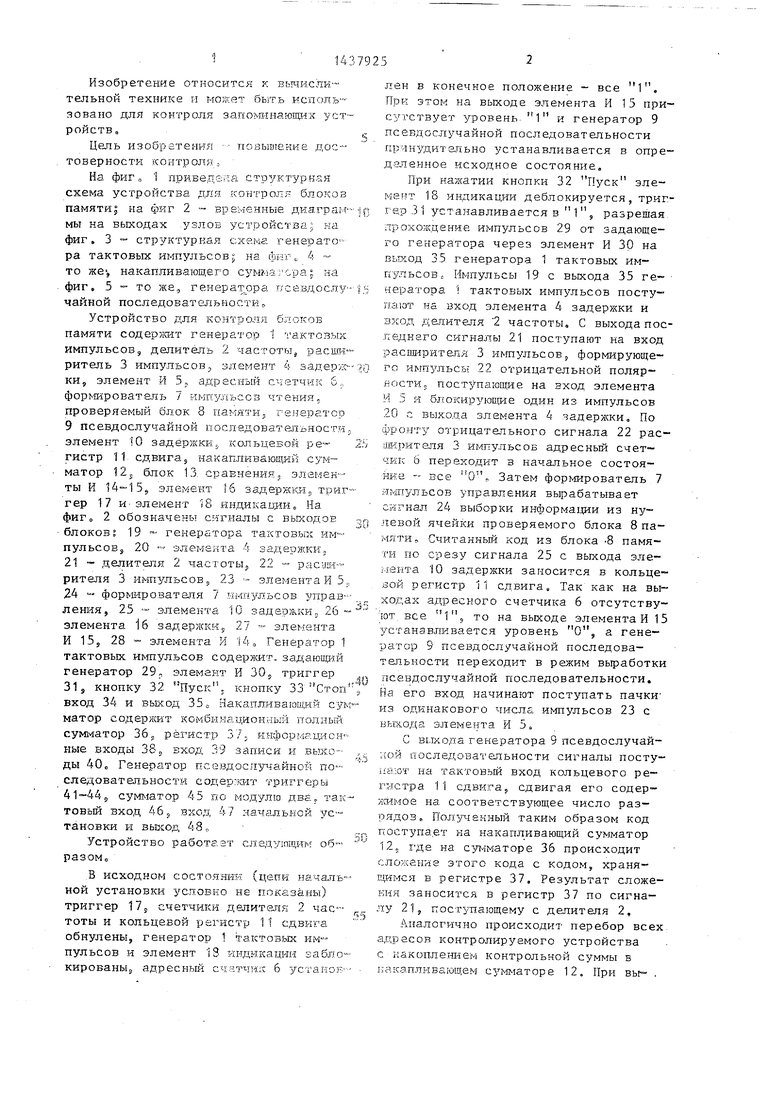

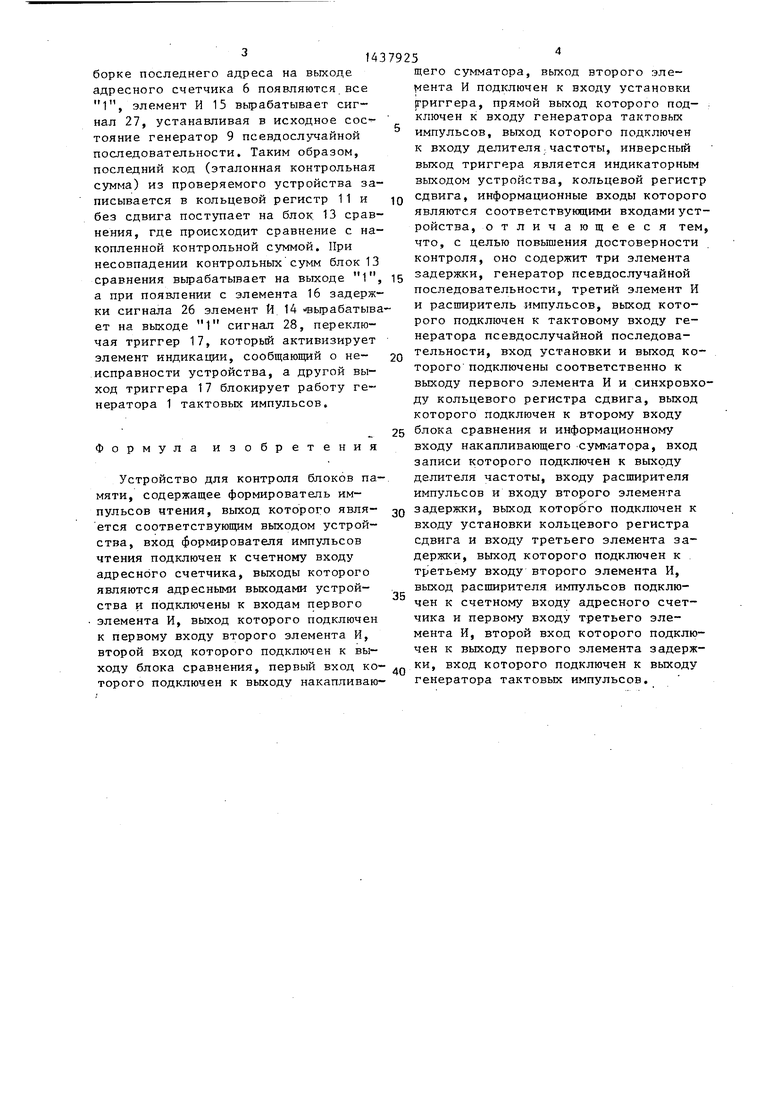

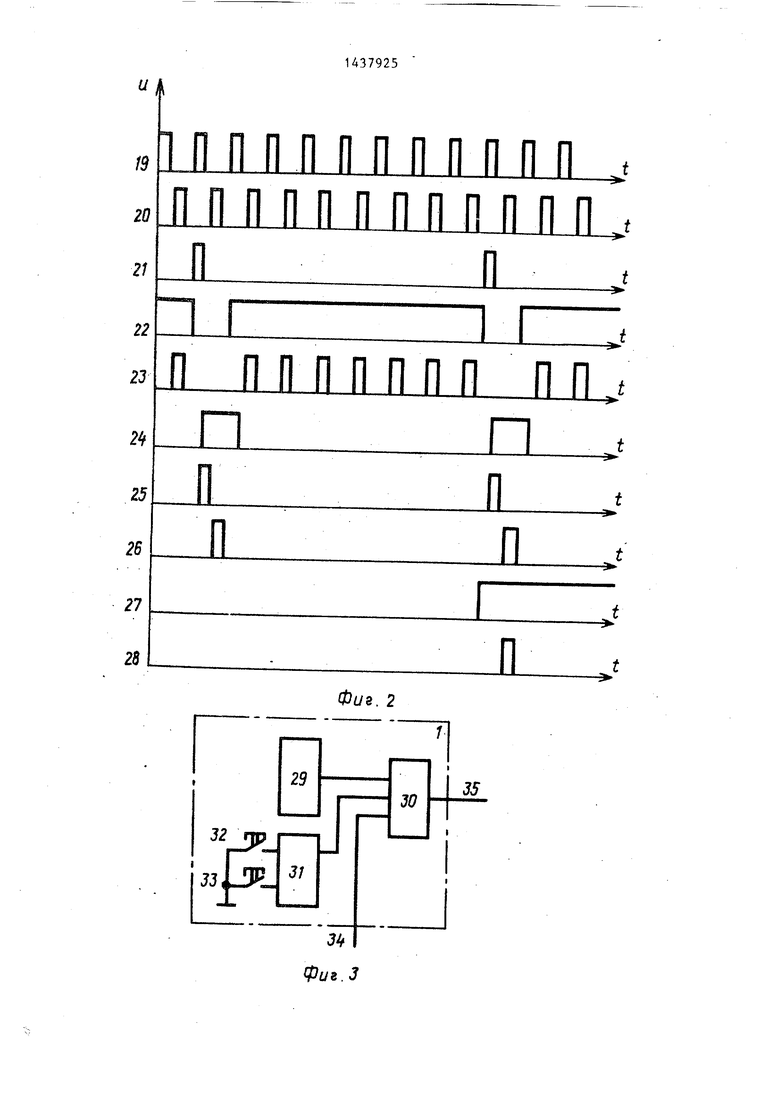

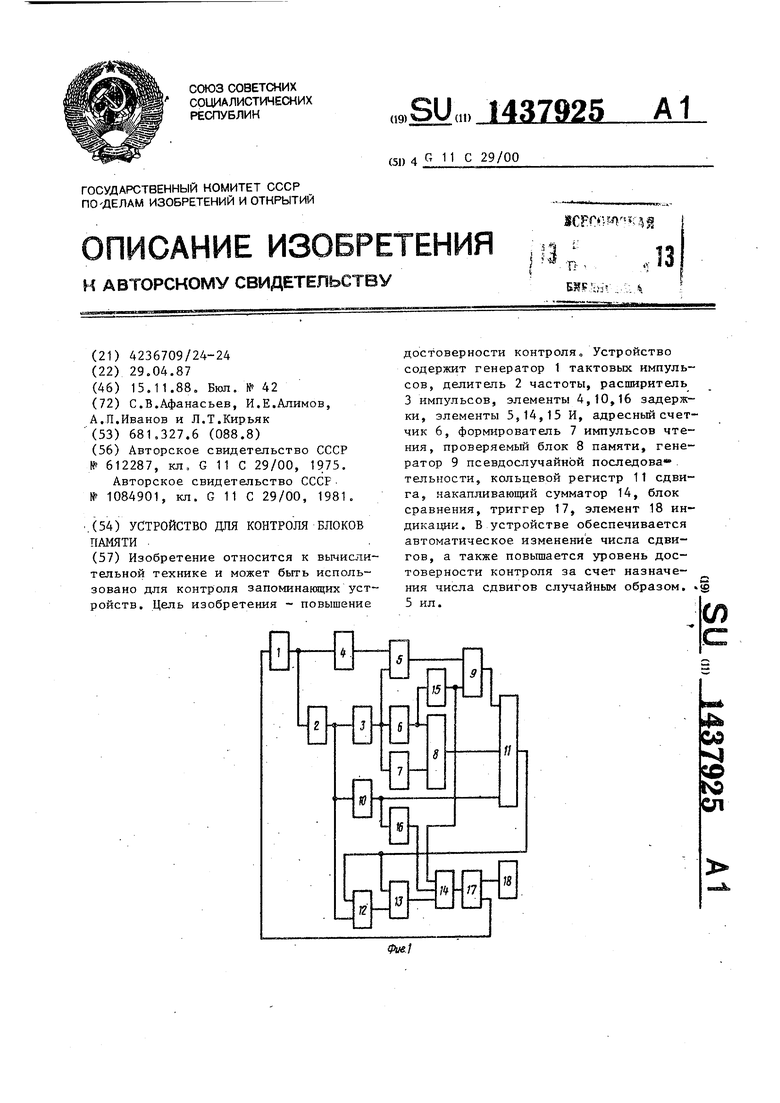

На фиг,, 1 приведена структ -урная схема устройства для контроля блоков памяти| на фиг 2 - временные диаграм мы на выходах узлов устройства; ка фиг, 3 - структурная схема генератора тактовых импульсовJ на фиг„ 4 - то же, накапливающего суымагс ра; на фиг, 5 - то же, генерат ора псевдослучайной последовательности,

Устройство для контроля блоков памяти содергкит генератор 1 актовых импульсов, делитель 2 частоты,, расширитель 3 импульсов, элемент 4 задержкн, элемент И 5, адресный счетчик б„ ф о р ми р о в а т ел ь 7 и мп ул ь с с з ч т е н и я, проверяемый блок 8 пакяти:, генератор 9 псевдослучайной последовательности; элемент 10 задёржкК;, кольцевой ре- гистр 11 сдвига5 накаплрхвающий сумматор IZj блок 13, сравнения, эленен-- ты И 14-155 элемент 16 задержки,, триггер 17 и-элемент 18 индикапт Ио На фиг о 2 обозначены с 1гналы с ВЬЕХОДОЕ блоков г 19 генератора тактовых им- nynbcoBj 20 - элемента 4 задержки, 21 делителя 2 частоты,, 22 -- рас1Ш рителя 3 имтхульсов 23 - элемента И 5, 24 ,вaтaпя 7 импульсов управления, 25 - элемента 10 задержки„ 26элемента 16 задерлскк 27 - элемента И 15s 28 - элемента И 14 Генератор 1 тактовых импульсов содержит, задающий генератор 29.. элемент И 30,, триггер 315 кнопку 32 кнопку 33 Стоп вход 34 и вькод 35о Накапливающий сумматор содеряш т комбина,цион,аый полный cyMiviaTOp 365 регистр 37; инфор /1ащ1СН ныв входы 385 вход 39 записи и выходы 40с Генератор псевдослучайной по- сле;довательности содергкит триггеры 41-44, сумзматор 45 по модулю два, так тов,&1й вход 46 J вход 47 начальной установки и вьпсод 48,,

Устройство работаэт следующим об- разомо

В исходном состо.яш Ш (цепи начальной установки условно не показаны) триггер 17; счетчики делителя 2 частоты и кольцевой регистр

сдвига

обнулены, генератор 1 тактовых импульсов и элемент 13 индикации забх(0- кированы адреснглй счатчи;: 6 з С1 аиоН

лен в конечное положение - все 1 , При этом на выходе элемента И 15 присутствует уровень 1 и генератор 9 псевдо г,лучайной последовательности принудительно устанавлршается в определенное исходное состояние.

При нажатии кнопки 32 Пуск элемент 18 индикации деблокируется, триггер 31 устанавливается в 1, разрешая прохож,цение импульсов 29 от задающего генератора через элемент И 30 на вьпсод 35 генератора 1 тактовых импульсов. Импульсы 19 с выхода 35 генератора

тактовых импульсов поступают на вход элемента 4 задержки и вход делителя 2 частоты С выхода пос ,п:еднего сигналы 21 поступают на вход расширитепя 3 иьшульсов, формирующего имп ульс&г 22 отрицательной поляр- ,ности,; поступающие на вход элемента М 5 я блокирз ющие один из импульсов 20 с выхо,аа элемента 4 задержки. По фронту отрицательного сигнала 22 рас- ,-лирителя 3 импульсов адресный счет- чкк 6 переходит в начальное состояние - ,тзсе О., Затем формирователь 7 ,ямпульсов управления вырабатывает сигнал 24 выборки информации из нулевой ячейки проверяемого блока 8 памяти, Считанный код из блока В памя- | и по срезу сигнала 25 с выхода элемента 10 задержки заносится в кольце- ,бой регистр 11 сдвига. Так как на выходах адресного счетчика 6 отсутствуют все r j то на выходе элементам 15 устанавливается уровень О, а генератор 9 псевдослучайной последовательности переходит в режим выработки псевдослучайной последовательности. На его вход начинают поступать пачки из одинакового числа импульсов 23 с выхода злемен та И 5«

С выхода генератора 9 псевдослучай- ;1:ой последовательности сигналы поступают на тактовый вход кольцевого регистра 11 сдвига сдвигая его содер- ясимое на соответствующее число разрядов, Пол5 1екный таким образом код поступает на накапливающий сумматор 12 г де на сумматоре 36 происходит сложение этого кода с кодом, храня- гдимся в регистре 37, Результат сложения заносится в регистр 37 по сигналу 21, постчшающему с делителя 2,

,fVHanorH4HO происходит перебор всех адресов контролируемого устройства с какоплегжем контрольной суммы в накапливающем cjj MMaTOpe 12, При вы™ .

борке последнего адреса на выходе адресного счетчика 6 появляются все 1, элемент И 15 вырабатывает сигнал 27, устанавливая в исходное сос- тояние генератор 9 псевдослучайной последовательности. Таким образом, последний код (эталонная контрольная сумма) из проверяемого устройства записывается в кольцевой регистр 1 1 и без сдвига поступает на блок. 13 сравнения, где происходит сравнение с накопленной контрольной суммой. При несовпадении контрольных сумм блок 13 сравнения вырабатывает на выходе 1, а при появлении с элемента 16 задержки сигнала 26 элемент И 14 -вьфабатыва ет на выходе 1 сигнал 28, переключая триггер 17, которьш активизирует элемент индикации, сообщающий о неисправности устройства, а другой выход триггера 17 блокирует работу генератора 1 тактовых импульсов.

Формула изобретения

Устройство для контроля блоков памяти, содержащее формирователь импульсов чтения, выход которого является соответствуюпщм выходом устройства, вход формирователя импульсов чтения подключен к счетному входу адресного счетчика, вькоды которого являются адресными выходами устройства и подключены к входам первого элемента И, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к выходу блока сравнения, первый вход которого подключен к выходу накапливаю-

5

щего сумматора, выход второго эле- 4ента И подключен к входу установки триггера, прямой выход которого под- . ключен к входу генератора тактовых

импульсов, выход которого подключен к входу делителя частоты, инверсный выход триггера является индикаторным выходом устройства, кольцевой регистр

сдвига, информационные входы которого являются соответствующими входами устройства, отличающееся тем, что, с целью повышения достоверности контроля, оно содержит три элемента

задержки, генератор псевдослучайной последовательности, третий элемент И и расщиритель импульсов, выход которого подключен к тактовому входу генератора псевдослучайной последовательности, вход установки и выход которого подключены соответственно к выходу первого элемента И и синхровхо- ду кольцевого регистра сдвига, выход которого подключен к второму входу

блока сравнения и информационному входу накапливающего сумматора, вход записи которого подключен к выходу делителя частоты, входу расширителя импульсов и входу второго элемента

задержки, выход которого подключен к входу установки кольцевого регистра сдвига и входу третьего элемента задержки, выход которого подключен к третьему входу второго элемента И, выход расширителя импульсов подключен к счетному входу адресного счетчика и первому входу третьего элемента И, второй вход которого подключен к выходу первого элемента задержки, вход которого подключен к выходу генератора тактовых импульсов.

ПППП on п п

пп п пп п пп п п п п

п

пп п п ппп п п

п

п

п

п

л

29

J2

JP

.

jj,JPL

J4- Фиъ.З

, 2

J

J5

фиг. 4

Фив. 5

Авторы

Даты

1988-11-15—Публикация

1987-04-29—Подача