Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих устройств.

Известно устройство для контроля блоков памяти, содержащее регистр, накапливающий сумматор, адресный счетчик, регистр константы и блок сравнения. Контроль блока памяти осуществляется путем суммирования информации и сравнения полученной суммы с заданной константой 1.

Недостатком данного устройства является низкая точность контроля.

Наиболее близким по .технической сущности к изобретению является устройство для контроля блоков памяти, содержащее сдвиговый регистр, вы- ходы которого подключены к информационным входам сумматора, выходы и управляющие входы сумматора подключены к соответствующим входам и выходам блока управления, адресный дешифратор, информационные входы которого подключены к соответствующим выходам адресного счетчику, управляющий выход адресного счетчика подключен к соответствующему входу блока управления и блока задания циклов суммирования, управляющие входы адресного девтфратора и адресного счетчика подключены к со.ответствующим выходам блока управления, выходы и входы блока задания циклов суммирования подключены к соответствующим входам и выходам блока управления. Блок управления и блок задания циклов суммирования содержат генератор тактовых импульсов, делители частоты,,формирователи временной диаграммы работы устройства, регистры, триггеры и логические элементь С2

Недостатками известного устройства являются низкое быстродействие, связанное с необходимостью осуществления нескольких циклов контрольного суммирования содержимого блока памяти, а также его сложность.

Цель изобретения - повьшение бь1стродействия и упрощение его схемы.

Поставленная цель достигается тем,что в устройстве для контроля блоков памяти, содержащем адресный счетчик, выходы которого являются соответствующими выходами устройства первый сдвиговый регистр, установочные входы которого являются одними входами устройства и подключены к

одним из входов блока .сравнения, выход первого сдвигового регистра подключен к одному из входов блока элементов И, выходы которого подключены к входам сумматора, выходы (Сумматора подключень к другим входам блока сравнения, второй сдвиговый регистр, генератор тактовых импульсов, делитель частоты триггеры и

o элементы И, выход генератора тактовых импульсов подключен к входу делителя частоты и к первым входам первого и второго элементов И, выход делителя частоты подключен к счетному входу

5 Первого триггера и к первым входам третьего и четвертого элементов И, первый выход .первого триггера подключен к вторым входам первого и третьего элементов И, выход первого

0 элемента И подключен к тактовому входу второго сдвигового регистра, установочные входы которого являются другими входами устройства, выход второго сдвигового регистра подклю5 чен к второму входу второго элемента И, выход которого подключен к тактовому входу первого сдвигового регистра; второй выход первого триггера подключен к второму входу четвер0 тога элемента И, выход которого подключен к входу адресного счетчика и является соответствующим управляющим выходом устройства, выходы адресного счетчика подключены к входам пятого

5 элемента И, выход которого подключен к первому входу шестого элемента И; установочный вход второго триггера подключен к выходу шестого элемента К, второй вход которого подключен к вы0 ходу блока сравнения, вход генератора тактовых импульсов подключен к первому выходу второго триггера; второй выход которого является соответствующим управляюким выходок уст5 ройства.

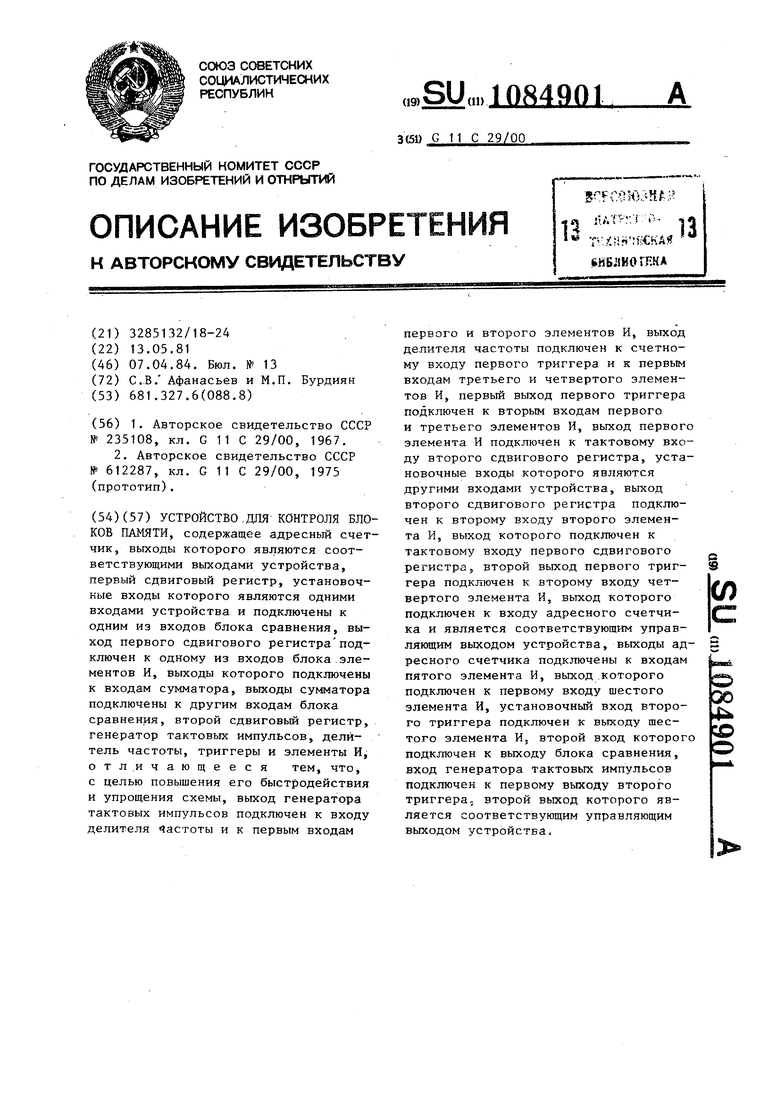

На фиг, 1 приведена структурная схема устройства для контроля блоков памяти; на фиг, 2 - временные диаграммы сигналов на выходах некс орьпс узлов устройс.тва; на фихч 3 - структурные схе.. ; генератора тактовых импульсов и цепей начальной устаноэки устройстввд на фиг, 4 - структурная схема блока начальной установки,

Устройство для контроля блоков памяти содерж гт генератор 1 тактовых импульсовJ,- делитель 2 частоты триггер 3f злементы И 4-7, сдвиго ый I регистр 8, блок 9 начальной установки, формирователь 10 импульсов управления, адресный счетчик 11, блок 12 памяти, сдвиговьш регистр 13, блок 14 элементов И, сумматор 15, блок 16 14 элементов И, сумматор ID, олог 1внения. элементы И 17 и 18. тригсравнения, элементы И 17 и 18, тт сравнения, элемен1ы и i/ и lo, триггер 19, элемент 20 индикации, вьп гер 19, элемент 20 индикации, выход 21 генератора тактовых: импульсов, выход 22 делителя частоты, выходы 23 и 24 триггера 3, выход 25 элемента И 5, выход 26 элемента И 6, выход 27 элемента И 4, выход 28 сдвигового регистра 8, выход 29 элемента И 7 1задающий генератор 30, элемент И 31, генератор 32, триггер 33, кнопку 34 Пуск, кнопку 35 Стоп, вход 36 генератора 1, выход 37 генератора 32 элемент 38 задержки, цепь 39 на вход тактового регистра 8, цепь 40 на вход режима регистра 8, шину 41 логи ческого нуля, элемент НЕ 42, шину 43 логической единицы, выходы 44 блока начальной установки. Устройство работает следующим образом. При нажатии кнопки Пуск триггер 33 переводится в единичное состояние при этом на тактовый вход кольцевого сдвигового регистра 8 поступает отрицательный перепад (из 1 в О) напряжения, а на входе режима регист ра 8 в это время еще присутствует уровень I, соответствующий режиму записи. При этом в него заносится код 111001100010 из блока 9 начальной установки. Через интервал времен определяемый элементом 38 задержки, на входе режима регистра 8 устанавли вается уровень О, соответствующий режиму сдвига. Одновременно I на единичном выходе Р-триггера 33 посту пает на вход элемента И 31. На выходе 21 генератора 1 тактовых импульсов появляются импульсы, поступающие на входы делителя 2 частоты и элемен тов И 4 и 7. На выходе 22 делителя 2 появляются импульсы, которые поступают на вход Т-триггера 3 и первые входы элементов И 5 и 6. На выходах 25 и 26 элементов И 5 и 6 появляются импульсы (фиг. 2). По первому сигналу с выхода элемента И 6 в адресный счетчик 11 заносится единица и формируется импульс управления на выходе формирователя 10, При этом информация из первой ячейки проверяемого блока 12 памяти записывается в кольцевой сдвиговый регистр 13. На выхо101 де 27 элемента И 4 появляется серия импульсов, поступающих на вход сдвига кольцевого сдвигового регистра 8, и информация в нем сдвигается на число разрядов, соответствующее числу, импульсов в серии на входе сдвига. На выходе старшего разряда регистра 8 единица появляется при сдвиге только один раз, что обуслбвлено записанным ранее кодом. Поэтому на выходе элемента И 7 появляется только один импульс, который сдвигает содержимое регистра 13 на один разряд. После прихода импульса с элемента И 5.сдвинутая информация через блок 14 элементов И поступает в накапливающий сумматор 15. Второй 1-1Мпульс с выхода элемента И 6 вновь поступает в счетчик 11, формируется импульс обращения к блоку 12, ив регистр 13 записывается информация из второй ячейки блока памяти. Вновь импульсы с выхода 27 элемента И 4 сдвигают содержимое регистра 8 и на выходе его старшего разряда появляется I за время сдвига уже дважды, что также обусловлено записанной ранее кодовой комбинацией. На выходе элемента К 7 появляются два импульса, и информация в регистре 13 сдвигается на два разряда. По сигналу с выхода элемента И 5 через блок 14 элементов И информация поступает на сумматор 15, где суммируется с его содержимым. Далее аналогичным образом информация из третьей ячейки памяти блока 12 сзтмируется с содержимым сумматора 15, предварительно сдвинувшись на три разряда, и т.д. Таким образом происходит последовательное чтение информации из проверяемого блока памяти, сдвиг ее на кольцевом регистре 13 и суммирование на сумматоре 15. Сдвиг информации идет по кольцу, т.е. из младших разрядов в старшие, а из самого старшего - в самьш младшрй. Выходы сумматора 15 подключены к входам блок 16 сравнения, другие входь которого подключены к выходам проверяемого блока памяти. По последнему адресу на выходе элемента И 17 появляется I. Если содержимое последней ячейки проверяемого блока памяти равнр содержимому сумматора, на выходе блока 16 сравнения будет О, и триггер 19 остается в нулевом состоянии. В последней

ячейке блока памяти должна храниться контрольная сумма, полученная с учетом выбранной последовательности сдвига считываемой информации. В случае неисправности блока 12 на выходе блока 16 сравнения в момент появления последнего адреса триггер 19 устанавливается в состояние I и срабатывает элемент индикации. Одновременно происходит остановка генератора.М .

Предлагаемое устройство наиболее эффективно при контроле постоянных

запоминающий устройств, контроль адресной Macrtf которых в динамическом режиме представляет трудности. При этом обеспечивается высокое быстродействие, так как для осуществления контроля достаточно проведения одного цикла суммирования. Кроме того, предложенное техническое решение проще известного, поскольку в нем отсутствует блок задания циклов суммирования, и имеет меньшие аппаратурные затраты для обеспечения временной диаграммы работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для вычисления скользящего среднего | 1986 |

|

SU1410058A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Цифровой фильтр | 1983 |

|

SU1249536A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для селекции изображений объектов | 1989 |

|

SU1777651A3 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

УСТРОЙСТВО,ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ, содержащее адресный счетчик, выходы которого являются соответствующими выходами устройства, первый сдвиговый регистр, установочные входы которого являются одними входами устройства и подключены к одним из входов блока сравнения, выход первого сдвигового регистраподключен к одному из входов блока элементов И, выходы которого подключены к входам сумматора, выходы сумматора подключены к другим входам блока сравнения, второй сдвиговый регистр, генератор тактовых импульсов, делитель частоты, триггеры и элементы И, отл.и чающееся тем, что, с целью повышения его быстродействия и упрощения схемы, выход генератора тактовых импульсов подключен к входу делителя «Частоты и к первым входам первого и второго элементов И, выход делителя частоты подключен к счетному входу первого триггера и к первым входам третьего и четвертого элементов И, первый выход первого триггера подключен к вторым входам первого и третьего элементов И, выход первого элемента И подключен к тактовому входу второго сдвигового регистра, установочные входы которого являются другими входами устройства, выход второго сдвигового регистра подключен к второму входу второго элемента И, выход которого подключен к тактовому входу первого сдвигового i регистра, второй выход первого триггера подключен к второму входу вертого элемента И, выход которого сг подключен к входу адресного счетчика и является соответствующим управляющим выходом устройства, выходы адресного счетчика подключены к входам пятого элемента И, выход которого подключен к первому входу шестого 30 элемента И, установочный вход второ4 21. го триггера подключен к выходу шессо того элемента И, второй вход которого подключен к выходу блока сравнения, вход генератора тактовых импульсов подключен к первому выходу второго триггера, второй выход которого является соответствующим управляющим выходом устройства.

22

6

м

21

1

17

8

r-LHU

PD

25

17

L

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПОСТОЯННОЙ ПАМЯТИ | 0 |

|

SU235108A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля блоков постоянной памяти | 1975 |

|

SU612287A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-07—Публикация

1981-05-13—Подача