4:

СО 00 О О СО

Изобретение относится к вычислительной технике и может быть использовано при построении имитирующе-мо- делирующей аппаратуры для тренажеров испытательных стендов, автоматизированных систем моделирования и испытаний радиоэлектронной аппаратуры,,

Цель изоб15етения - повышение точности формирования временного интервала.

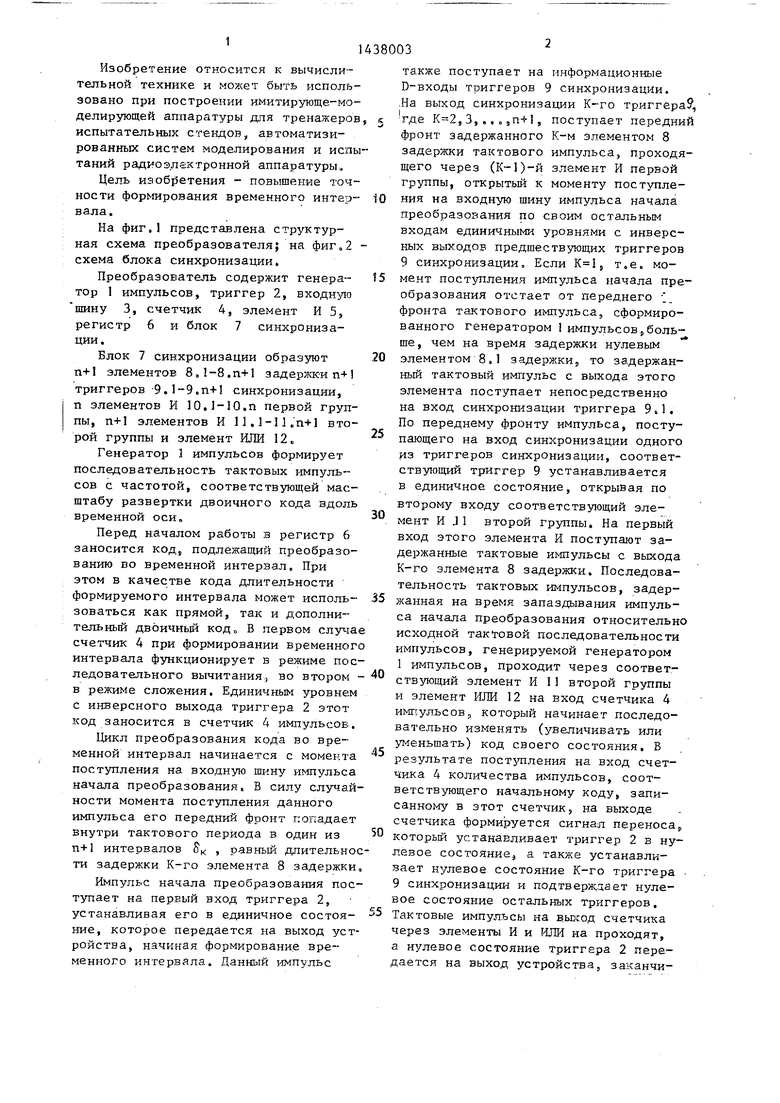

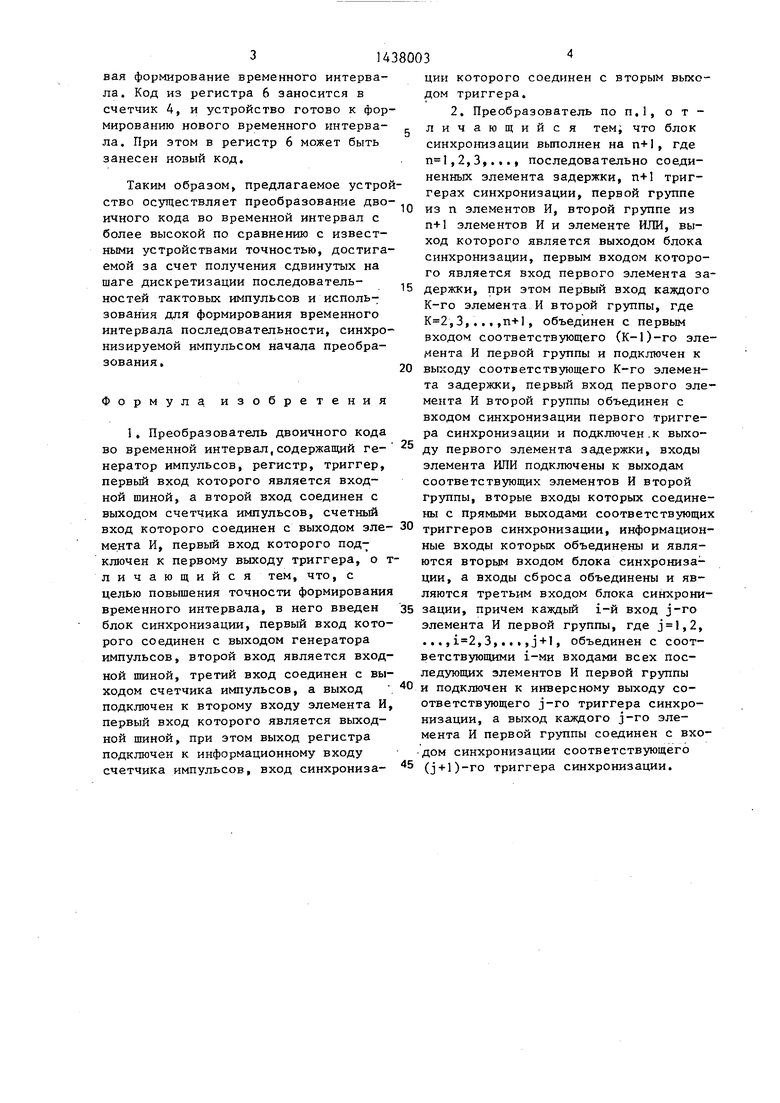

На фиг,1 представлена структурная схема преобразователя; на фиг,.2 схема блока синхронизации.

Преобразователь содержит генера-- тор 1 импульсов, триггер 2, входную шину 3, счетчик 4, элемент И 5, регистр 6 и блок 7 синхронизации.

Блок 7 синхронизации образуют п+1 элементов 8,1-8.п+1 задержки п+ триггеров 9.1-9.П+ синхронизации, п элементов И 10,1-lO.n первой группы, п+1 элементов И П.) второй группы и элемент ИЛИ 12.

Генератор 3 импульсов формирует последовательность тактовых импульсов с частотой, соответствующей масштабу развертки двоичного кода вдоль временной оси„

Перед началом работы в регистр 6 заносится код подлежащий преобразованию во временной интервал. При этом в качестве кода длительности формируемого интервала может использоваться как прямой, так и дополни- тельньй двоичный код„ В первом случа счетчик 4 при формировании временног интервала функционирует в режиме последовательного вычитания, во втором в режиме сложения. Единичным уровнем с инверсного выхода триггера 2 этот код заносится в счетчик 4 импульсоЕ;. 11ИКЛ преобразования кода во временной интервал начинается с момента поступления на входную шину импульса начала преобразования. В силу случайности Момента поступления данного импульса его передний фронт попадает внутри тактового периода в один из п+1 интервалов 5к , равный длительноти задержки К-го элемента 8 задержки Импульс начала преобразования поступает на первый вход триггера 2, устанавливая его в единичное состоя ние, которое передается на выход устройства, начиная формирование временного интервала. Данный импульс

,

10

fS

25

s

40с. 55

также поступает на информационные D-входы триггеров 9 синхронизации. ,На выход синхронизации К-го триггера, где , 3, ., „ jO-i-i, поступает передний фронт задержанного К-м элементом 8 задержки тактового импульса, проходящего через (К-1)-й элемент И первой группы, открытьш к моменту поступления на входную шину импульса начала преобразования по своим остальным входам единичными уровнями с инверсных выходов предшествующих триггеров 9 синхронизации. Если т.е. момент поступления импульса начала преобразования отстает от переднего фронта тактового импульса, сформированного генератором 1 импульсовjбольше, чем на время задержки нулевым 20 элементом 8,1 задержки, то задержанный тактовый импульс с выхода этого элемента поступает непосредственно на вход синхронизации триггера 9.1. По переднему фронту импульса, поступающего на вход синхронизации одного из триггеров синхронизации, соответствующий триггер 9 устанавливается в единичное состояние, открывая по второму входу соответствующий элемент И J1 второй группы. На первый вход этого элемента И поступают за- держаннь е тактовые импульсы с выхода К-го элемента 8 задержки. Последовательность тактовых импульсов, задержанная на время запаздывания импульса начала преобразования относительно исходной тактовой последовательности импульсов, генерируемой генератором 1 импульсов, проходит через соответствующий элемент И 11 второй группы и элемент ИЛИ 12 на вход счетчика 4 импульсов, который начинает последовательно изменять (увеличивать или уменьшать) код своего состояния. В результате пост шления на вход счетчика 4 количества импульсов, соответствующего начальному коду, записанному в этот счетчик, на выходе счетчика формируется сигнал переносар которьЕй устанавливает триггер 2 в нулевое состояниез а также устанавливает нулевое состояние К-го триггера 9 синхронизации и подтверждает нулевое состояние остальных триггеров. Тактовые импульсы на выход счетчика через элементы И и Г1ПИ на проходят, а нулевое состояние триггера 2 передается на выход устройства, заканчи30

35

45

50

31438003

ирование временного интерваиз регистра 6 заносится в 4, и устройство готово к форю нового Временного интерваэтом в регистр 6 может быть новый код.

в т м вх д эл со Гр ны

Таким образом, предлагаемое устройство осуществляет преобразование двоичного кода во временной интервал с более высокой по сравнению с известными устройствами точностью, достигаемой за счет получения сдвинутых на шаге дискретизации последовательностей тактовых импульсов и использования для формирования временного интервала последовательности, синхронизируемой импульсом начала преобразования ,

25

Формула изобретения

1, Преобразователь двоичного кода во временной интервал,содержащий генератор импульсов, регистр, триггер, первьй вход которого является входной шиной, а второй вход соединен с выходом счетчика импульсов, счетный вход которого соединен с выходом зле- 30 триггеров синхронизации, информацион2. Преобразователь по п.1, о т - личающийся тем; что блок синхрО1шзации выполнен на п+1, где ,2,3,.,., последовательно соединенных злемента задержки, п+1 триггерах синхронизации, первой группе из п злементов И, второй группе из п+ элементов И и элементе ИЛИ, выход которого является выходом блока синхронизации, первым входом которого является вход первого злемента задержки, при этом первый вход каящого К-го элемента И второй группы, где ,3,..,,п+1, объединен с первым входом соответствующего (К-1)-го зле- нента И первой группы и подключен к выходу соответствующего К-го элемента задержки, первый вход первого злемента И второй группы объединен с входом синхронизации первого триггера синхронизации и подключен ,к выходу первого элемента задержки, входы элемента ИЛИ подключены к выходам соответствующих элементов И второй Группы, вторые входы которых соединены с прямыми вькодами соответствующих

0

5

0

5

0 триггеров синхронизации, информационции которого соединен с вторым выходом триггера.

2. Преобразователь по п.1, о т - личающийся тем; что блок синхрО1шзации выполнен на п+1, где ,2,3,.,., последовательно соединенных злемента задержки, п+1 триггерах синхронизации, первой группе из п злементов И, второй группе из п+ элементов И и элементе ИЛИ, выход которого является выходом блока синхронизации, первым входом которого является вход первого злемента задержки, при этом первый вход каящого К-го элемента И второй группы, где ,3,..,,п+1, объединен с первым входом соответствующего (К-1)-го зле- нента И первой группы и подключен к выходу соответствующего К-го элемента задержки, первый вход первого злемента И второй группы объединен с входом синхронизации первого триггера синхронизации и подключен ,к выходу первого элемента задержки, входы элемента ИЛИ подключены к выходам соответствующих элементов И второй Группы, вторые входы которых соединены с прямыми вькодами соответствующих

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Преобразователь двоичного кода во временной интервал | 1990 |

|

SU1714811A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1223248A1 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Преобразователь двоичного кода во временной интервал | 1983 |

|

SU1115223A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

Изобретение относится к вычислительной технике и может использоваться при построении имитирующе-модели- рующей аппаратуры для тренажеров, испытательных стендов, автоматизированных моделирующих комплексов.Целью изобретения является повьшение точ- ности формирования временного интервала. Преобразователь осуществляет преобразование код-временной интервал без погрешности, вызванной асинхронностью тактовых импульсов устройства относительно сигналов управления. Отличительным признаком преобра.зователя является введение в схему, содержащую генератор импуль- ;- сов, триггер, регистр, счетчик и элемент И, блока синхронизации, выполненного на элементах задержки, триггерах синхронизации, двух групп элементов И и элемента ИЛИ. Работа пре- с образователя заключается в формирова- НИИ сдвинутых тактовых последователь- ff ностей, автоматическом выделении из них последовательности, синхронизируемой внешним сигналом, и использовании ее для преобразования. 1 з.п. ф-лы, 2 ил.

мента И, первый вход которого подключен к первому выходу триггера, о т личающийся тем, что, с целью повьппения точности формирования временного интервала, в него введен блок синхронизации, первый вход которого соединен с выходом генератора импульсов, второй вход является входной шиной, третий вход соединен с выходом счетчика импульсов, а выход подключен к второму входу элемента И, первый вход которого является выходной шиной, при этом выход регистра подключен к информационному входу

счетчика импульсов, вход синхрониза

35

40

45

ные входы которьк объединены и являются вторым входом блока синхронизации, а входы сброса объединены и являются третьим входом блока синхронизации, причем каждый i-й вход j-ro элемента И первой группы, где ,2, ...,,3,.t,,j+1, объединен с соответствующими i-MH входами всех последующих элементов И первой группы и подключен к инверсному выходу соответствующего j-ro триггера синхронизации, а выход каждого j-ro элемента И первой группы соединен с вхо- -дом синхронизации соответствующего (j+l)-ro триггера синхронизации.

Фиг.2.

т

Авторы

Даты

1988-11-15—Публикация

1986-10-08—Подача