/.

со

CD СП 00

о:

| название | год | авторы | номер документа |

|---|---|---|---|

| Однородный спектрокоррелометр | 1983 |

|

SU1219977A1 |

| Частотно-импульсное множительно-дЕлиТЕльНОЕ уСТРОйСТВО | 1979 |

|

SU813426A1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Частотное множительно-делительное устройство | 1986 |

|

SU1312571A1 |

| Устройство для интегрирования частотно-импульсных сигналов | 1974 |

|

SU615496A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| Функциональный преобразователь | 1986 |

|

SU1456951A1 |

| Частотно-импульсное множительно-делительное устройство | 1983 |

|

SU1112364A1 |

| Частотно-импульсное множительноделительное устройство | 1975 |

|

SU596944A1 |

| Устройство для программного регулирования | 1988 |

|

SU1674086A1 |

Изобретение относится к вычислительной технике н может быть использовано при построении автоматизированных систем управления различными технологическими процесс мИо Цепь изобретения - повьшение точности перемножения частот. Устройство содер- лсит множительно-делительные блоки 1, 6, 11 с соответствующими информационными входам и выходами и функциональными связями, В устройстве период Т определяет интервал осреднения, и хотя увеличение этого интервала приводит к необходимости увеличения емкости счетчиков множительно-дели- тельных блоков, тем не менее повышается точность перемножения при некратных частотах F,, F и F, а также при нестабильности частот Е и F Вькодная импульсная последовательность оказывается нечувствительной к нестабильности входных частот,-ТоКо устройства осуществляет троекратное усреднение их на интервале времени Т„ путем накопления общего числа импульсов в счетчиках множительно-делитель- ных блоков о 2 ил. (Л с

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано при построе Ши автоматизиро - ванных систем управления различньиуш технааогическими процессами

Цепь изобретения - повьшюние точности перемножения частот

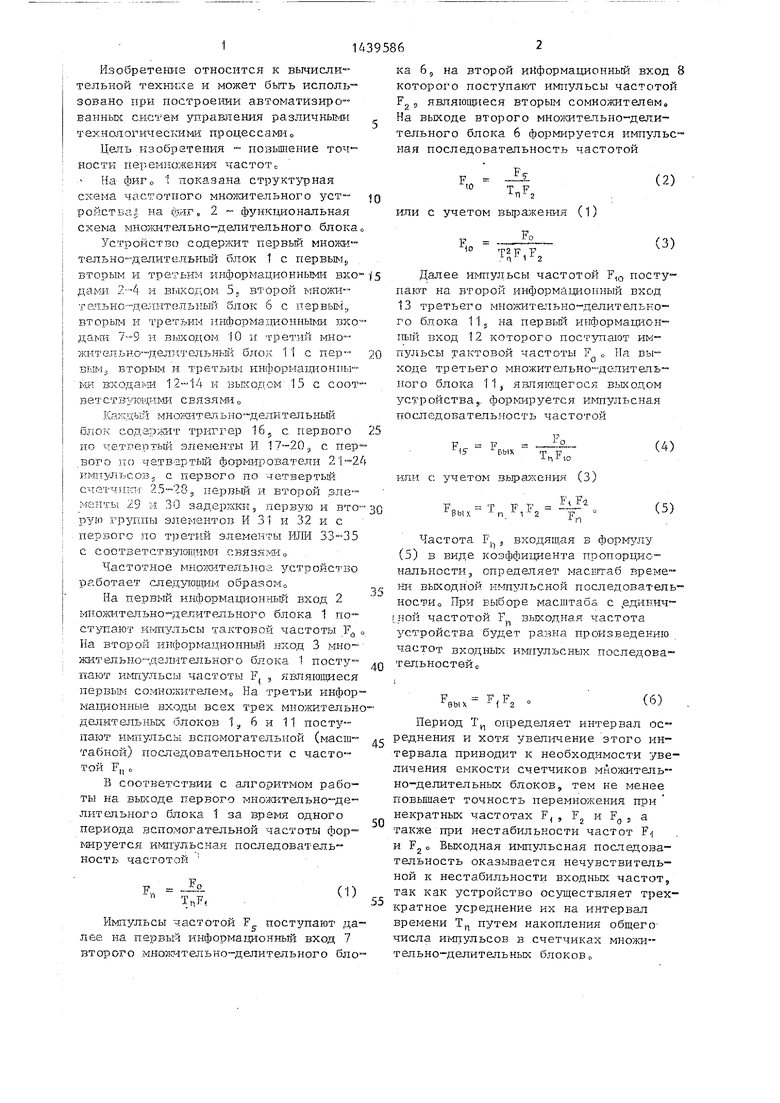

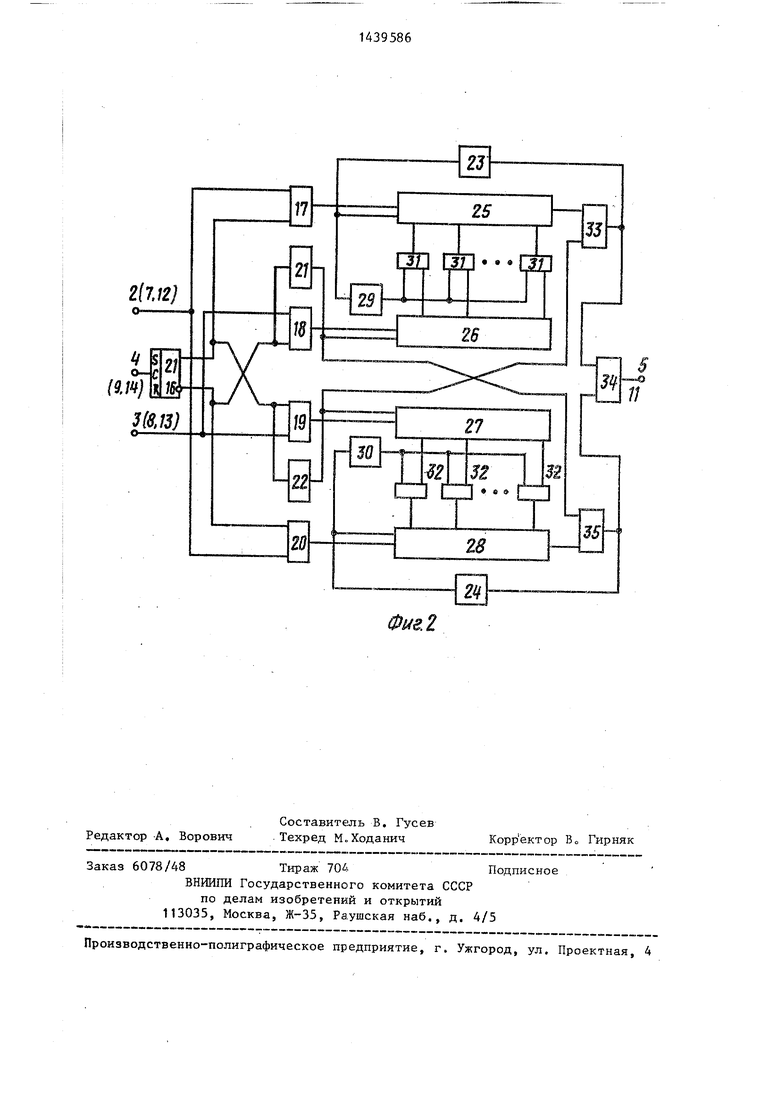

На фиг о 1 поК Э-зана структурная схема частотного множительного уст- роистБа| на йлг 2 функциональная схема множитапьно-делительного. блока

Устройство содержит первый мнозиг- тельно-далительньй блок 1 с первьм., вторым и третьим информационным - входамл и выходом 5. второй множи- тельно -делительный блок 6 с первьм,, вторым и третьим информа1щонны ш входами и выходом 10 и третий мно- яштельно-дел;5:тельный бхгок 11 с пер- БглМз вторым и третьим информационными вхотда з- 12-14 и вьпсодом 15 с соот- ветствз юг дими связяьм о

Каждый множительно-делктельный блок содерла1т триггер 16,, с первого по четрертый элементы И 17-20, с первого 310 четвертый формлгрователи 21-24 импульсов,- с первого по четвертьй c-qeT4Hi-:TT 25-28, первьп и второй зле- менты /9 и 30 задержки,, первую и вторув) грзш;пы sjiei -seHTOB И 31 и 32 и с первого по т :етнй элементы ШШ 33-35 с соответствующими связя:мно

Частотное мнохштельпог устройство работает Следующим образомо

На первьй информац онный вход 2 множительно-делительного блока 1 поступают и;ушульсы тактовой частоты V На второй информационный 3 мно жительно-делительного блока 1 посту™

пают импульсы частоты F , являющиеся первы1.{ сомножителемо На третьи инфор- магщонные входы всех трех множительно делительных блоков 1, 6 и 11 поступают имв:ульсы вспомогательной (масштабной) последовательности с частотой Ff, о

В соответствии с алгоритмом работы на вькоде первого множ тельно-де- лительного блока 1 за время одного периода вспомогательной частоты фор™ иpyeтcя илшульсная последовательность частотой

F.

(1)

Лг

Импзшьсы частотой F, постзшают далее на первый информагдаонный вход 7 второго мнозь7-1тельно-делительного блока б, на второй информационный вход 8 которого поступают импульсы частотой Fg 5 являющиеся вторьм сомножителемо На выходе второго множительно-дел:и- тельного блока 6 формируется импульсная последовательность частотой

(О

TnF,

(2)

или с учетом выражения (1)

F .(3)

10 T2F F

I.,, J. , 2

Далее импульсы частотой F,o поступают на второй информационный вход 13 третьего мнoжIiтeльнo-дeлитeльнo- го блока 115 на первьй ргнформацион- пый вход 12 которого поступают им- ni JibCH тактовой частоты F „ На ходе третьего множитапьно-делитель- кого блока 11, являгсгщегося выходом устройства5 формируется импульсная последователы-юсть частотой

F,

F

вых

,o

ли с учетом выраясения (3)

F. Fi

F

Вы V

т.

F,J 2

F

(4)

(5)

Частота F|., входящая в формулу (5) в виде коэффициента пропорпдо- нальности, определяет масштаб време- ш-1 выходной икшульсной последовательности При выборе масштаба с ,единич ной частотой F выходная частота устройства будет равна произведению

частот входньк импульсных последовательностей „

F F F

-(2

(6)

45

50

55

Период Т определяет интервал осреднения и хотя увеличение этого интервала приводит к необходимости увеличения емкости счетчиков множитель- но делительных блоков, тем не менее повышает точность перемножения при некратных частотах F, F и F а также при нестабильности частот F и Fgо Выходная импульсная последовательность оказывается нечувствительной к нестабильности входных частот, так как устройство осуществляет трехкратное усреднение их на интервал времени Т„ путем накопления общего числа импульсов в счетчиках множи-- тельно-делительных блоков

Формула изобретения

Частотное множительное устройство содержащее первый множительно-дели- тельньй блок, в состав которого входят триггер, первый, второй, третий и четвертый элементы И, первый, второй, третий и четвертый формирователи импульсов, первьй, второй, третий и четвертый счетчики, первьй и второй элементы задержки, первую и вторую группы элементов И, первый, второй и третий элементы РШИ, причем первые входы первого и четвертого элементов И соединены с первым информационным входо1ч блока, первые входы второго и третьего элементов И соединены с вторым информационным входом блокаJ вход синхро Изац1-1И триггера соединен с третьим информадионным входом блока, прямой выход триггера соединен с вторыг-ш входагда первого и третьего элементов И и вхо/дом второго фop я-IpoвaтeJIя ш-шульсов, выход которого соединен с первым входом первого элемента I-fflH и входом сброса третьего счетчика, инверсный выход , тртсггера соединен с вторыми входами второго и четвертого элe гeнтoв И и входом первого формирователя иг-шуль- соВэ выход которого соед.инен с первы 13ХОДОМ- третьего элемента ИЛИ и входом сброса второго счетчика, вькод первого элемента И соединен со счет™ ным входом первого счетчика, выход переполнения которого соединен с вторым входом первого элемента И,ПИ, выход второго элемента И соединен со счетньм входом второго счетчика, вы- ,ход третьего элемента И соединен со счетным входом третьего счетчика, выход четвертого элемента И соединен со счетным входом четвертого счетчика, выход переполнения которого- со- .единен с вторым входом третьего элемента ШШ, выходы первого и третьего элементов ИЛИ соединены с входами второго элемента ИЛИ, выход которого соединен с выходом блока, выход первого элемента Е1Ш соединен с входом третьего формирователя импульсов

0

0

5

5

выход которого соединен с входом сброса первого счетчика и входом первого элемента задержки, выход которого соединен с первыми входами элементов И первой группы, вькоды которых coeдliнeны соответственно с установочными входаьш первого счетчика, выход третьего элемента ИЛИ соединен с входом четвертого формировататя импульсов, выход которого соединен с входом сброса четвертого счетчика и входом второго элемента задержки, выход которого соединен с первыми 5 входами элементов-И второй группы, выходы которых соединены соответственно с установочными входакяг четвертого счетчика, инверсные разрядные выходы второго счетчика соединены соответственно с вторы н1 входами элементов И nepBOfi группы, инверсные разрядные вьпсоды третьего счетчика соединены соответственно с вторыми входами элементов И второй группы, отличающееся тем, что, с делыо повьшшния точности перемно- лсения частот, в него введены второй и третий множитзльно-делительные блоки, прр1чем первьй информационньй вход первого множительно-делительно- го блока соединен с первым информационньй входом третьего множительно™ делительного блока и с входом опорной частоты устройства, второй информационньй вход первого множительно- делитель ного блока соединен с первым информационным входом устройства, третьи информационные входы первого, второго и третьего множительно-дели- тельных блоков соединены с масштабным входом устройства, вькод первого множительно-дачительного блока соединен с первьм информационным входом второго множительно-делительного блока, второй информационньй вход которого соединен с вторым информационным входом устройства, выход второго мно- жительно-делительного блока соединен. с вторым информационным входом третьего множительно-делительного блока, выход которого является выходом устройства.

0

5

0

| Частотно-импульсное множительно-делительное устройство | 1979 |

|

SU932493A1 |

Авторы

Даты

1988-11-23—Публикация

1986-12-11—Подача