соединен с первыми входами третьего, четвертого и пятого триггеров и через второй и третий элементы задержки подключен соответственно ко входу обнуления основного счетчика и ко вторым входам элементов И основной группы, выхо; которых через регистр соединены с первыми входами элементов И дополнительной группы, вторые входы которых подключены к третьему входу множительно-делительного блока и к вь1ходу дополнительного счетчика, разрядные вхйды которого соединены с выходами элементов И дополнительной группы, а счетный вход подключен к выходу пятого элемента И, соединенного первым входом с выходом третьего триггера, а вторым входом с входом запуска устройства и с первыми входами шестого и седьмого элементов И, вторые входы которых сов динены с входом устройства и со вторым входом третьего элемента И, подключенного выходом к вторым входам четвертого и пятого триггеров, первые выходы которых соединены соответственно с вторым входом первого и третьим входом шестого элементов И, причем выход шестого элемента И через четвертый элемент задержки подключен к входу второго триггера, а второй выход пятого триггера соедине с третьим входом .первого элемента И, а выход седьмого элемента И, подключенного третьим входом к выходу шестого триггера, соединен с первым входом основного элемента ИЛИ, второй вход которого подключен к выходу множительно-делительного блока и входу шестого триггера.

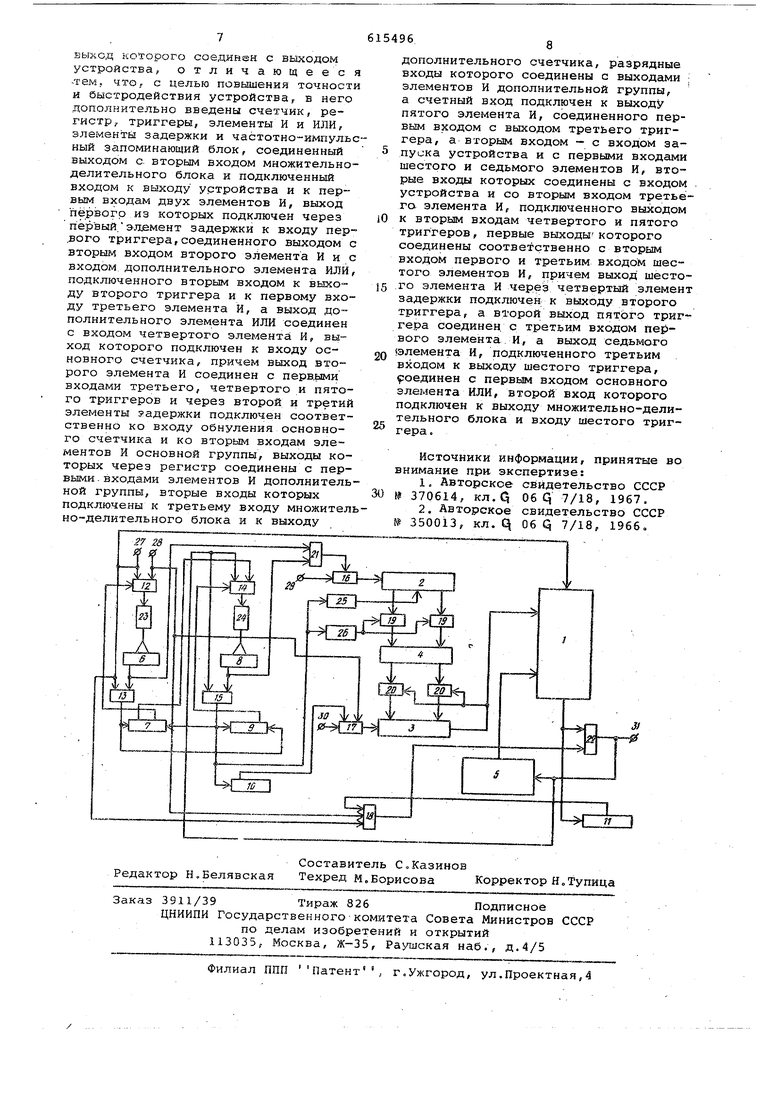

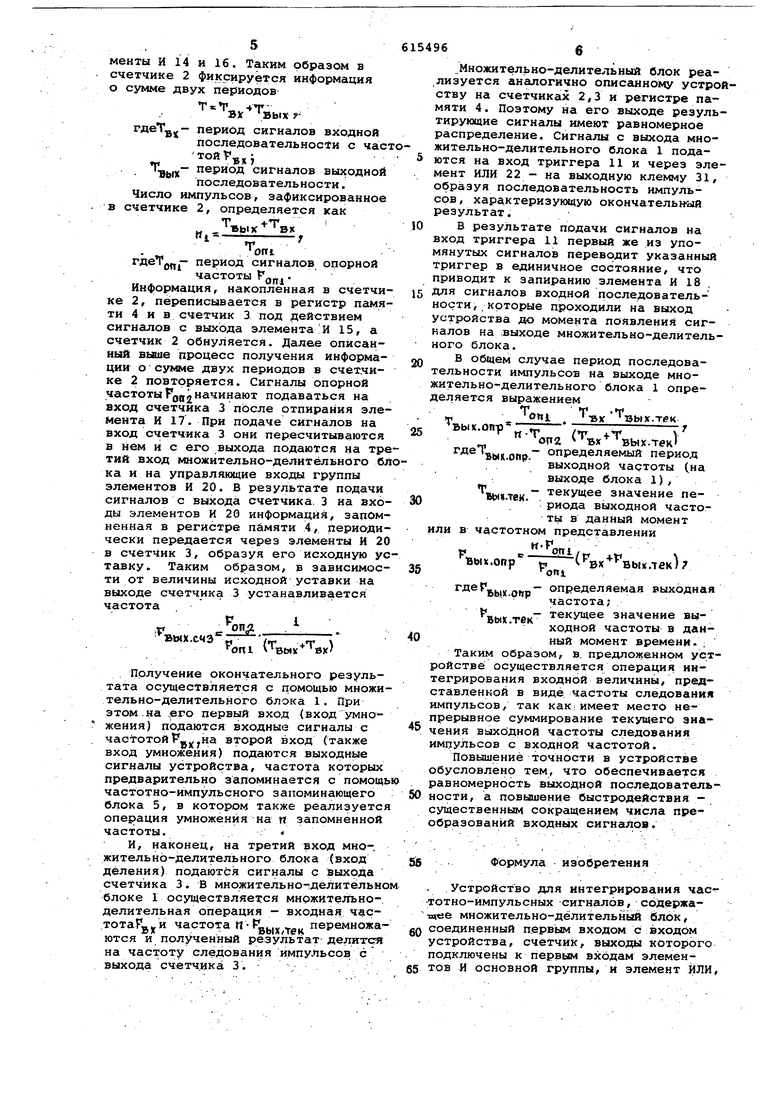

На чертеже представлена функциональная схема устройства для интегрирования частотно-импульсных сигналов

Устройство содержит миожительноделительный блок 1, основной счетчик 2, дополнительный счетчик 3, регистр 4, частотно-импульсный запоминакиций блок 5,. триггеры 6jl 1, элементы И 12-г18, группы элементов И 19 20 элементы ИЛИ 21,22, элементы задержки 23т-26, клемму 27 подачи входных сигналов клемму 28. подачи сигнала запуска, клеммы 29,30 подачи сигналов опорных частот, выходную клемму 31 .

Устройство работает следующим образом. Входные сигналы с частотойР подаются на клему1у 27. Сигналы опор ных частот оп иРод2Подаготся соответственно на клеммы 29 и 30. В исходном состоянии счетчики, регистры и триггеры устройства обнулены. В момент t на 28 подается сигнал запуска. При этом первый после момента t, импульс, подаваемый на клемму 27, проходит через элемент И1 и через элемент задержки 23 на счетный вход триггера 6, переводя его лз нулевого в единичное состояние.,. Очевидно, что при этом сигнал не про ходит на выход элемента И 13, так как отпирающий сигнал с триггера 6 подается на его вход с задержкой за счет элемента задержки 23. С переводом триггера б в единичное состояние отпирающий сигнал с его выхода подается на вход элемента И 13 и через элемент ИЛИ 21 - на вход элемента И 16. При этом через элемент И 16 на вход счетчика 2 начинают подааатьг ся сигналы опорной частоты Р,,которые выполняют функцию заполнения периода частоты . При этом заполнение периода входной частоты осуществляется до момента поступления следующего сигнала на 27. При поступлений следующего сигнала на клемму 27 этот сигнал проходит на выход элемента И 13, переводя триггер 7 в и через время, определяемое элементом задержки 23, переводит триггер 6 в нулевое состояяие. В результате прекращения подачи отпиракяцего напряжения на вход элемента И 16 прекргицается подача сигналов опорной частотыРОП| на вход счетчика 2, и в нем фиксируется информация, соответствующая периоду частотыР«.Одновременно в результате перевода триггера 7 в. единичное состояние открывается элемент И 14 для сигналов с выхода интегратора, конкретно с выхода элемента ИЛИ 22, и запирается эле1мент И 12 для входных сигналов с . частотой Pjj.Первые сигналы на выход интегратора проходят с клеммы 27 через элемент И 18 и элемент ИЛИ 22. Первый после момента отпирания элемента И 14 сигнал из выходной после- довательности проходит через элемент И 14 и элемент;задержки 24 на счетный вход триггера 8, переводя его из нулевого е единичное состояние.

В результате отпирающий сигнал с выхода триггера 8 подается на вход элемента И 15 и через элемент ИДИ 21- на вход элемента И 16. При этом через элемент И 16 на вход счетчика 2

начинают подаваться сигналы опорной частотыРдд,которые су Фтруются с ранее .накопленной s счетчике 2 информацией о периоде входного сигнала Заполнение периода сигналов выходной

последовательности осуществляется . до момента поступления следующего сигнала с выхода, устройства на вход; элемента И 14.: При поступлений этого сигнала он проходит на выхрА элемента И 15, переводя триггеры 9 и 10

в единичное состояние, а триггер 7 - в нулевое. Через время, определяемое элементом задержки 24, осуществляется хакжё перевод триггера 8 в нулевое состояние, ь результате, открывгиотся

элементы И 12 и 17 и запираются эле менты И 14 и 16. Таким образом в счетчике 2 фиксируется информация о сумме двух периодов sV 4Т B)f г период сигналов входной последовательности с час ToaV j период сигналов выходной последовательности. Число импульсов, зафиксированное счетчике 2, определяется как Т +Т . гдеТ,- период сигналов опорной частоты Информация, накопленная в счетчи накопленная в ке 2, переписывается в регистр памя ти 4 ив счетчик 3 под действием сигналов с выхода элементами 15, а счетчик 2 обнуляется. Далее описанный BiAiie процесс получения информации о сумме двух периодов в счет.чике 2 повторяется. Сигналы опорной частоты Гон2 начинают подаваться на вход счетчика 3 после отпирания эле мента И 17. При подаче сигналов на вход счетчика 3 они пересчитываются в нем и с его выхода подаются на тре тий вход множительно-делитёльного бл ка и на управляющие входы группы элементов И 20. В результате подачи сигналов с выхода счетчика. 3 на вхо ды элементов И 20 информация, запомненная в регистре пймяти 4, периоди чески передается через элементы И 2 в счетчик 3, образуя его исходную ус тавку. Таким образом, в зависимос ти от величины исходной уставки на выходе счетчика 3 устанавливается частота ВЫХХЧЭ Получение окончательного результата осуществляется с помощью множи тельно-делитёльного блока 1. При этом на ,jero первый вход (вход умножения) подаются входные сигналы с частотойР- на второй вход (также вход умножения) подаются выходные сигналы устройства, частота которых предварительно запоминается с помощ частотно-импульсного запоминающего блока 5, в котором также реализуетс операция умножения на п запомненной частоты. . И, наконец, на третий вход мно-. жительно-делительного блока (вход деления) подаются сигналы с выхода счетчика 3. В множительно-делительн блоке 1 осуществляется множительноделительная операция - входная частотаРд и частота M-Pgy перемножа ются и полученный результат делится на частоту следования импуЛьсов с выхода счетчика 3. .. . Множительно-делительный блок реализуется аналогично описанному устройству на счетчиках 2,3 и регистре памяти 4. Поэтому на его выходе результирующие сигналы имеют равномерное распределение. Сигналы с выхода множительно-делитёльного блока 1 подаются на вход триггера 11 и через элемент ИЛИ 22 - на выходную клемму 31, образуя последовательность импульсов, характеризующую окончательном результат. В результате подачи сигналов на вход триггера 11 первый же из упомянутых сигналов переводит указанньой триггер в единичное состояние, что приводит к запиранию элемента и 18 . для сигналов входной последовательности, которые проходили на выход устройства до момента появления сигналов на .выходе множительно-делительного блока. В общем случае период последовательности импульсов на выходе множительно-делитёльного блока 1 определяется выражением ощ , :в)с вых.тек ъы. - &х вых-тек V 1 определяемый период гык.опр. выходной частоты (на выходе блока 1), текущее значение периода выходной частоты в данный момент в частотном представлении вх вьилек)7 BbOf.ORp f. - определяемая выходная БЫх.рпр частота; - текущее значение выВых.тек ходной частоты в данный момент времени.. Таким образом, в. предложенном устройстве осуществляется операция интегрирования входной величины, представленной в виде частоты следования импульсов, так как:имеет место непрерывное суммирование текущего зиачения выходной частоты следования импульсов с входной частотой. Повышение точности в устройстве обусловлено тем, что обеспечивается равномерность выходной последовательности, а повышение быстродействия - существенным сокращением числа преобразований входных сигналов Формула изобретения Устройство для интегрирования частотно-ймпульсных сигналов, содержатцее множительно-дёлительный блок, соединенный п.ервым входом с : входом устройства, счетчик, выходы которого подключены к первым входам элементов И основной группы, и элемент ИЛИ,

Авторы

Даты

1978-07-15—Публикация

1974-12-19—Подача