4 4

СО 00 О)

Изобретение относится к вычислительной технике и может быть использовано в специализированных процессорах для обработки информации в реальном масштабе времени.

Целью изобретения является повышение быстродействия устройства.

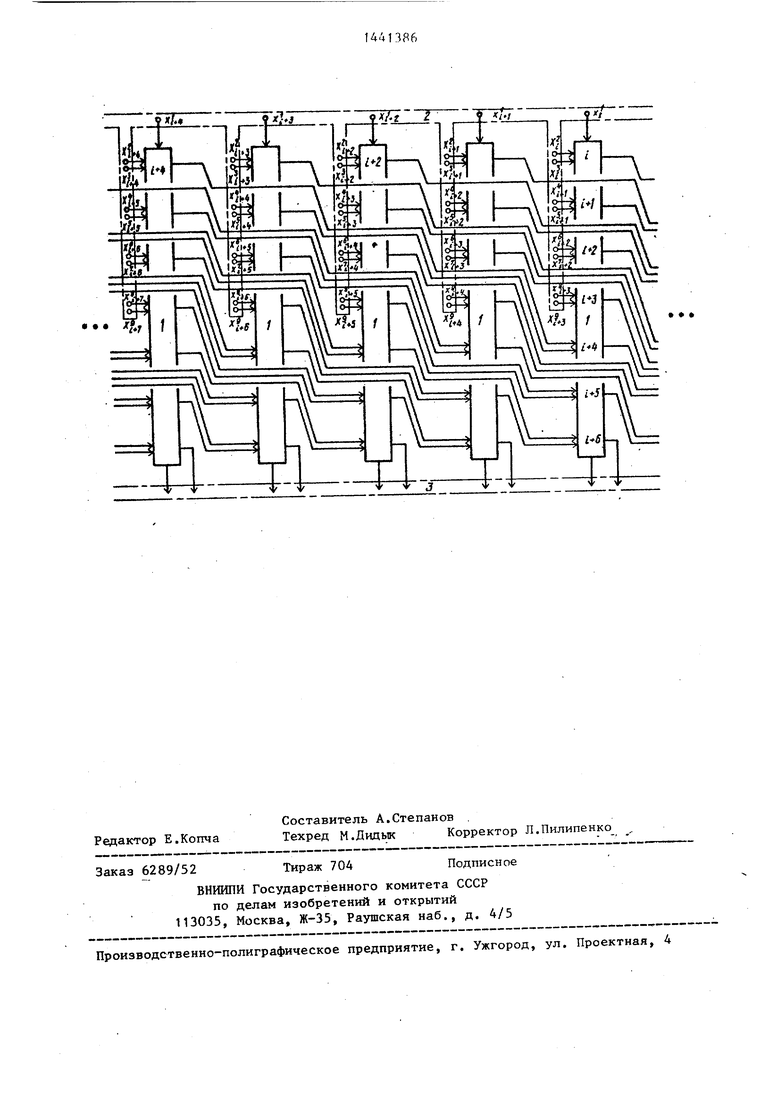

На чертеже приведена структурная схема многовходового суммирующего устройства для случая суммирования девяти чисел (N 9).

Многовходовое суммирующее устройство содержит (N - 2)-разрядные сумматоры 1, имеющие входы 2 слагаемых и выходы 3 двзгхрядного кода результата.

2 3 i, J,

разрядов

N) - на входы

Устройство работает следующим образом.

Разряды N слагаемых подаются на входы 2 устройства. При этом разряды первого слагаемого поступают на входы начального переноса сумматоров 1, а разряды 1-го слагаемого (1

гп (1 + 1 - т I ° слагаемого сумматоров 1. Сигнал, сформированный на выходе i-ro разряда (i 1, 2N - 3) суммы j-ro сумpN + il матора 1, приходит на вход

го разряда (1 « N + i - 2 -т

f ТТ

слагаемого (j--:г- -го сунматора 1 .Пр L / J

этом i-й разряд j-ro сумматора 1 осуществляет сложение переменных с весовым коэффициентом 2 . На выходах (N - 2)-го и :(N - 1)-го разрядов суммы сумматоров 1 формируются разряды двухрядного результата, поступающие на выходы 3 устройства.

го

-

ю

15

20

25

30

ри I

40 45

о

35

Повьппение быстродействия достигается за счет сокращения числа пересылок информации между сумматорами с N - 3 до М - 1, где М log(N- -1), а также за счет того, что в параллельном сумматоре имеется возможность повышения быстродействия за счет ускорения переноса.

Формула изоб ретения

Многовходовое суммируюп(ее устройство, содержащее (N - 2)-разрядные сумматоры, где N - количество суммируемых чисел, причем вход переноса младшего разряда каждого сумматора соединен с соответствующим разрядом первого слагаемого устройства, первый вход i-ro разряда, где i 1,

N - 1Г , каждого J-ro сумматора

соединен с (j + i - 1)-м разрядом (2i)-ro слагаемого устройства, второй вход первого разряда каждого сумматора соединен с соответствующим разрядом третьего слагаемого устройства, выхода и переноса старшего разряда каждого сумматора соединены с выходами соответствующих разрядов двухрядного кода результата устройства, отличающееся тем, что, с целью повьш1ения быстродействия, второй вход i-ro разряда,

где 1 2, ..., , кавдого

j-ro сумматора соединен с (j + i - - 1)-м разрядом (2i + 1)-го слагаемого устройства, выход i-ro разряда (i 1, ..., N - 3) суммы j-ro сумматора соединен с

(N + i + 1 + 2 «

fN + Г.Гм + i1

(-п-и входом -S- -го разL - J fN - il L - J ряда (j - I-2-J

ro сумматора.

F4S

/;

vv

LII 4/j I

. P j . I т -ли:

V |jr4,ir 7 «I //

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования N @ -разрядных чисел | 1979 |

|

SU920707A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения двух N-разрядных чисел | 1987 |

|

SU1524046A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Двоично-десятичный сумматор | 1990 |

|

SU1728859A1 |

Изобретение относится к области вычислительной техники и может быть использовано в специализированных процессорах для обработки информации в реальном масштабе времени. Целью изобретения является повьшение быстродействия устройства. Устройство реализует алгоритм параллельного по словам и разрядам суммирования чисел. Устройство содерткит (N - 2)-разрядные параллельные сумматоры. Поставленная цель достигается за счет введения новых связей в подключении входов параллельных сумматоров к /входам разрядов слагаемых и к выходам других сумматоров. Это позволяет существенно уменьшить число каскадов задержки в формировании суммы, а также применить в устройстве параллельные сумматоры с возможностью ускорения переноса. 1 ил. (Л

| Карцев М.А,, Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| М.: Радио и связь, 1981, с | |||

| УСТРОЙСТВО ПАРОПЕРЕГРЕВАТЕЛЯ | 1920 |

|

SU295A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многовходовое суммирующее устройство | 1980 |

|

SU898422A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-30—Публикация

1986-06-02—Подача