1

Изобретение относится к вычислительной технике, а именно к устройствам для сложения массивов-чисел, например для сложения частичных произведений в быстродействующих умножителях.

Известны устройства для суммирования N п-разрядных двоичных чисел, содержащие п блоков суммирования, каждый из которых содержит m рядов одноразрядных двоичных сумматоров

2

(

), ВХОДЫ одноименных

разрядов слагаемых устройства соединены со входами соотиетствующего блока суммирования, выходы переносов каждого блока суммирования соединены со входами последующего блока суммирования l и Cz .

Недостатком их является сложность конструкции из-за большого количества перекрестных связей внутри каждого блока и большого количества межблочных соединений.

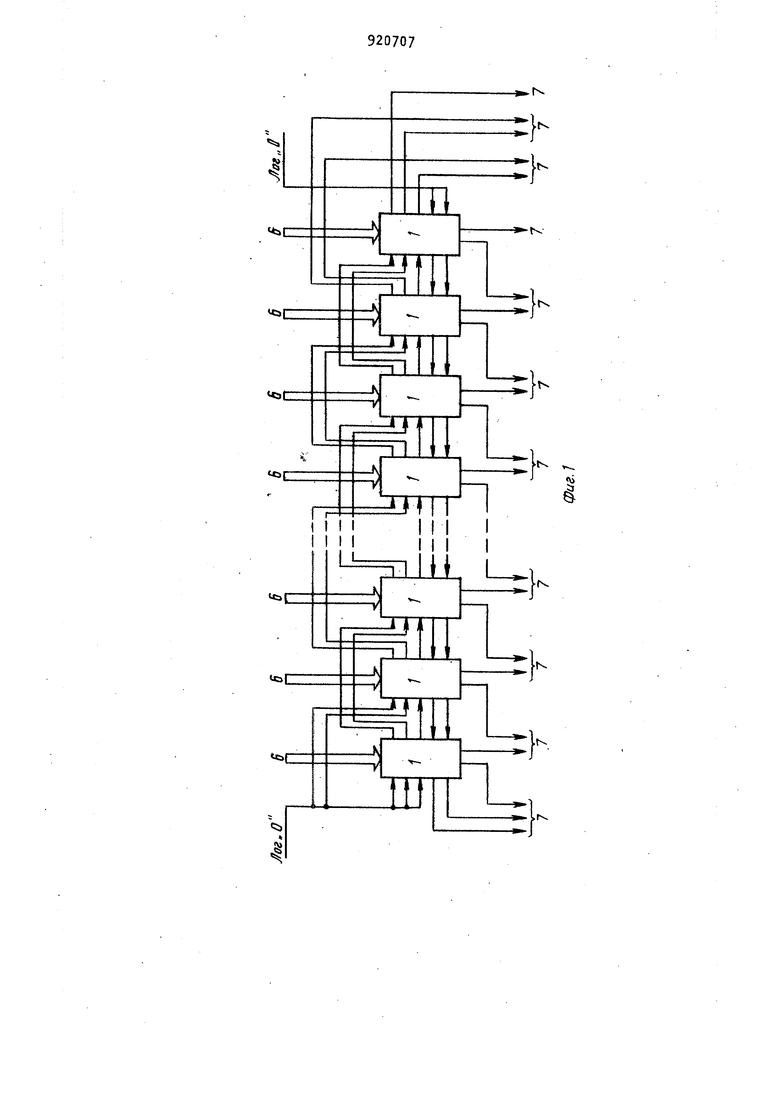

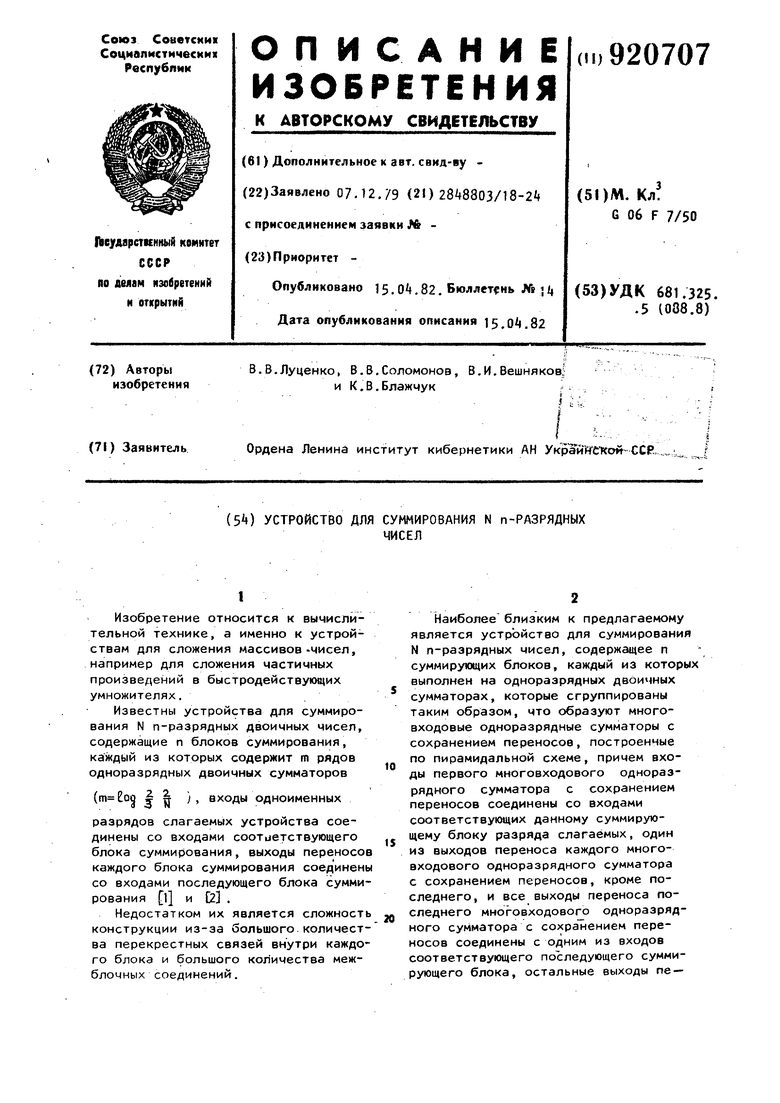

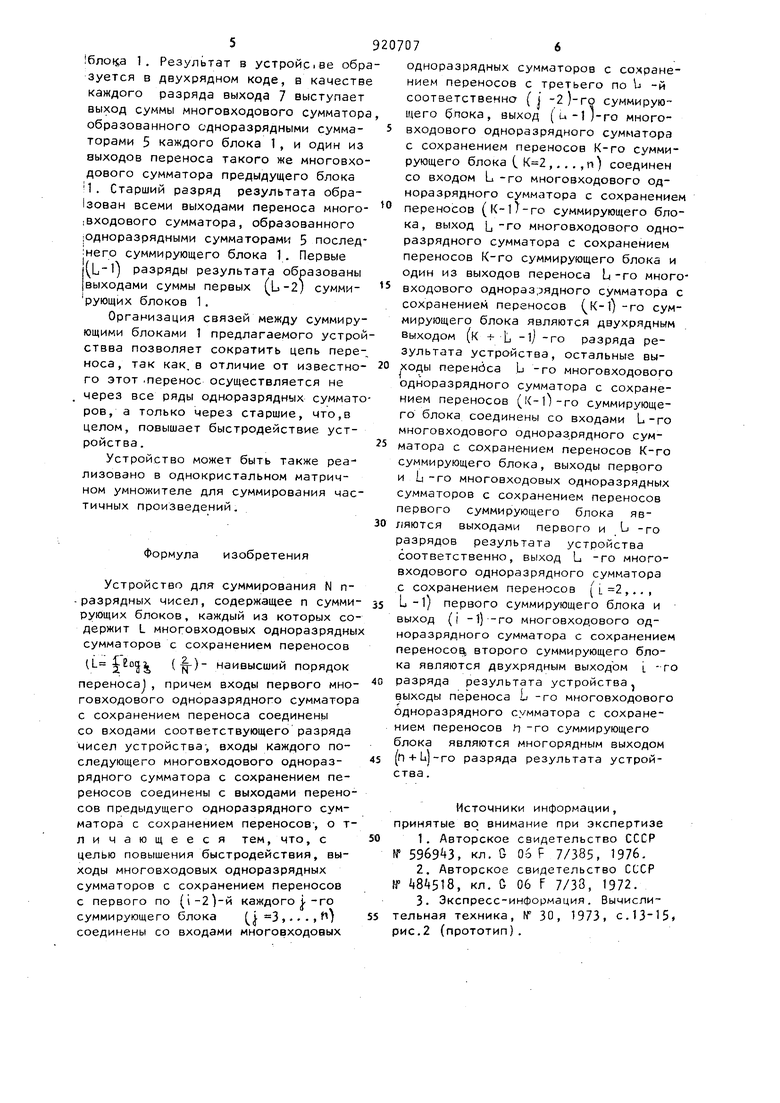

Наиболее близким к предлагаемому является устройство для суммирования N п-разрядных чисел, содержащее п суммирующих блоков, каждый из которых выполнен на одноразрядных двоичных сумматорах, которые сгруппированы таким образом, что образуют многовходовые одноразрядные сумматоры с сохранением переносов, построенные по пирамидальной схеме, причем входы первого многовходового одноразрядного сумматора с сохранением переносов соединены со входами соответствующих данному суммирующему блоку разряда слагаемых, один из выходов переноса каждого многовходового одноразрядного сумматора с сохранением переносов, кроме последнего, и все выходы переноса последнего многовходового одноразрядного сумматора с сохранением переносов соединены с одним из входов соответствующего последующего суммирующего блока, остальные выходы пе- реносов каждого многовходового одноразрядного сумматора с сохранением переносов, кроме последнего, соединены со входами последующего многовходового одноразрядного сумматора с сохранением переносов, выход суммы первого многовходового одноразрядного сумматора является выходом разряда результата, соответствующим данному суммирующему блоку |3 , Недостатком этого устройства является невысокое быстродействие, ввн ду того, что выходы каждого, суммирующего блока связаны со входами первого многовходового многозарядного сумматора одного из последующих суммирующих блоков. Цель изобретения - повышение быстродействия устройства. Для дрстижения поставленной цели в устройстве для суммирования N празрядных чисел, содержащем п суммирующих блоков, каждый из которых содержит L многовходовых одноразрядных сумматоров с сохранением пеi 3|C реносов (L наивысший порядок переноса) ,прйчем входы перв го многовходового одноразрядного су матора с сохранением переносов соединены со входами соответствующего разряда чисел устройства, входы каж дого последующего многовходового о норазрядного сумматора с сохранение переносов соединены с выходами пере носов предыдущего одноразрядного сумматора с сохранением переносов в ходы многовходовых одноразрядных сумматоров с сохранением переносов с первого по (-2)-й каждого j-ro суммирующего блока (j 3,...,п) соединены со входами многовходовых одноразрядных сумматоров с сохранением переносов с третьего по L-й соответственно (j-2)-ro суммирующег блока, выход (L-l)-ro многовходовог одноразрядного сумматора с сохранением переносов К-го суммируюещго бл ка ( ,.. . г соединен со входом L-ГО многовходового одноразрядного сумматора с сохранением переносов .{К-1)-го суммируюещго блока, выход L-ro многовходового одноразрядного сумматора с сохранением переносов К-го суммирующего блока и один из выходов переноса многовходово одноразрядного сумматора с сохранением переносов (К-1) -го суммирующеj o блока являются двухрядным выходо К 4- L-l)-ro разряда результата устройства, остальные выходы переноса L-ro многовходового одноразрядного ,., сумматора с сохранением переносов ( суммирующего блока соединены со входами L-ro многовходового одноразрядного., сумматора с сохранением-г1ереносов К-го суммирующего блока, выходы первого и L-ro :многовходовых одноразрядных сумматоров с сохранением переносов первого суммирующего блока являются выходами первого и L-ГО разрядов результата устройства соответственно, выход 1,-го многовходового одноразрядного сумматора с сохранением переносов {.,..,, L-1) первого суммирующего блока и выход (i-l)-ro многовходового одноразрядного сумматора с сохранением переносов второго суммирующего блока являются двухрядным выходом -го разряда результата устройства, выходы переноса L-многовходового одноразрядного сумматора с сохранением переносов п-го суммирующего блока являются многЬрядкым выходом (n+L)-ro разряда результата устройства. На фиг.1 показана блочная схема устройства для суммирования двадцати семи п -ра.зрядных двоичных чисел; на фиг.2 - структурная схема одного суммирующего блока. Устройство содержит суммирующие блоки 1 , каждый и;з которых содержит одноразрядные сумматоры 2-5, образующие первый, второй, третий и четвертый многовходовые одноразрядные сумматоры с сохранением переносов. Входы 6 первых многовходовых одноразрядных сумматоров каждого блока 1, образованных одноразрядными сумматорами 2, соединены со входами 6 соответствующего разряда N-разрядных чисел (). Выходы суммы каждого из многовходовых одноразрядных сумматоров с распространением переносов, образованных одноразрядными сумматорами 2 и 3 j-ro блока суммирования 1 соединены со входами (j-2)-ro суммирующего блока 1 . Выход суммы многовходового сумматора, образованного одноразрядными сумматорами К-го блока 1, соединен со входом (К-м-го блока суммирования 1., Все выходы переноса, кроме одного многовходового сумматора, образованного одноразрядными сумматорами 5 (K-l)-ro блока Т, соединены со входами К-го 5 бло)а 1. Результат в устройс.ве обр зуется в двухрядном коде, в качеств каждого разряда выхода 7 выступает выход суммы многовходового сумматор образованного одноразрядными сумматорами 5 каждого блока 1, и один из выходов переноса такого же многовхо дового сумматора предыдущего блока П. Старший разряд результата обра1зован всеми выходами переноса много 1ВХОДОВОГО сумматора, образованного одноразрядными сумматорами 5 послед :него суммирующего блока 1. Первые j() разряды результата образованы |выходами суммы первых суммирующих блоков 1. Организация связей между суммиру ющими блоками 1 предлагаемого устро ствва позволяет сократить цепь пере носа, так как, в отличие от известно го этот -перенос осуществляется не через все ряды одноразрядных суммато ров, а только через старшие, что,в целом, повышает быстродействие устройства. Устройство может быть также реализовано в однокристальном матричном умножителе для суммирования частичных произведений. Формула изобретения Устройство для суммирования N п-разрядных чисел, содержащее п суммирующих блоков, каждый из которых содержит L многовходовых одноразрядны сумматоров с сохранением переносов (L 2oij ()- наивысший порядок переноса , причем входы первого многовходового одноразрядного сумматора с сохранением переноса соединены со входами соответствующего разряда чисел устройства-, входы каждого последующего многовходового одноразрядного сумматора с сохранением переносов соединены с выходами переносов предыдущего одноразрядного сумматора с сохранением переносов-, о тличающееся тем, что, с целью повышения быстродействия, выходы многовходовых одноразрядных сумматоров с сохранением переносов с первого по ((-2)-й каждого |.-го суммирующего блока Ц 3 ,.. - , соединены со входами многовходовых 07 одноразрядных сумматоров с сохранением переносов с третьего по Ь -и соответственно (J -2)-го суммирующего блока, выход (u-l)-ro многовходового одноразрядного сумматора с сохранением переносов К-го суммирующего блока С ,...,п) соединен со входом L -го многовходового одноразрядного сумматора с сохранением переносов (K-l)-ro суммирующего блока, выход , -го многовходового одноразрядного сумматора с сохранением переносов К-го суммирующего блока и один из выходов переноса L-го многовходового одноразрядного сумматора с сохранением переносов (К-l) -го суммирующего блока являются двухрядным Выходом (к + L -1J -го разряда результата устройства, остальные выЬ -, ходы переноса ,--,-,- , - го многовходового одноразрядного сумматора с сохранением переносов ()-ro суммирующего блока соединены со входами L-ro многовходового одноразрядного сумматора с сохранением переносов К-го суммирующего блока, выходы первого и Ь -го многовходовых одноразрядных сумматоров с сохранением переносов первого суммирующего блока явяяются выходами первого и Ь -го разрядов результата устройства соответственно, выход L -го многовходового одноразрядного сумматора ,.., с сохранением переносов L -1) первого суммирующего блока и выход (i -l)--ro многовходового одноразрядного сумматора с сохранением переносов, второго суммирующего блока являются двухрядным выходом i. -го разряда результата устройства, выходы переноса Ь -го многовходового одноразрядного сумматора с сохранением переносов п -го суммирующего блока являются многорядным выходом (n + LJ-ro разряда результата устройства. Источники информации, принятые во внимание при экспертиза 1. Авторское свидетельство СССР № , кл. G Об F 7/385, 1976. 2.Авторское свидетельство СССР № i 8if5l8, кл. G 06 F 7/38, 1972. 3.Экспресс-информация. Вычислительная техника, № 30, 1973, с. рис.2 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования нескольких Р-ичных чисел | 1983 |

|

SU1188730A1 |

| Устройство для сложения @ чисел | 1980 |

|

SU1012243A1 |

| Многовходовое суммирующее устройство | 1986 |

|

SU1441386A1 |

| Многовходовое суммирующее устройство | 1980 |

|

SU898422A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения двух N-разрядных чисел | 1987 |

|

SU1524046A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

LZJ

LZJ

г

w

i

л

ir

Фигг

.j

Авторы

Даты

1982-04-15—Публикация

1979-12-07—Подача