первого уровня, инверсньй выход стар шего разряда (4 + группы регистра множителя соединен с первым входом второго элемента И то элемента 2И-ЙЛЙ первой группы блока диализа множителя и с (М+ 2 i + 2)-м весовым входгом Д i / Р -ГО сумматора двухрядного кода первого, уровня, выход второго разряда (, + 1;-й группы разрядов регистра множителя соединен с вторым взводом второго элемента М i -го элемента 2И-ИЛИ первой группы блока анализа множителя и с первым входом первого элемента И i-ro элемента 2Й-ИЛИ второй группы блока анализа множителя, инверсный выход второго разряда (i + 1)-й группы регистра множителя соединен с вторым входом первого элемента И i-ro элемента 2И-ИЛИ первой группы блока анализа множителя и с первым входом второго элемента И i -го элемента 2H-IOTi второй группы блока анализа множителя, вькод младшего разряда ( i + 1)-й группы регистра множителя соединен с третьим входом второго элемента И i -го элемента 2И-ЙЛИ первой группы блока аналиэа множителя и с вторь м входом второго элемента И i -го элемента 2И-ИЛИ второй группы блока аналиэа множителя, инверснЕда выход младшего разряда ( i - 1) -и группы регистра множителя соединен с третьим входом первого элемента. И -го элемента 2И- ИЛИ первой группы блока аналиэа множителя и с вторым входом первого элемента И I -го элемента 2И-Ш1И втрой группы блока анализа множителя, первый вход первого элемента И каждой группы блока формирования кратных множимого соединен с М -м разрядом регистра множимого, первый вход второго элемента И кащ;ой группы блока формирования кратных множимого соединен с первым разрядом регист1 а множимого,, первые входы первого элемента И и k -го элемента 2И-ИЛИ каждой группы блока формировании кратных множимого соединены -С (К + 1)-м выходом регистра множимого (К 1, 2, ..., М- 1), первый вход второго элемента и k; -го элемента 2И-ИЛЙ каждой группы блока форйирования кратных Ь1ножимого соедйнен с К -м выходом регистра множимого, прямой выход младшего разряда первой группы регистра множителя соединен с вторыми входами пеовых

элементов И элементов 2И-ИПИ и второго элемента И первой группы блока формирования кратных множимого, выход элемента И блока аналиэа множителя соединен с вторыми входами вторых элементов И элементов 2И-ИПИ и первого элемента И первой группы блока форшрования кратных множимого, выход 1 -го элемента 2И-ИЛИ первой группы блока анализа множителя соединен с вторыми входами вторых элементов И элементов 2И-ИЛИ и первого элемента И ( + 1)-й группы блока формирования кратных множимого, вькод 1 -го элемента 2И-ШТИ второй группы блока анализа множителя соединен с вторыми входами первых элементов И элементов 2И-ИЛИ и второго элемента И (i + 1)-й группы блока формирования кратных множимого, выходы первого и второго элементов И -и группы которого соединены соответственно с вторыми входами (М + + 1)-го и первого полусумматоров 1-й группы блока формирования кратных множимого, выход К -го элемента 2И-ИЛИ 1 -и группы которого соединен с вторым входом ( i; -v t)-ro полусумматора i -и группы блока формирования кратных множимого, выход р-го полусумматора J -и группы которого соединен с (2 + р - 2)-м весовым входом 1 сумматора двухрядного кода первого уровня (р - 1, 2, „.., М + 1), шика логической единицы устройства соединена с {М + 2 + + 3)-ми весовыми входами сумматора двухрядного кода первого уровня, выходы суммы и переноса |ft/26 сумматоров двухрядного кода первого уровня соединены с соответствующими разрядными входами Ь/Б регистров суммы и переноса блока регистров первого уровня соответствен,но, выходы разрядов регистра множиMord соединены соответственно с разрядными входами.второго регистра множимого, выходыJ N/9 регистров суммы и переноса блока регистров первого уровня соединены с соответствующими весовыми входами сумматора дв.ухрядного кода второго уровня, -й выход второго регистра множимого соединен соответственно с (N + ; + ( - 1)-м весовым разрядом сумматора друхрядного кода второго уровня (( 1,2, ...М), управляющие входы регистров соединены с входом синхронизации устройства. 111 Изобретение относится к автоматике и вычислительной технике и предназначено для использования в быстродействукжщх цифровых арифметически устройствах для умножения нормалйзованньк чисел. Известны устройства для умножения двоичных чисел, содержащие регистры множителя и множимого, блок формирования кратных множимого, матрицу сумматоров, регистр результата lj . Наиболее близким по технической сущности к предлагаемому является устройство для умножения, содержащее регистры сомножителей и результата, .регистр суммы и переноса двухрядного кода, блок анализа семи разрядов множителя и три блока, содержащих по четыре кратных множимого каждьй, три сумматора двухрядного кода первого уровня, параллельный сумматор. Результат произведения получается путем последовательной обработки разрядов множителя, цричем за один такт производится обработка только семи разрядов множителя. При этом семь разрядов множителя разбива1отся на три группы по три разряда в каждой. По сигналам, обра- зующимся в результате анализа указанных триад, производится выборка соответствуюгщх кратных множимого, которые суммируются на. .сумматорах двухрядного кода. Результат суммирования постзтает на регистр суммы и переноса двухрядного кода. Если обра ботаны не все разряды множителя, то код с регистра двухрядного кода поступает в качестве слагаемого на вход одного из сумматоров двухрядного кода. В противном случае коды суммы и переноса с регистра двухрядного к да подаются на параллельный су 1матор на выходе которого образуется резул тат произведения, который подается :в регистр результата 2j. Однако устройство обладает невыс ким быстродействием из-за последова тельной обработки разрядов множителя Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройство для умножения содержащее VI -разрядный регистр мно жителя, М -разрядный регистр множимого, блок анализа множителя, блок формирования кратных множимого, три сумматора двухрядного кода первого уровня, регистр двухрядного кода, параллельный сумматор, регистр результата, причем разрядные выходы регистра двухрядного кода соединены с соответствующими весовыми входами параллельного сумматора, разрядные выходы которого соединены с соответствующими весовыми входами регистра результата, разрядные выходы регистра множимого соединены с соответствующими разрядными входами блока формирования кратных множимого, введены 3 сумматоров двухрядного кода первого уровня (С 3, 4, 6, 9, 13, ...), сумматор двухрядного кода второго уровня, блок регистров, содержащий N/E + 1 регистров разрядностью (М + 2 + 1) каждый, второй М -разрядный регистр множимого, причем блок формирования кратных множимого содержит 1 N /2 групп по два элемента Ни (М- 1) элементов 2И-ИЛИ и N /2 С групп по (М + 1) полусумматоров, а блок анализа множителя содержит элемент И, первую и вторую группы - l элементов 2И-ИЛИ, причем -регистр множителя разделен + ll групп разрядов, первая из которых содержит два младших разряда, а 1 -я группа три разряда. ( j 2, 3, ... Н /2 + + 1), причем старший разряд i -и группы регистра множителя ( 1, 2, ...Н/2 + 1j) равен по значению мпадщему разряду ( i + 1)-й группы разрядов регистра множителя, выход старщего разряда первой группы регистра множителя соединен с первым входом элемента И блока анализа множителя, с первым, ( 2)-м и (М+ 3)-м весовыми входами первого сумматора г двухрядного кода первого уровня и с первыми входами полусумматоров пер группы блока формирования кратных множимого, инверсный выход младшего разряда первой группы регистра множителя соединен с вторым входом элемента И блока анализа множителя. инверсный выход старщего разряда первой группы регистра множителя соединен с (М+ 4)-м весовым входом первого сумматора двухрядного кода первого уровня, выход старшего разряда (i + 1)-и группы разрядов регистра множителя соединен с первьй входом первого элемента И j -го элемента 2И-ИЛИ первой группы блока анализа множителя, с первыми входами полу3

сумматоров (i + 1)-й группы блока формирования кратньк множимого и с (2 А 1)-м весовым входом i/В -го сумматора двухрядного кода первого уровня, инверсный выход старшего разряда ( 1 + 1)-й группы регистра 4ножителя соединен с первым входом второго элемента И -го элемента 2И-ИЖ первой группы блока анализа множителя и с (М + 2 + 2)-м весовь1м входом i сумматора двухрядного кода первого уровня, выход второго разряда (i 1)-й группы разрядов регистра мнотгителя соединен с вторым входом второго элемента И 4-го элемента 2И-ИЛИ первой гр5гппы блока анализа множителя и с первым входом первого элемента И 1-го элемента 2И-ШШ второй группы блока анализа множителя, инверсный выход второго разряда (i « 1)-й груп пы регистра множителя соединен с вторым входом первого элемента И 4-го элемента 2И-ИЛИ первой групгал блока анализа множителя и с первым входом второго элемента И i -го элемента 2И-Ш1И второй группы блока анализа множителя, выход младшего разряда (i + 1)-й группы регистра множителя соединен с третьим входом второго элемента И f -го элемента первой группы блока анализа множителя и с вторым входом второго элемента И ( -го элемента 2И-Ш1И втрой группы блока анализа множителя инверсный выход младшего разряда (I + 1)-й группы регистра множителя соединен с третьим входом первого элемента И -го элемента 2И-ИЛИ певой группы блока анализа множителя и с вторым входом первого элемента И 4 -го элемента 2И-ИЛИ второй группы блока анализа множителя, первый вход первого элемента И каждой группы блока формирования кратных множимого соединен с W -м разрядом регистра множимого, первый вход .второго элемента И каждой группы блока формирования кратных множимого соединен с первым разрядом регистра мн жимого, первые входы первого элемента И и К -го элемента 2И-ИЛИ каждой группы блока формирования кратных множимого соединен с (К+ 1)-м выходом регистра множимого ( 1, 2, ,.., М- 1), первый вход второго элемента И К -го элемента 2И-ИЛИ ка дои группы блока формирования кратных множимого соединен с -м выхо

349344

дом регистра множимого, прямой выход младшего разряда первой группы регистра множителя соединен с вторыми входами первых элементов И элементов 2К-ИЛИ и второго элемента И первой группы блока формирования кратных множимого, выход элемента И блока анализа множителя соединен с вторыми входами вторых элементов И

0 элементов 2И-ИПИ и первого элемента И первой группы блока формирования кратньк множимого, выход ч -го элемента 2И-ИЛИ первой группы блока анализа множителя соединен с вторыми входами вторых элементов И элементов 2И-Ш1И и первого элемента И (i + 1)-й группы блока формирования кратных множимого, выход t -го элемента 2И-ИПИ второй группы блока

0 анализа множителя соединен с вторыми входами первых элементов И элементов 2И-ИЛИ и второго элемента И (i +1)-й группы блока формирования кратных множимого, выходы первого и второго

5 элементов И i -и группы которого соединены соответственно с вторыми входами (М+ 1)-го и первого полусумматоров ч -и группы блока формирования кратных множимого, выход

Q |(-го элемента 2И-ИЛИ i -и группы которого соединен с вторым входом (К + 1)-го полусумматора i -и группы блока формирования кратных множимого, выход р -го полусумматора i -и группы которого соединен с (2i + р + р - 2)-м весовым входом л/ |-го сумматора двухрядного кода первого уровня (р 1, 2, ...,М+ 1), шина логической единицы устройства соедиQ нена с (М 2 + 3)-ми весовыми входами i сумматора двухрядного кода первого уровня, выходы суммы и переноса N/2E сумматоров двухрядного кода первого уровня соединены с

5 соответствуюр ими разрядными входами регистров суммы и переноса блока регистров первого уровня соответственно, выходы разрядов регистра множимого соединены соответственно с разрядными входами второго регистра множимого, выходыJ N/Е ре- гистров суммы и переноса блока регистров первого уровня соединены с соответствующими весовыми входами

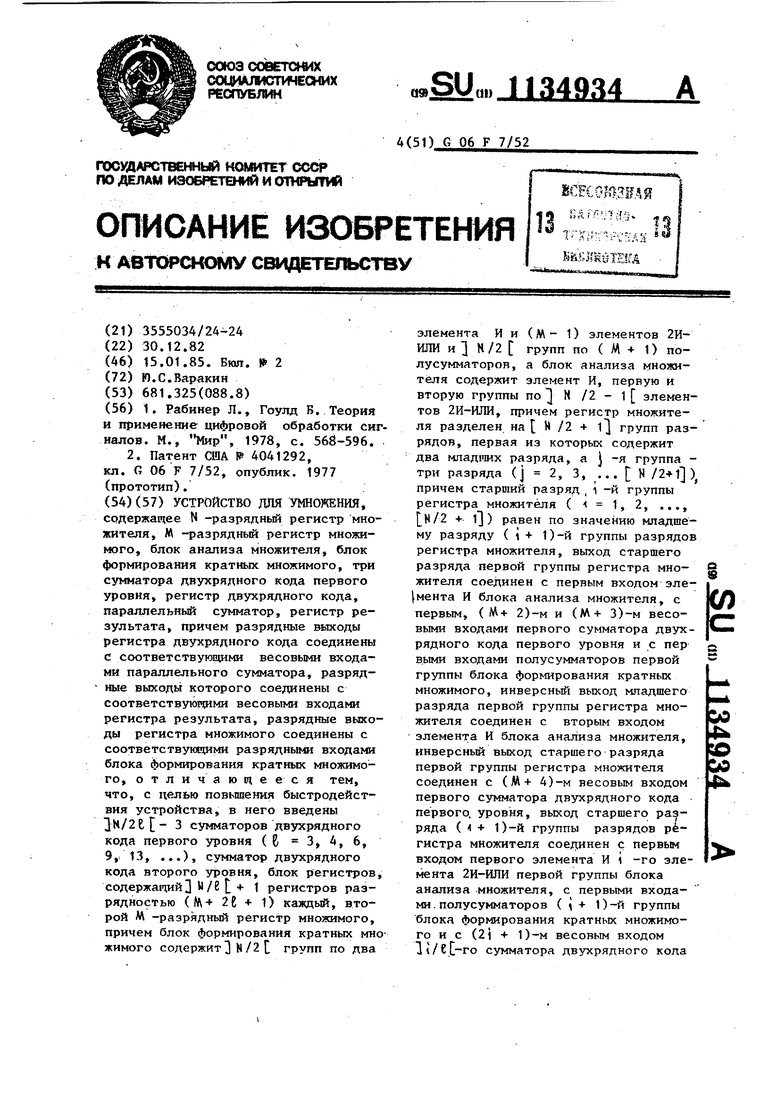

5 сумматора двухрядного кода второго уровня, q -и выход второго регистра множимого соединен соответственно с ( Я-к - 1)-м весовым разрядом сумматора двухрядного кода второго уро ня (с) 1, 2,...„,М), управляющие входы регистров соединены с входом синхронизации устройства, i На фиг о 1 представлена структурная схема устройства для умножения; на фиг. 2 - схема блока анализа разрядов множителя; на фиг. 3 - схе ма блока формирования кратных множимого; на фиг. 4 - группы разрядов множителя, анализируемые в блоке анализа разрядов множителя; на фиг. 5 - получение результата умножения ,путем суммирования 24 кратных множимого,, полученных из анализа разрядов 48-разрядного множителя и числа, равного значению самого множимого, на фиг. 6 - первый сумматор двухрядного кода первого уровня; на фиг. 7 - результаты суммирования на сумматорах двухрядного кода первог о уровня и значения регистра множимог Устройство -содержит регистр 1 мн жителя, регистр 2 множимого, блок 3 анализа разрядов множителя, блок 4 формирования кратных множимого, бло 5 сумматоров двухрядного кода перво го уровня, в который входят три сумматора двухрядного кода, блок 6 регистров (первого уровня), сумматор 7 двухрядного кода второго уровня, два регистра второго уровня составляют регистр двухрядного кода 8, параллельный сумматор 9, регистр 10 результата. Блок 3 анализа разрядов множителя содержит элемент И 3-1, первую труппу элементов 2И-ИЛИ 3-2 и 3-3 и вторую группу элементов 2И-ИЛИ 3 4 и 3-5, формирую1цие управляющие сигналы СД и НСЛ. В случае нормализованного значения множителя старши разряд равен единице и элемент 2ИИЛИ 3-3 вьфбждается в двухвходовой элемент И. Влок 4 формирования кратных множимого содержит группы элементов И 4-1 - 4-6, элементов 2И-ИЛИ 4-7 4-12 и группы полусумматоров 4-13 4-16, 4-17. 4-20, 4-21, 4-24. В случае нормализованного значения множителя старший его разряд равен едини1(е. При этом сигнал ПП24 равен единице, что позволяет исклю-чить группу полусумматоров для последнего кратного множимого, заменив их инверторами. Деление множителя на группы производится следуюи им образом: первая группа состоит из двух младших разрядов, остальные группы состоят из трех разрядов,причем младший разряд последующей группы разрядов множителя совпадает со старшим разрядом предьщущей группы. Если в старшей группе разрядов множителя получается меньше трех разрядов, то значения недостающих до трех разрядов приравниваются к нулю. Если разряды множителя пронумеровать с 1-го по 48-й, то логические функции управляющих сигналов НСД, СД и ПП.имеют вид: НСД1 48р СД1 47р, 48р ПП1 47р НСД2 46р 47 р СЛ2 45 р 46 р 47 р + 45 j 46 р 47р ПП2 45р НСД24 + 2р 3р СД24 1р. 2р. Зр + 1р 2р Зр ПП24 1рI / г Необходимо отметить, что для случая нечетного количества разрядов в множителе множимое, как дополнительное слагаемое, не учитывается. Перед старшими разрядами первого кратного множимого формируются три дополнительных разряда, роль которых выполняет код наличия сигнала прямой передачи (без сдвига) кратного множимого ПП1 (старший разряд равен ПП1, средний и младший равны ПП1). В случае прямой передачи кратного множимого П1Т1 1. Остальные кратные множимого имеют по два дополнительных разряда (старший тредставляет собой 1, а младший сигнал равен ПП;, где i 2, 3, ... N/2). К младшему разряду каждого кратного множимого при суммировании прибавляется сигнал ПП;, где i 1,2,..., , N/2, выполняющий роль единицы при образовании дополнительного кода. Общее количество суммируемых кратных множимого, ра.яНое N/2, разбивается на группы по t слагаемых, где 6 равно 3, 4, 6, 9, 13, ..., т.е.максимальное количество .слагаемых, которые можно просум в1ровать на 1, 2, 3, 4, 5 и т.д. слоях одноразрядных трехвходовых сумматоров соответственно, из которых состоят сумматоры двухрядного кода первого уровня.

В конкретном случае для М 48 выбрано равным шести.

Сумматор 5 первого уровня состоит из трёхвходовых одноразрядных сумматоров, на входы которых подаются соответствукщие весовые разряды шести кратных множимого и код ПП, . JJfin упрощения схемы сумматора двухрядкого кода первого уровня сигнал 1ШЗ запоминает на отдельном триггере или на дополнительном разряде регистра переноса или суммы, которые суммируются далее на сумматоре двухрядКо;го кода второго уровня.

Устройство позволяет реализовать конвейерный способ умножения путем подачи соответствующей серии синхроимпульсов и новых сомножителей.

Работа устройства при перемножении 48-разрядных кодов множимого и множителя, равных О,tlOOO...00, происходит следукяцим образом.

По первому тактовому импульсу, поступающему из блока синхронизации ЦВМ, разряды множителя записываются в регисдр t множителя, а разряды множимого - в регистр 2 множимого

Блок анализа разрядов множителя формирует для каждого кратного три управляющих сигнала НСД, СД и ШТ. При коде множителя 1100...00 сигналы НСД1- НСД23, СД1 - СД23, ПП1 ПП23 имеют нулевое значение.

В результате на выходах элементов И и логических узлов И-ИЛИ для йрат ных множимого (с 1-го по 23-й) фор-, мируетсянулевой код, который по сигналу ПП1 - ПП23 без сдвига передается через полусумматор, соответствующий кратньм множимому с чисел с 1-го-по 23-й. Таким образом, с учетом знаковых разрядов на 1-й сумматор t-ro уровня поступают следующие слагаемые:

1000 ... 000 1100 .„. 000 1100 ... 000 1100 ... 000 1100 .,,,000 t100 ... 000

5 1111111110 ....... 000

. р 0000000010, 000

На 2-й и 3-й сумматоры двухрядного кода 1-го уровня поступают следующие слагаемые:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1123031A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1989 |

|

SU1654815A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1741128A1 |

| Устройство для умножения | 1989 |

|

SU1658148A1 |

УСТРОЙСТВО ДЛЯ УШОЖЕНИЯ, содержащее N -разрядный регистр множителя, М -разрядньй регистр множимого, блок анализа множителя, блок формирования кратных множимого, три сумматора двухрядного кода первого уровня, регистр двухрядного кода, параллельный суьжатор, регистр результата, причем разрядные и та:оды регистра двухрядного кода соединены с соответствующими весовыми входами параллельного сумматора, разрядные выходы которого соединены с соответствующими весовыми входами регистра результата, разрядные выходы регистра множимого соединены с соответствующими разряднь да входами блока формирования кратных множимого, отличающееся тем, что, с целью повьш1е тя быстродействия устройства, в него введены ЗН/2Ь - 3 сумматоров двухрядного кода первого уровня

5 Р

Так как сигналы НСЛ24 и Ш124 равны единице, то 24-е кратное множимого формируется путем передачи кода множимого без сдвига через элементы И и логические узлы И-ИЛИ 4-5,4-6,4-11,4-12 и преобразования его в обратный код на полусумматорах 4-21 - 4-24 ,

1 1000000000. . .000 11000000000. ..000 000000000. . .000

1 1

1 1 000000000 1000000000. . 0011111111..

О

1 00 11 0000000 1 100111111100

1110011111110

На 4-й сумматор двухрядного кода. 1-го уровня при этом поступает единичный сигнал с целью преобразования обратного кода 24-го кратного множимого в дополнительный. В результате на 4-й сумматор двухрядного кода 1-го уровня поступят следующие слагаемые : . .000 000

111

1100000000000 0100000000000

0000000000000

По второму тактовому импульсу синхронизации результаты сложе иия на сумматорах I - го уровняв двухрядном коде , а также значение множимого запоминаются

на регистрах

сумматоров уровня.

О, 1 О О 1 О О

Результат суммирования в двухрядном коде по 3-му тактовому импульсу синхронизации записывается в регистры сумматора с сохранением переносов 2-го уровня. Далее на параллельном сумматоре формируется окончательный результат суммирования и по 4-му тактовому импульсу синхронизации записывается в регистр 10 результата (фиг. 1).

В результате одновременной параллельной обработки разрядов множителя и возможности организации конвейерной обработки устройство обесДалее результаты сумматоров двухрядного кода первого уровня и код множимого подаются на соответствующие весовые входы сумматора двухрядного кода второго уровня (фиг. 8).

После сложения кодов имеем следующий результат:

О

печивает более высокую производительность по сравнению с прототипом.

Базовым объектом для изобретения является арифметическое устройство многопроцессорного вычислительного комплекса Эльбрус. Умножение 32разрядных чисел в конвейерном режиме осуществляется здесь со скоростью одной пары операндов за три такта.

В данном устройстве 48-разрядные операнды обрабатываются в конвейерном режиме со скоростью одной пары операндов за один такт, т.е. в три раза быстрее при одинаковых затратах оборудования.

Фиг. 2

I I I I.Mr

1 i XTI , fii /1

i,tjjj - IlVi

2 гр23гр22гр

iHTTrrr

Фиг. Змаиение мможимобо

грЗгр2гр1гр

r 2mmfff7 f-8 разрядов Результаты сло кении шести (соотнл/ fiHOfffufiOMy чисел д двухрядном коде

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| М., Мир, 1978, с | |||

| Нефтяная топка для комнатных печей | 1923 |

|

SU568A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4041292, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-15—Публикация

1982-12-30—Подача