1lA

Изобретение относится к цифровой вычислительной технике и.может быть ис гользовано для контроля обмена вычнслг;тельных систем с магистральной

oprai-yHsaujiefl интерфейса,

ЦелгзЮ изобретения является нокышениа достоверности кси -роля ,

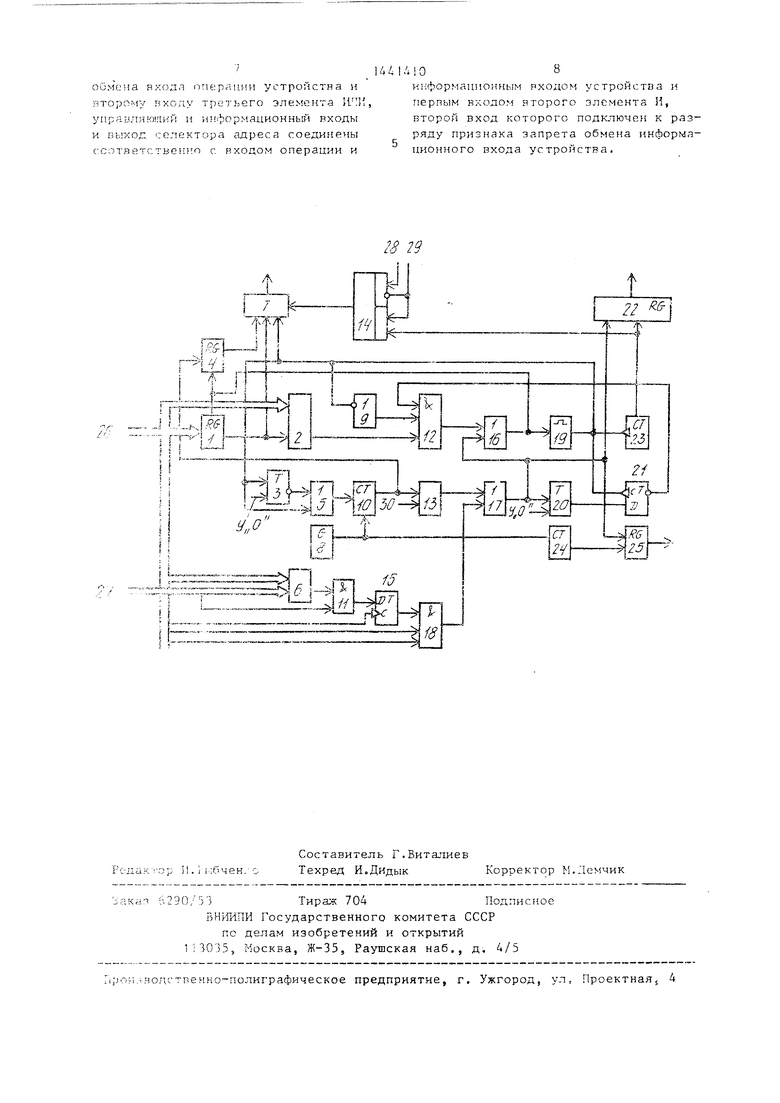

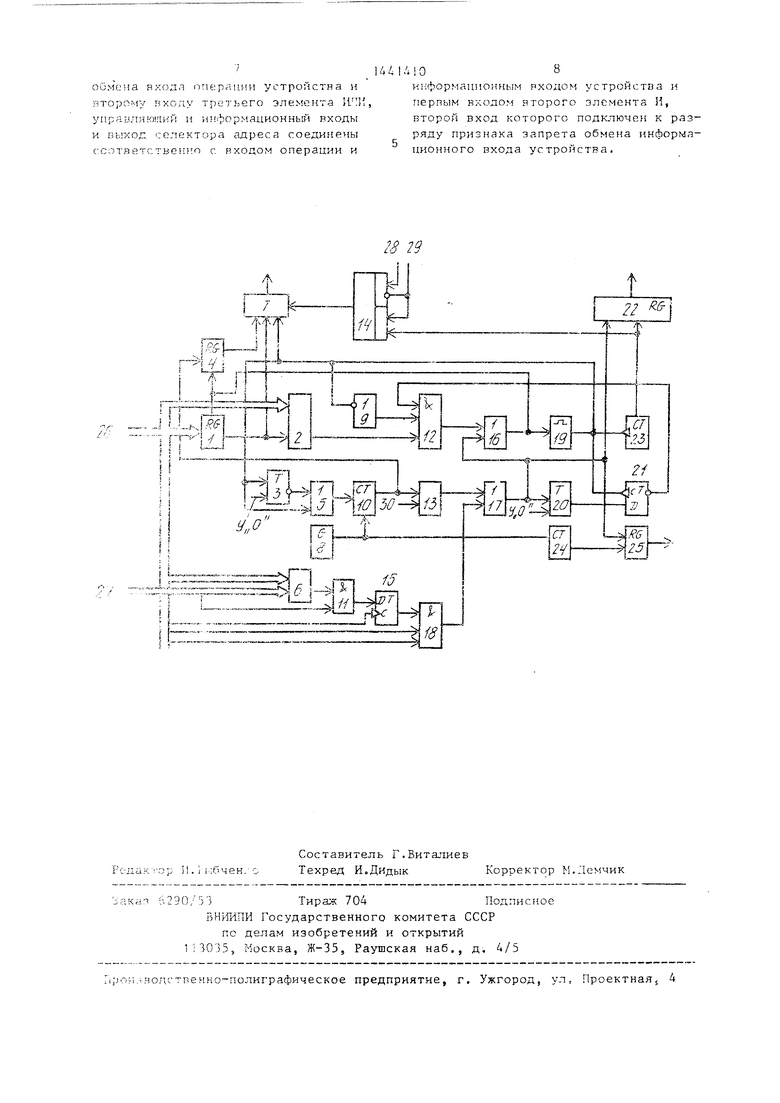

На чертеже предста--1лена структур- ь. ая схема устройства.

Устройство содержит регистр i сос- интерфейса, схему 2 сравнения триггер 3, регистр 4 интервалов времени, элемент 1ШН 5, селектор 6 адреса, блок 7 памяти, генератор 8, эле- мент НЕ 9, таймер 10, элемент И I, э. М 2, схему -13 сравнения, коммутатор 14 ап,реса. D-триггер 15, элеме -1ть ИЛИ 16, 17, элемент И 18, одновибратор 19, триггер 20, D-триг- гер 2, регистр 22 адреса останова, счет г-- К .23 адреса, счет -;ик 24 временных интервалов 5 periicTp 25 времени ocraHCiBas вход 26 операции, и гформа- шопный вход 27, адресный вход. 28, вход 29 задания режима, вход 30 конс- laiiTbb Выходы регистров 22, 25 и блока 7 гшмяти являются выходами устройства .

Выход регистра ; состояния интерфейса связан :: одним КЗ входов схемь; 2 сраы-гения ,; из иь формаиион- ных входов 6: :ока 7 памяти. Другой вход схемы 2 нодк. к входу 26 операции Выход 2 сравнения нодкхи очен к одному из входов элемента И 12; вход которого соединен с инверсным выходом триггера 2. Вькод элемента И 2 связан с одним ня Бкодон элемента 16,, Вькод псследнегэ соеди-нен с синхровходом регистра , си гхропходом регистра 4 интервалов времени и входом охтновибра

тора

:5ыход о д н ов и о р а то ра

связан с J-входом триггера 21, входом счетчика 23, входо.) элемента ME 9, выход которого подк.лючен к входу элемента И 2, установочному входу триггера 3 и из входон элемеь та 5, Лругой вход элемента ИЛИ 5 соединен с тпшерсным выходом триггера 3. Выход элемента ИЛИ 5 подключен к 1зходу с:броса таймера 0. Входы таймера 0 и счетчика 24 соединены с выходом ге ератора 8, Выход таймера 10 связан с входом рег истра 4, выход которого соязан с информационным входом блока 7 памяти и одним из зходов схемы 3 сравнен1 я Лрут-ой

1П

иояа и 25 к;-;еме ;; ::-( - - - Еход злемен а -7 :f.::. -. дом элемента И ь, (VIMH ич з:1еме(та И 8 ::Сли . :;очс ; ; чалроса обмена пход; ; }.. ; : г Другой вход - к разр;т у обмена нх(1д;: 26 yi-7 p - вход sneNieHT,- ; I :;о;:,; ;:;::. :;.;

ДУ П-)рИГГ:. ра У;. lI-iM:- ::,,.

26 устройсттза. Олии ;-;:; r;-::v: i И 1 1 )1 :: рГ: 37 1;;г:; ха заг;1ета обмен;; jvx;;;:;; 2 на. Лругой яхол -j r-Nrejira ; нен с ;: .ходо;. TOI;;J 6 -;: - ирааляюший вход cj:eK ; (.п-

иоДКЛ ОЧеН к входу 26 .

формационньгй - к ,- ройства, Выхо,;, счетч;;ха : с ииформанио;{ :ым нхслом :.; -меии остягопа, - : ; aicpeCci связан с И ;::г ; ;.;:;,-:; i. дом регистра 22 ;,арс:,;-, ос :::И одмим из ;-1Н(ЬГ ПМн: н: чмь -- --ry:

ахсд коммутатора ; --, ::сг::е:; --;г;

.: : ои1ий пх;:д ком;-:;/ /ч . с аходо;.; 29 --ад-. .- ва. Выход ,-;т .:.. : ciii ресн.;м ах:..ло О.чок- .- сброса TDiirr Ci.iC., / . :: ; «ходом сбуосг yi:: - , : .

Ус 1 р : Йсти: -ir i: .. i,. У разом,

В ИСХОДн С)--: со. Г :;:: 22,25, тригг ;;ы :. .. .;.; 2 ; , 23 адреса х;:;, му.-:;- нии .

VcTpoAci BC р боглсг ;.- ;:HV мах; Контро. м/ и Bi.s;ioj: .

т - f

Контроль ocyiuecTF-. i5 f Tc : :::: состоя11Ия cHrnajK) nnrejidic-fi ; садия носледонатедь.п;.. ти ;зм- состояния и 7 ерфейса . 1 реежи: вод ос;у ществлпетг л н, ,::. ; а рованной в HpO ierce :онгродя ния интерфейса инфор; ;:ди;1 с ; щей обработкой и рг iCT;- .пгн. ном из стаьщартнмл ) :- н работь устр) 1:-тнл ::-ic:

сигиа,г1ом . пхоле 29 устроГютва, В режиме Контроль при наличии соответствующего сигнала fia входе 29 осу шествляется подключение выходов счет- шка 23 через коммутатор 1Д к адресным входам блока 7 памяти. В режиме Вывод при наличии соответствующего сигнала на входе 29 устройства обеспечивается подключение адресного входа 28 устройства через коммутатор 14 к алрескъ;м входам блока 7 памяти.

В ре,-име Контроль сигналы интер- и :ейск с входа 26 поступают яа входы регистра у. схемы 2 сравнения. Пос1 оотсулен. то при появлении на входе - j устройства сигиа/.ов интерфейса на 1;ь;ходе cxeNn.n 2 сраззтения гоявляется : разj;С:;; i uaiH cnrHajT, посту- :: Л01ДИЙ на вхо;: элемента 12, Так как г, лсходном со-токлин триггер 21 обну- лек и ;;а его инперсно;- вькоце лрисут- ст;,ует е.пи и:иый р;;зрешакз:щ;й сиг11ал, f.i cH.: ::-3ji л.апуска одиовибратора 19 от- с;утс гйуст ir.e. на вьгходе элемента 1:Г: 9 присутствует едизшчный ра:1рс:;,; :о;11.ий ( мл;ал)) на выходе эле- :-;л:-;т 1 2 Ор - ; рУ - : с : единичный пазреii :-4.-i: :-..., ., };а зход :;..;;;, :чнт - ib. . л ;-:;;;;иом состояг ии L : i-;rrep 3 о5;{у;-с ; и на его инверсном ; T :oz;o лг ис утсгвует единич;-1ый сигнал ;;:т;дг-;г. ;ход э.пемента 5 и да- -е : ,i . :;ход сброса таймера 10, удер- -лпая с Г я ;к;ход.ом положении. Пуле- коп с :- :: Ла тайь ера 0 поступает на Dxcii ске -ъ :3 сра} нения, на другом входе которой присутствует код константы ;5 гсзу: ьтате ;1О}{ --я находит r narO-;iHb НС ь.

рыходе схемы 13 срав- мулевой сигнал, послы элементов 16 и 17,

а по :л:е лос уплсч рьч ЕДИНИЧНОГО сигна- ;..; с г;:;е.:рита 12 на вход элемента 16 на F-г : выходе формируется е ИН :л}{Ь й (игиал. По переднему фронту cHrti;ij;a с рыхода элемента 16 В ре- Г истре 1 ф -;ксл ,-уется состояние сигна- л .-. инте;:1фе;;г,ч, на входе 26 устройст- ;:. , а в peiM -Tp-p - код на выходе 10 I, и ;; ai чом случае нулевой :од) , Кроме то:-(;. по сигналу с выхода ,. у,ес.твляется запуск од- ;- , ллсле чего на выхо- ь Пг нения формируется ну 1: сигналу с выхода од- ; Of уществ:;яется за;. - ВэКОДОН реГИСТрОБ

I и 4 по адресу, определяемому счетчиком 23, а на выходе элемента 9 появляется сигнал, блокирующий появление на выходе элемента 12 на время цикла записи в блок 7 памяти. По зaднe o фронту сигнала с выхода одновибратора 19 осуществляется модификация счетчика 23 адреса и запись состояния триггера 20 в триггер 21 .

5

0

5

5

0

5

5

риг гер 21 подтверждает свое исходное состояние, а ;а его инвер ном вьзходе сохраняется единиЧ1-1ый . Кроме тог-о. по сигнал: с выходо одновибраторт 19 устанавливается триггер 3. На его и;;- версипм -ыхода появляется г улевсй сигнал, подключающий - ход сброса таймера 10 через элеметтт 5 к Кмгхоя/ од- новибратоса 19, Ггоскольку в этот момент BpeM.e riM на выходе од -;от-,ибратора 19 присутствует елчничнь сигнал, таймер 1C лродол7;а-зт уД рхпг заться в 1-;сходном {ну.г;езо 0 состоян;-i-;, Тосле окончан гя сигнала на Г|-;холс одловиб- ратора 19 си1 на,п сброса с в г-ссда мсрр 10 jHHN ae-c :. При ::с еле,.; vKjpi e.-: по; улле Л и сигналов F с;-:е -чь;х меток с зь хода гошра ор.; Б 10 осу1::ест; ляет отсчет speNfCHHorc глтер- вала г Код Tcxyicci O И; тс;:зас;г. -трс че - ни с н;.:хода таймера 10 )ia вход схемы сравнения, Лг:: отсутствии сигна ла на вь;ходе схе;-го ;3 сравнения у сзидетельствуюаего об оконча)-. до- rrycTHhioro интервала 5pcN:eK i, г при измененли состояния сигл ;т;ов .:& входе 26 с тройства на зьг. 2 сразнеиия появ::лется од; лгилный сиг - нап, постулаюпил; на вхог зле гентя 12Если в прО ;ессе обме: а в Te ier-n-iE интервала , зад,ан;:ого лри ло- МО1ЦИ константь на входе 30, состояние сигналов интерфейса ля входе 26 устройства не изменяется, то после поступления очередного сигнала с выхода генератора 8 код };а выходе таймера 10 становится значению константы на входе 30 и :-ia зъкоде схемь; 13 сравнения формируется единичный сигнал, постулшои .итй на вход элемента 17. На выходе эле. ;е;1та i появляется сигнал, по котсм ому устанавливается триггер 20, а Е регистрах 22 и 25 фиксируете;; -:uipec ячейки блока 7 памяти в момент останова и

премн останова соогветег: нал с 1;ь;хода элемента i / также на вход sjieMesrra ii На выходе элемент iб С;1Г: ал- соотватст яи) : Раг яс грГ; i фиксируатпл с( налов ;;i-rreprSe: ca ня вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интерфейса ввода-вывода | 1988 |

|

SU1674140A2 |

| Устройство для контроля интерфейса ввода-вывода | 1986 |

|

SU1383374A1 |

| Устройство для контроля интерфейса ввода-вывода | 1989 |

|

SU1649557A2 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Мультипроцессорная вычислительная система | 1988 |

|

SU1522227A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| Имитатор канала | 1984 |

|

SU1310823A2 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Устройство для сопряжения интерфейсов ввода-вывода с регистратором | 1987 |

|

SU1413636A1 |

4KN:ara ш. г.азнь: гств )Те т-с -апус

1,;:ЙС ОСуЕ ег :ЛЯ -:

содержкысг есу, огре,,.- лясмо о за,;;::,ему фронту днозмбратора 19 Фиг;г1мп-е гся пи;

ООРМИП ЯТС

,OK iDy;o;ri

:; г:.цррга ггаяп.пяатгя едк г- ЧН: , гссту:;а о ций яа пхоп е 1.3in; Hji подклю ге :--;е сг. /кгд.; :т1;ую;и го тгрнзнак 27

Г|П1 Мстз, ;сг г.п(;: i Vii: г л к::,мс1 -НЯ;. Г.; 1 ь;кодс ЭЛСМй;: а iS : ;;я еди гииный ., свинете.: ;-:г:-;й об г . осдедс;; атг.п: обмена. Kv-iTopbiH поступаег HI й.;еиеяг,я У v: формируете;: сч;: соотвегствии с которь;м з геп фиксируется код на ;ь :-:оде сч 23 в мот- П остзноза, ; ,;

) Q

ваемя

Если 3 нроцгсч;е обмена о иуу ; о I By- ет обргицение к со . тветстяующему регистру сос гоян; Л , ;:а иьп- оде селекто-- ра 6 адреса находиток ,:nof сигнал блокирук)Щ{ш устаиовху триггера i5 м

14 Д I Д о8

оимсиа рходл операции yL-тройстна и имформациоиным РХОДОМ устройства н втором-, вхолу третьего элемента , перпым входом второго элемента И, упряБ.пяюшиГ и HictJOpManHOHMbn i входы второй вход которого подключен к разряду признака запрета обмена информационного входа устройства.

и выход селектора адреса соеяине1гы с олтветствен} п с Р ХОДОМ операции и

имформациоиным РХОДОМ устройства н перпым входом второго элемента И, второй вход которого подключен к разряду признака запрета обмена информационного входа устройства.

Авторы

Даты

1988-11-30—Публикация

1986-10-21—Подача