Изобретение относится к цифровой вычислительной технике, может быть использовано для контроля ввода-вывода цифровых вычислительных машин и систем, организованных на базе МПИ, и является усовершенствованием изобретения по авт. св. № 1383374.

Цель изобретения - сокращение времени реакции на ошибки, связанные с отсутствием ответа от устройства, к которому осуществляется обращение.

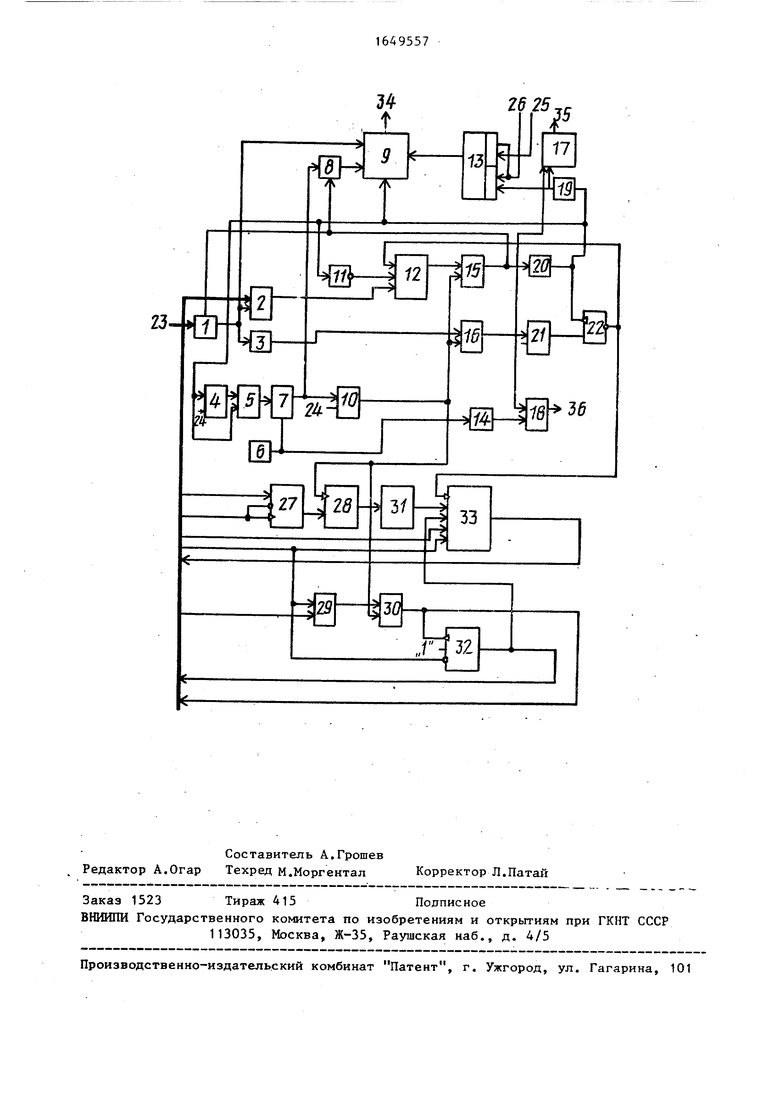

На чертеже представлена структурная схема устройства.

Устройство содержит регистр 1 состояния интерфейса, схему 2 сравнения, дешифратор 3 состояния интерфейса, триггер 4, элемент ИЛИ 5, генератор 6 импульсов, таймер 7, регистр 8 интервалов времени, блок 9 памяти, схему 10 сравнения, элемент НЕ 11, элемент И 12, коммутатор 13, таймер 14, элементы ИЛИ 15 и 16, регистры 17 и 18 адреса и времени останова соответственно, счетчик 19 адреса, одновибратор 20, триггеры 21 и 22, входы устройства информационный (23), константы времени (24), адресный (25) и признака коммутации (26), регистры 27 и 28 адреса текущего обмена, элемент И 29, триггер 30, шифратор 31, триггер 32, регистр 33

Р

u

to

и

ч

14)

вектора, а также выходы 34-36 устройства.

Устройство работает следующим образом.

В исходном состоянии регистры 1, 17, 18, 27, 28 и 33, таймеры 7 и 14, триггеры 4, 21, 22, 30 и 32 и счетчик 19 установлены в нулевое состояние (средства установки в исходное состояние на чертеже не показаны).

Устройство работает в двух режимах: Контроль и Вывод.

В режиме Контроль осуществляется

10

вом состоянии. На входе 24 присутствует константа, равная значению интервала времени, в течение которого допускается отсутствие изменения состояния сигналов интерфейса, поэтому на выходе схемы 10 сравнения находится нулевой сигнал, поступающий на входы элементов ИЛИ 15 и 16, и после поступления единичного сигнала с выхода элемента И 12 на вход элемента ПЛИ 15 на его выходе формируется единичный сигнал. По переднему фронту сигнала с выхода элемента ИЛИ 15 в

контроль состояния сигналов интерфрй- 1.5 регистре 1 фиксируется состояние сиг- са и фиксация последовательности изменения состояния сигналов интерфейса. В режиме Вывод осуществляется вывод зафиксированной в процессе контроля последовательности обработ- 20 кой и регистрацией на одном из стандартных устройств вывода. Режим работы устройства определяется сигналом на входе 26 устройства. В режиме Контроль при наличии соответст- 25 вующего сигнала на входе 26 устройства осуществляется подключение выходов счетчика 19 через коммутатор 13 к адресному входу блока 9 памяти.

налов интерфейса на входе 23 и в регистре 8 - код на выходе таймера 7 (в данном случае нулевой код), кроме того, по сигналу с выхода элемента ИЛИ 15 осуществляется запуск одновиб- ратора 20. С выхода схемы 2 сравнения снимается единичный сигнал. С выхода регистра 1 код сигналов текущего состояния интерфейса поступает на вход дешифратора 3. Если код сигналов состояния интерфейса, поступающий с выхода регистра 1, соответствует нормальной последовательности обмена, то на выходе дешифратора 3

35

40

В режиме Вывод при наличии соответ- 30 сохраняется нулевой сигнал, поступаю- ствующего сигнала на входе 26 устройства обеспечивается подключение адресного входа 25 устройства через коммутатор 13 к адресном} входу блока 9 памяти.

В режиме Контроль сигналы интерфейса с входа 23 устройства поступают на входы регистра 1 и схемы 2 сравнения.

Поскольку в исходном состоянии регистр 1 обнулен, то при появлении на входе 23 устройства сигналов интерфейса на выходе схемы 2 сравнения появляется единичный сигнал. В этот момент времени на входах дешифратора 3 присутствуют нули, а на его выходе находится нулевой сигнал. При поступлении сигнала на вход элемента И 12 на остальных его входах находятся единичные сигналы, так как в исходном состоянии триггер 22 обнулен и на его инверсном выходе присутствует единичный разрешающий сигнал, а запуск одновибратора 20 отсутствует. В результате на выходе - элемента И 12 появляется сигнал, поступающий на вход элемента ИЛИ 15, сигналом с инверсного выхода тригщий на вход элемента ИЛИ 16, на выходе которого также сохраняется нулевой сигнал,

Установка триггера 21 при этом отсутствует. По сигналу с выхода одновибратора 20 осуществляется запись информации с выходов регистра 1 и регистра 8 по адресу, предложенному счетчиком 9, а на выходе эле-- мента НЕ 11 появляется сигнал, блокирующий появление сигналов на выходе элемента И 12 на время цикла записи в блок 9 памяти. По заднему фронту сигнала с выхода одновибратора 20 45 осуществляется модификация счетчика 19 адреса и запись состояния триггера 21 в триггер 22. При отсутствии ошибки, зафиксированной триггером 21, триггер 22 подтверждает свое исходное нулевое состояние, а на его инверсном выходе сохраняется единичный сигнал. Кроме того, по переднему фронту сигнала с выхода одновибратора 20 устанавливается триггер 4. На его -инверсном выходе появляется нулевой сигнал, подключающий вход сброса таймера 7 через элемент ИЛИ 5 к выходу одновибратора 20. Поскольку на выходе одновибратора 20 присутствует

50

55

гера 4 таймер 7 удерживается в нуле

вом состоянии. На входе 24 присутствует константа, равная значению интервала времени, в течение которого допускается отсутствие изменения состояния сигналов интерфейса, поэтому на выходе схемы 10 сравнения находится нулевой сигнал, поступающий на входы элементов ИЛИ 15 и 16, и после поступления единичного сигнала с выхода элемента И 12 на вход элемента ПЛИ 15 на его выходе формируется единичный сигнал. По переднему фронту сигнала с выхода элемента ИЛИ 15 в

регистре 1 фиксируется состояние сиг

налов интерфейса на входе 23 и в регистре 8 - код на выходе таймера 7 (в данном случае нулевой код), кроме того, по сигналу с выхода элемента ИЛИ 15 осуществляется запуск одновиб ратора 20. С выхода схемы 2 сравнения снимается единичный сигнал. С выхода регистра 1 код сигналов текущего состояния интерфейса поступает на вход дешифратора 3. Если код сигналов состояния интерфейса, поступающий с выхода регистра 1, соответствует нормальной последовательности обмена, то на выходе дешифратора 3

сохраняется нулевой сигнал, поступаю-

щий на вход элемента ИЛИ 16, на выходе которого также сохраняется нулевой сигнал,

Установка триггера 21 при этом отсутствует. По сигналу с выхода одновибратора 20 осуществляется запись информации с выходов регистра 1 и регистра 8 по адресу, предложенному счетчиком 9, а на выходе эле-- мента НЕ 11 появляется сигнал, блокирующий появление сигналов на выходе элемента И 12 на время цикла записи в блок 9 памяти. По заднему фронту сигнала с выхода одновибратора 20 осуществляется модификация счетчика 19 адреса и запись состояния триггера 21 в триггер 22. При отсутствии ошибки, зафиксированной триггером 21, триггер 22 подтверждает свое исходное нулевое состояние, а на его инверсном выходе сохраняется единичный сигнал. Кроме того, по переднему фронту сигнала с выхода одновибратора 20 устанавливается триггер 4. На его -инверсном выходе появляется нулевой сигнал, подключающий вход сброса таймера 7 через элемент ИЛИ 5 к выходу одновибратора 20. Поскольку на выходе одновибратора 20 присутствует

единичный сигнал, таймер 7 удерживается в исходном нулевом состоянии. После окончания сигнала на выходе одновибратора 20 снижается сигнал с входа сброса таймера 7. При последующем поступлении сигналов временных меток с выхода генератора 6 таймер 7 осуществляет отсчет временного интервала времени. Код текущего значения интервала времени с выхода таймера 7 поступает на вход схемы Ю сравнения, при-помощи которой осуществляется сравнение его со значением константы на входе 24. При отсутствии сигнала на выходе схемы 10 сравнения, свидетельствующего об окончании допустимого интервала времени, и при изменении состояния сигналов на входе 23 устройства на выходе схемы 2 сравнения появляется единичный сигнал, поступающий на вход элемента И 12. Дальнейшая работа устройства аналогична описанному.

Если в процессе обмена при помощи регистра 1 зафиксирована комбинация сигналов интерфейса, не соответствующая нормальной последовательности, на выходе дешифратора 3 формируется сигнал ошибки, поступающий на вход элемента ИЛИ 16. На выходе элемента ИЛИ 16 формируется сигнал, в соответствии с которым осуществляются установка триггера 21, а также фиксация в регистре 17 адреса г. ячейки блока 9 памяти, в которую записывается последнее состояние сигналов интерфейса, и фиксация в регистре 18 времени останова. По заднему фронту сигнала с выхода одновибратора 20 информация с выхода триггера 21 записывается в триггер 22. На инверсном выходе триггера 22 появляется нулевой сигнал останова, блокирующий появление сигналов на выходе элемента И 12.

При появлении на соответствующей шине входа 23 сигнала ОБМ снимается сигнал обнуления с R-входа регистра 27 и осуществляется запись информации об адресе текущего цикла обмена в регистр 27 по переднему фронту сигнала ОБМ.

Если в процессе обмена в течение интервала времени, заданного при помощи константы, изменение состояния сигналов интерфейса отсутствует, то после поступления очередного сигнала с выхода генератора 6 код на выходе

5

0

0

таймера 7 становится равным значению константы на входе 24 и на выходе схемы 10 сравнения формируется единичный сигнал, поступающий на входы элементов ИЛИ 15 и 16, вход записи регистра 28 и установочный вход ,

триггера 30. На выходах элементов ИЛИ 15 и 16 формируются сигналы, по которым

0 в регистре 1 фиксируется состояние сигналов интерфейса на входе 23 устройства и осуществляется запуск одновибратора 20, а также установка .триггера 21 и т.д. в соответствии с описанным. В регистре 28 фиксируется адрес в текущем цикле обмена, в котором зафиксировано отсутствие изменения состояния интерфейса в течение интервала времени, заданного при помощи константы на входе 24 устройства. На входе регистра 28 появляется код, соответствующий коду адреса в текущем цикле обмена. С выходов регистра 28 информация поступает на вход шифратора 31. Шифратор 31 преобразует код адреса текущего цикла обмена в код, определяющий старшие разряды адреса вектора прерывания. С вывода шифратора 31 сформированный код поступает на вход регистра 33. Кроме того, iia входы регистра 33 поступают сигналы, соответствующие направлению подачи информации (ДЗП и ДЧТ) и определяющие младшие разряды адреса векто5 ра прерывания. Кроме того, по сигналу с выхода схемы 10 сравнения

осуществляется установка триггера 30. Сигнал запроса прерывания с выхода триггера 30 поступает на вход 23 и

0 далее на вход процессора системы, к шине которой подключено данное устройство. С входа 23 на выходы элемента И 29 поступают сигналы ПРР и ДЧТ, свидетельствующие о выпол5 нении цикла обмена, связанного с обработкой запроса прерывания, формируемого при помощи триггера 30. На выходе элемента И 29 формируется сигнал, поступающий на вход сброса триг0 гера 30. В результате сигнал запроса прерывания с выхода триггера 30 и далее на входе 23 снимается.. По заднему фронту сигнала на выходе триггера 30 устанавливается триггер 32.

5 Сигнал ОТВ с выхода триггера 32 поступает на вход 23 и управляющий вход регистра 33. В результате выходы регистра 33 подключаются к входу 23 устройства.-После поступления сиг

нала ОТВ, свидетельствующего о поступлении адреса вектора прерывания и приеме адреса вектора прерывания, процессор снимает на входе 23 сигналы ППР и ДЧТ. В результате снимается сигнал с входа сброса триггера 30 и сбрасывается триггер 32, Цикл передачи адреса вектора прерывания, содержащего информацию об адресе и направлении передачи в цикле обмена, во время которого зафиксировано отсутствие изменения состояния интерфейса в течение интервала времени, заданного при помощи константы на входе 24, закончился.

В режиме Вывод в соответствии с сигналом на входе 26 устройства осуществляется подключение адресного входа 25 устройства к адресному входу блока 9 памяти. Далее осуществляется считывание ячеек блока 9 памяти по адресам, поступающим с адресного входа 25 устройства, для последующей обработки и регистрации.

Формула изобретения

Устройство для контроля интерфейса ввода-вывода по авт. св. № 1 383374, отличающеес я тем, что, с целью сокращения времени реакции на ошибки, связанные с отсутствием ответа от устройства к которому осуществляется обращение, в него введены второй и третий регистры адреса, регистр вектора, четвертый и пятый триггеры и второй элемент И, причем информационный вхо I

второго регистра адреса соединен с информационным входом устройства, вход сброса и вход синхронизации второго регистра адреса соединены с шиной сброса и синхронизации обмена устройства, выход второго регистра адреса соединен с информационным входом третьего регистра адреса, син- хровход которого соединен с выходом второй схемы сравнения, а выход соединен с входом шифратора, выход шифратора соединен с группой старших разрядов информационного входа ре- гистра вектора, а группа младших разрядов информационного входа регистра вектора соединена с входными шинами записи данных и чтения данных устройства, вход синхронизации регистра вектора соединен с выходом первого триггера, а вход чтения - с выходом четвертого триггера и является выходом ответа устройства, выход регистра вектора является выходом вектора прерывания устройства, первый вход второго элемента И соединен с входной шиной чтения .данных устройства и с входом сброса четвертого триггера, второй вход второго элемента И соединен с входной шиной разрешения прерывания устройства, выход второго элемента И соединен с входом сброса пятого триггера, вход установки которого соединен с выходом второй схемы сравнения, выход пятого триггера соединен с входом синхронизации четвертого триггера и является выходом запроса на прерывание устройства.

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интерфейса ввода-вывода | 1988 |

|

SU1674140A2 |

| Устройство для контроля интерфейса ввода-вывода | 1986 |

|

SU1383374A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Устройство для контроля интерфейса ввода-вывода | 1991 |

|

SU1798792A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

Изобретение относится к цифровой вычислительной технике, может быть использовано дпя контроля ввода- вывода цифровых вычислительных машин и систем, организованных на базе МПИ, и является усовершенствованием изобретения по авт. св. № 1383374. Печь изобретения - сокращение времени реакции на ошибки, связанные с отсутствием ответа от устройства, к которому осуществляется обращение, за счет формирования по результатам контроля состояния интерфейса вектора прерывания и передачи его к центральному процессору контролируемой системы. Устройство содержит регистр состояния интерфейса, три регистра ацреса, регистр времени останова, блок памяти, два таймера, две схемы сравнения, счетчик адреса, коммутатор, гечерат-ор импульсов, регистр интервалов времени, элемент НЕ, два элемента И, три элемента ИЛИ, пять триггеров, дешифратор состояния интерфейса, регистр вектора, шифратор. 1 ил. 3 (Л

| Устройство для контроля интерфейса ввода-вывода | 1986 |

|

SU1383374A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1989-05-03—Подача