Э

01 rsS

ю

N9

Ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоуровневая подсистема обработки прерываний | 1988 |

|

SU1624448A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Процессор для мультипроцессорной системы | 1988 |

|

SU1541626A1 |

| Процессор программируемого контроллера | 1984 |

|

SU1269150A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

Изобретение относится к вычислительной технике и может быть использовано при построении мультипроцессорных систем повышенной надежности. Целью изобретения является повышение надежности системы за счет организации следящего контроля выполнения системных операций, запоминания предыстории использования общих ресурсов системы на фиксированное число системных циклов и дальнейшей ее обработки для выбора оптимальнойц стратегии поведения системы после сбоев и отказов. Поставленная цель достигается тем, что в систему, содержащую главный процессор 1, N исполнительных процессоров 21....2N, запоминающее устройство 3, введены блок управления общими ресурсами 4 и блок защиты 6. 12 ил.

4

W

Jn

Изобретение относится к вычисительной технике и мож ет быть испольовано при построений мультипроцессорных снстем повышенной надежности.

Целью изобретения является повыше- не надежности системы за счет орга- нэации следящего контроля выполнения системных операций, запоминания предстории использования общих ресурсов системы на фиксированное число системных циклов и дальнейшей ее обработки для выбора оптимальной страте гии поведения.системы после сбоев и отказов.

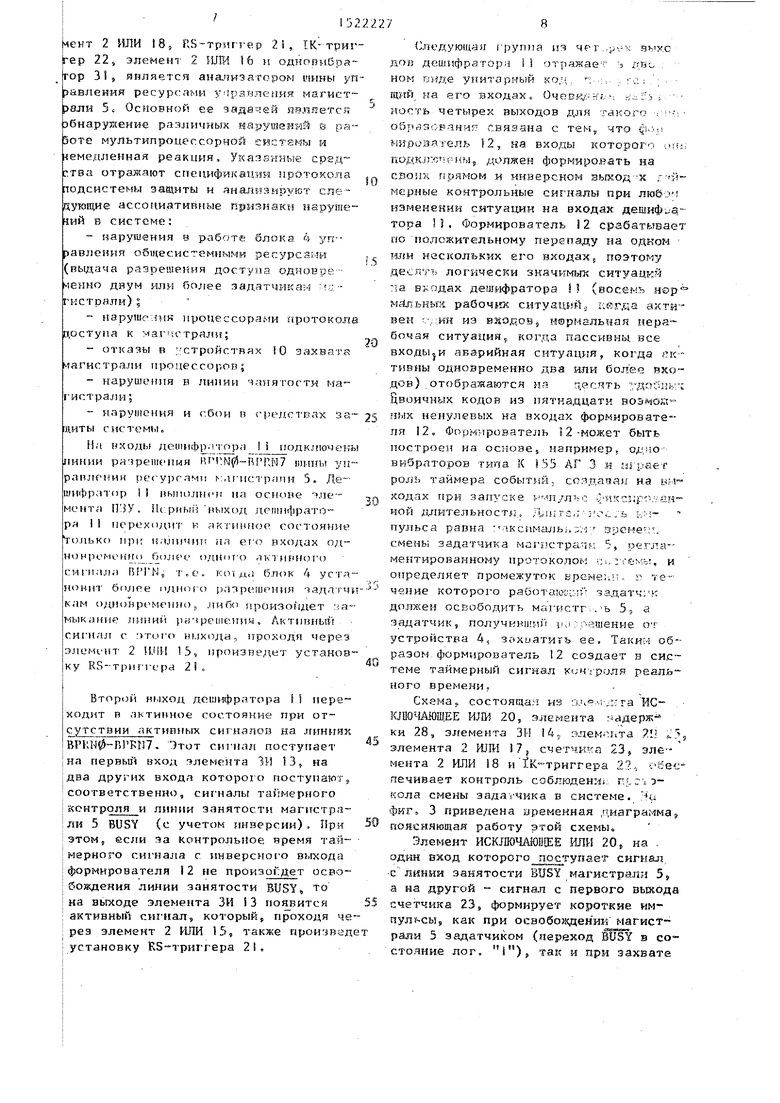

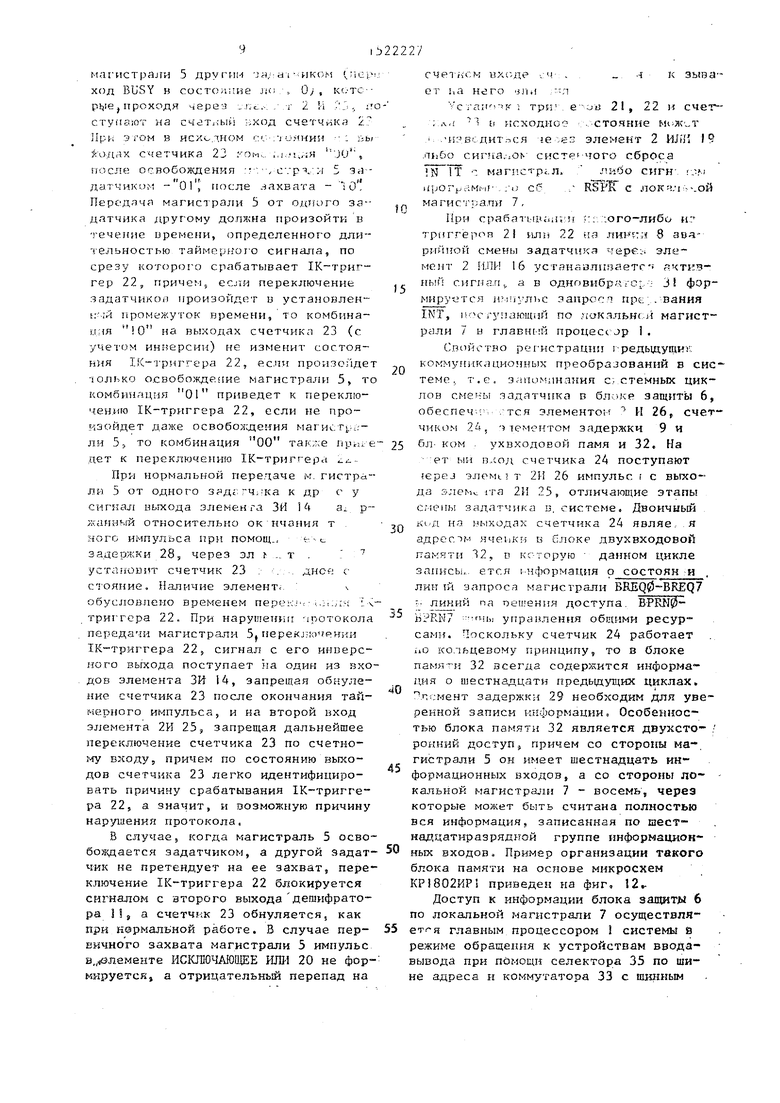

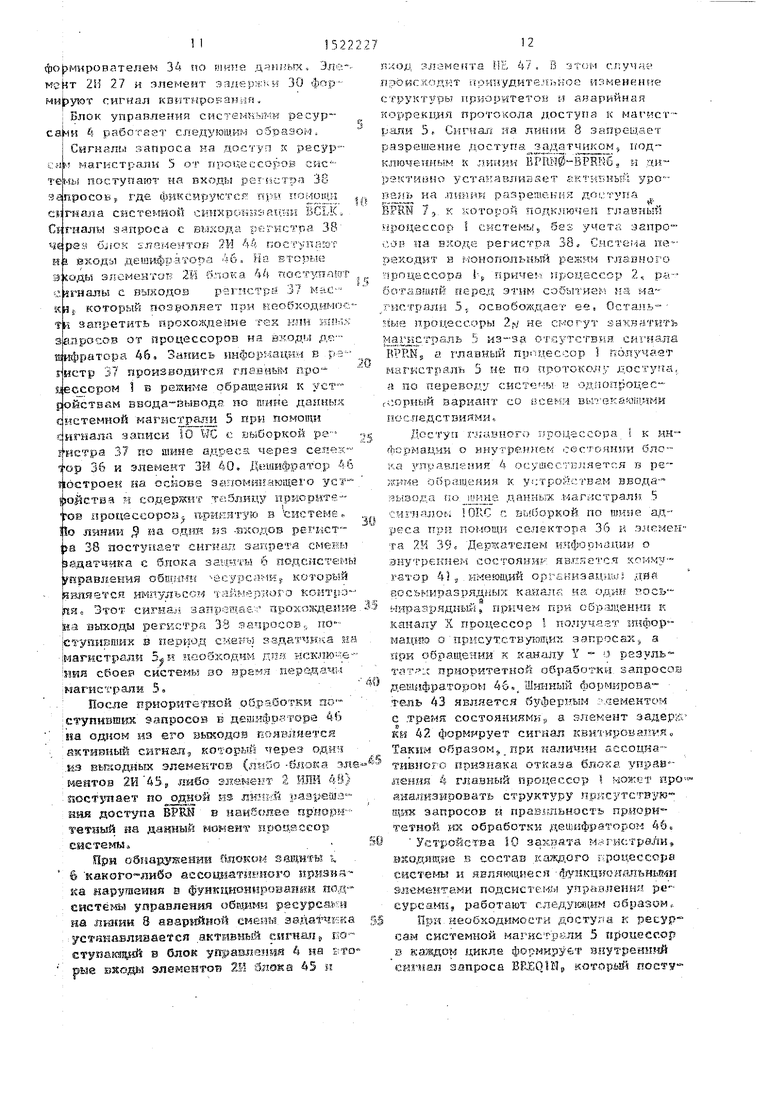

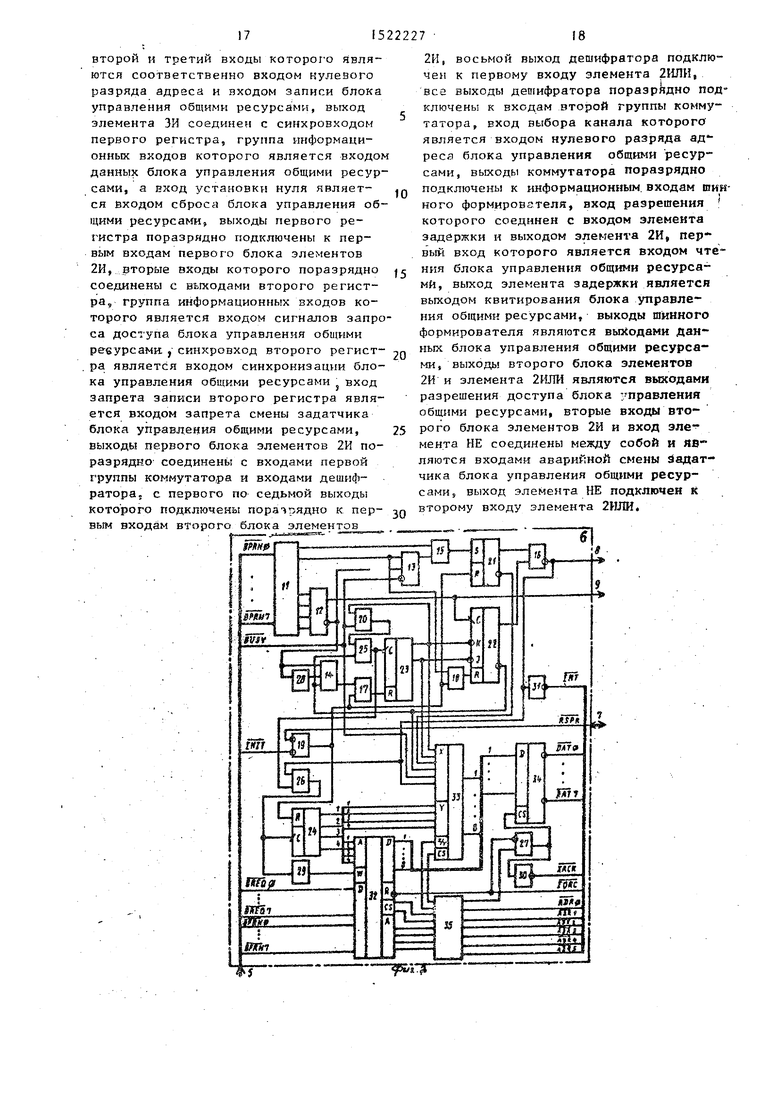

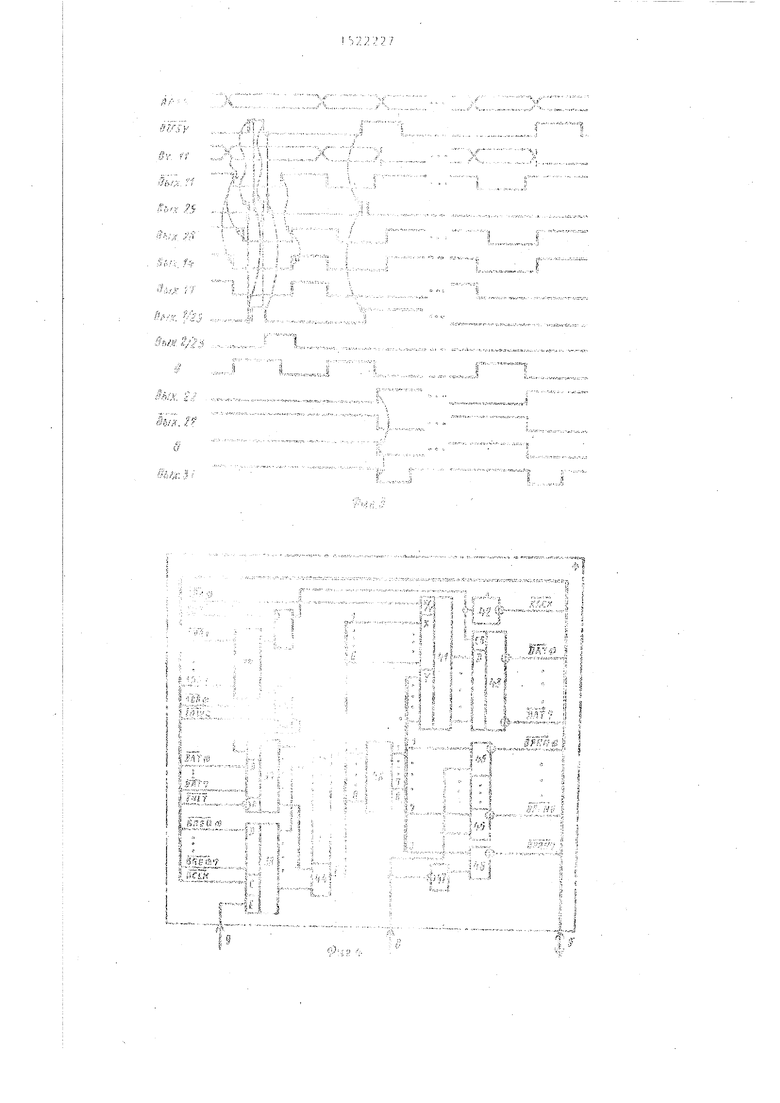

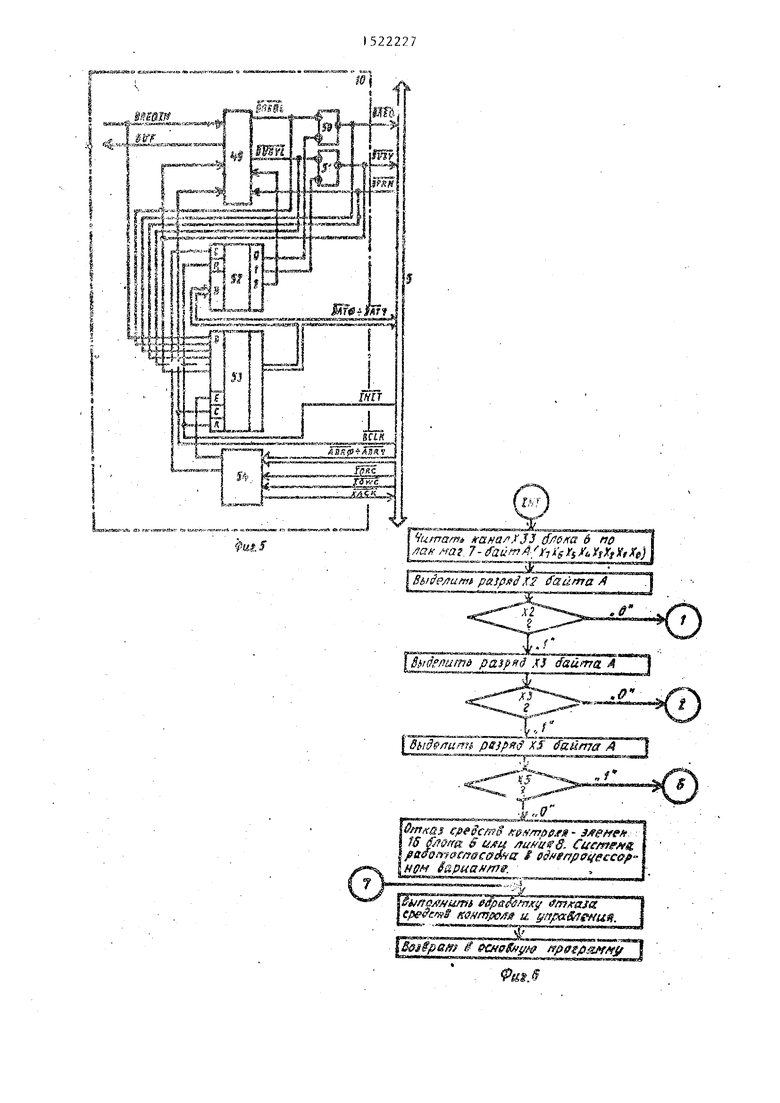

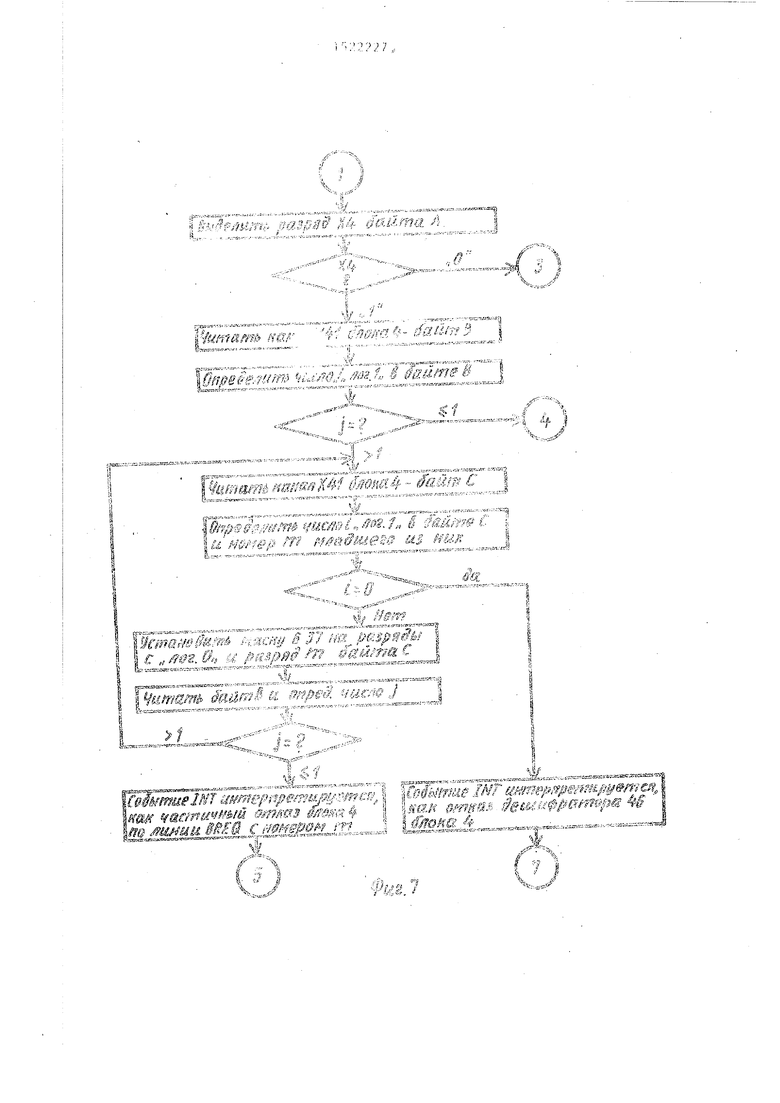

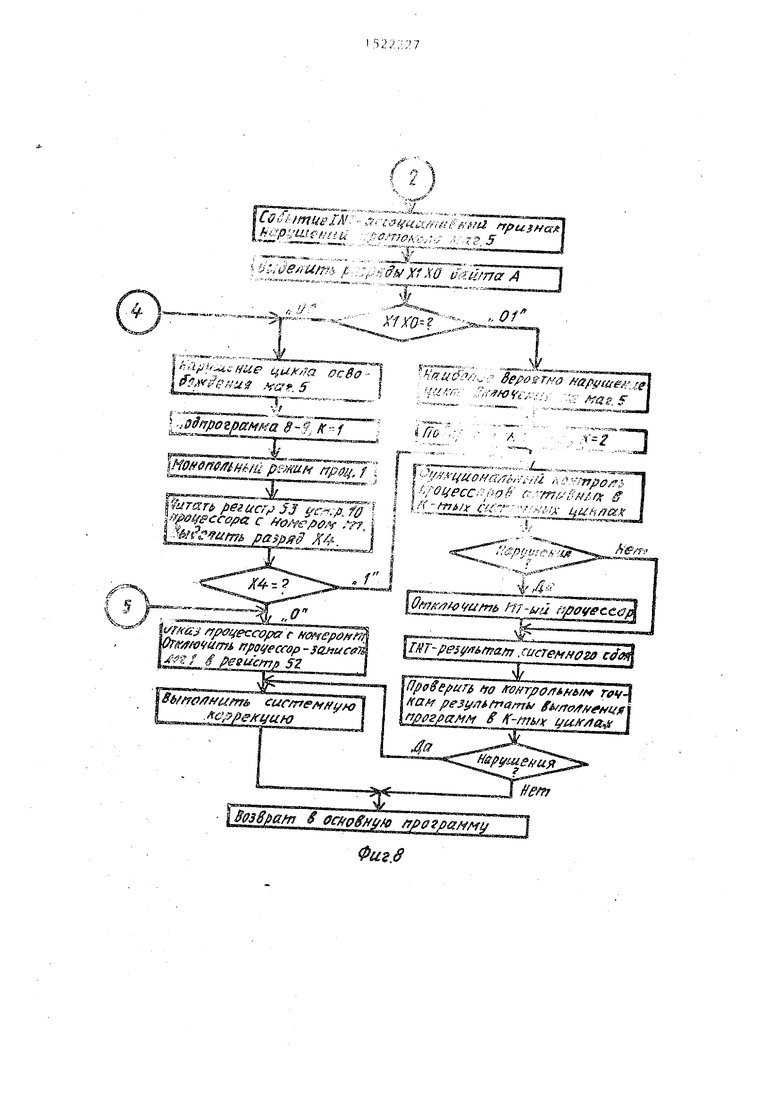

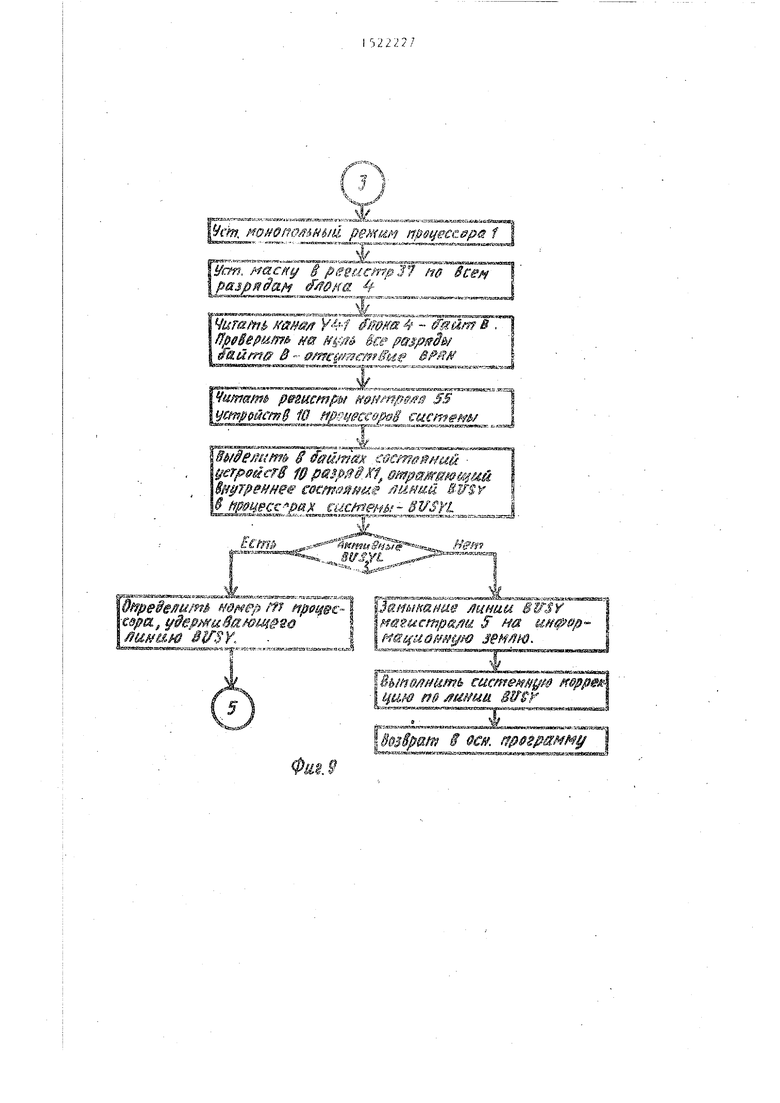

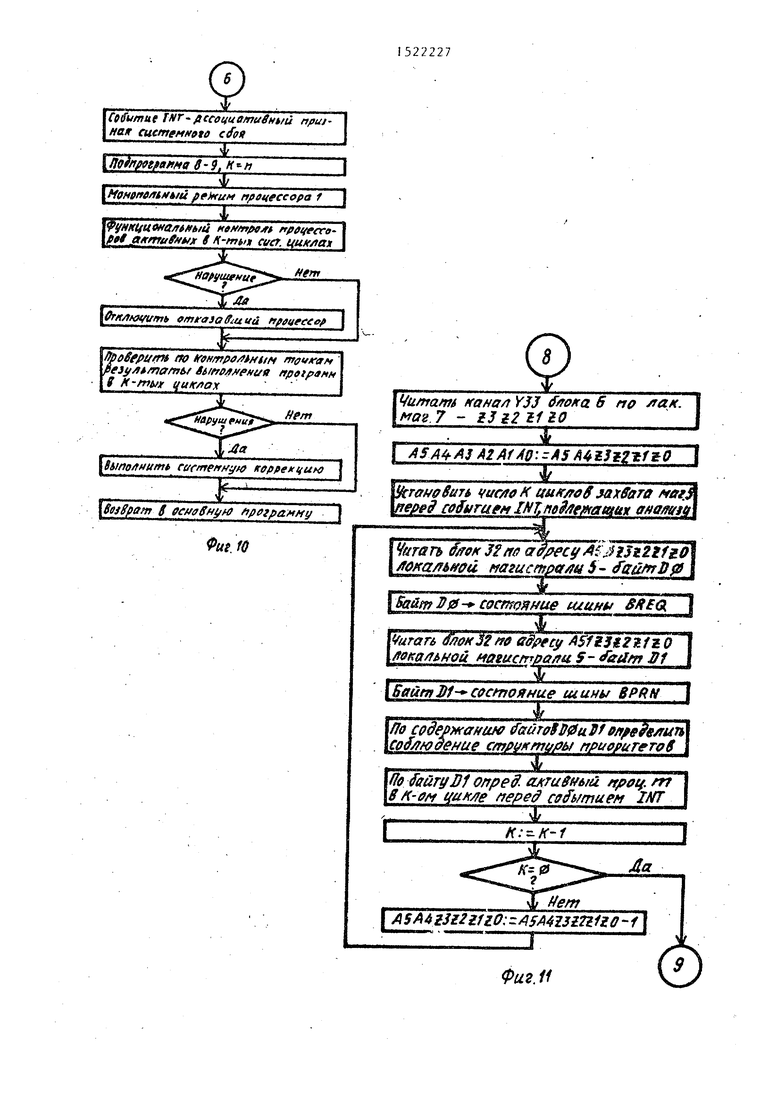

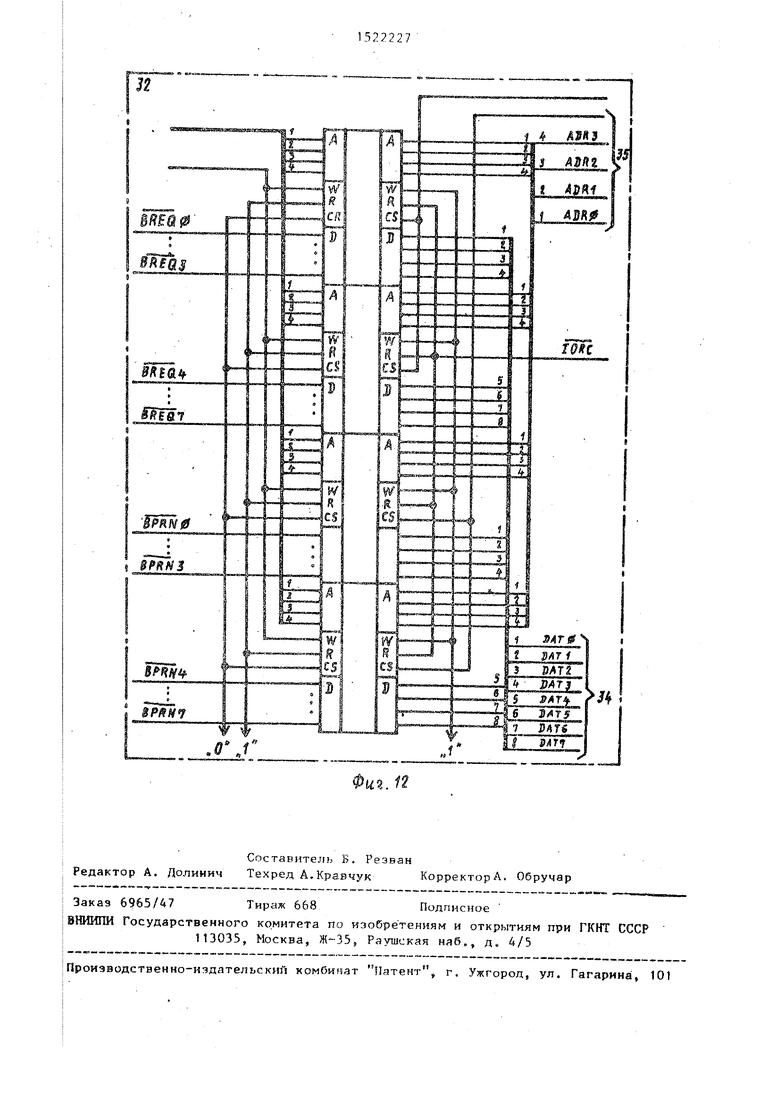

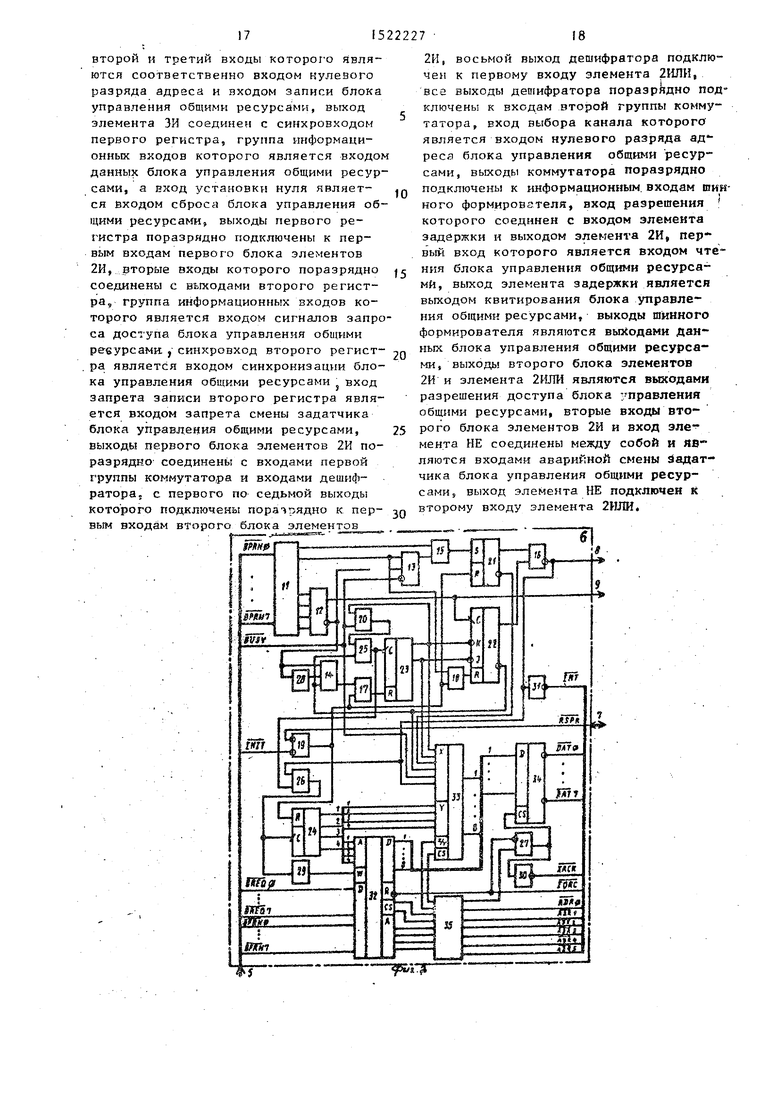

На фиг. представлена структурная схема мультипроцессорной вычислительной системы; на фиг. 2 - функцио нальная схема блока защиты для системы с семью исполнительнь ми процессорами; на фиг. 3 временная диаграмма фун ционирования блока зав{иты в режиме смены задатчнка магистрали; на фиг. 4 - функциональная схема блока управления общесистемными ресурсами для семи исполнительных процессоров; на фиг, 5 - функциональная схема процессорного устройства эахвй- та магистрали; на фиг. 6-И - блок- схемы алгоритмов функционирования под Системы управления общими ресурсами в нештатных ;ситуациях; на фиг. 12 функциональная схема двухвходового запоминающего устройства блока защи ты.

Сист-ема (фиг. 1) содержит главный процессор 15 исполнительные процес соры 2 с первого по седьмой, запоминающее устройство ЗУ блок управления общесистемными ресурсами 4, общую ма гистрапь 5, блок защиты 6, локальную магистраль 7, линию 8 аварийной смены задатчика, линию 9 запрета смены эадатчика, а каждьй процессор системы устройство 10 захвата магистрали.

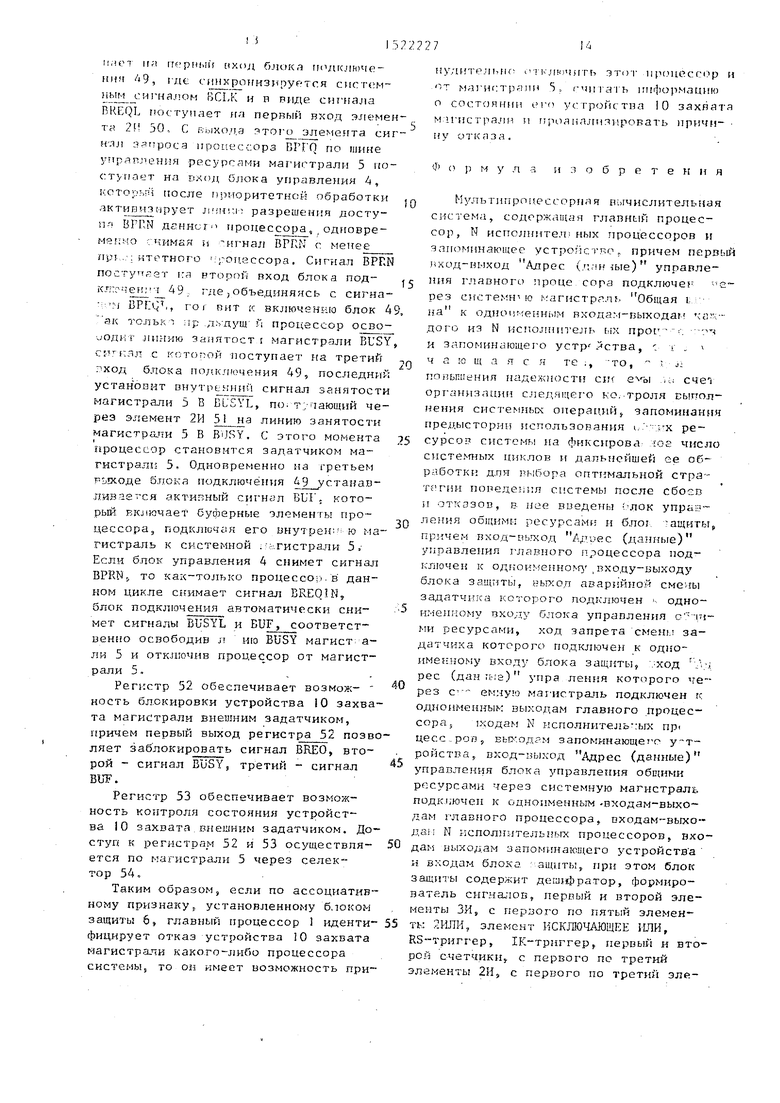

Блок защиты 6 (фиг 2) содержит дешифратор 11, формирователь сигналов 12 элементы ЗИ 13, 14,элементы 2 ИЛИ, 15-19, элемент,.ИСКЛ ОЧАЮИ1ЕЕ ИЛИ 20, RS-триггер 21.,. 1К -триггер 22,, счетчики 23 24, элементы 2И 25-27,. элементы задержки 28-30, одновибра- тор 31, блок двухвходовой памяти 32, коммутатор 33, шинный формирователь 34, селектор 35.

Блок 4 управления общими ресурсами (фиг. 4) содержит селектор 36, регистры 37, 38jэлемент 2И 39, эле

5

5

5

/

0

0

5

мент 3Vi 40, коммутатор , элементы задержки 42, шинпьгГ; формирователь 43, блоки элементов 2И 44, 45 дешифратор 46,, элемент НЕ 47, элемент 2 ИЛИ 48.

- Устройство 10 захвата магистрали (фиг. 5) содержит блок подключения 49, элементы 2И 50 51 регистры 52, 53 и селектор 54

Топология системы основана на магистральном принципе объединения структурных элементов и содержит главный процессор 1 системы, являющийся основой вычислительной подсистемы и выполняющий функции менеджера в обще системном масштабе, системное запоминающее устройство 3, являющееся в общем случае блоком оперативной памяти коллективного польэован Я, исполнительные процессоры , часть которых могут выполнять роль процессоров ввода-вывода, образуя подсистему ввода-вывода, другая часть - роль сопроцессоров или спецвычислителей., дополняющих вычислительную подсистему (конкретное их распределение зависит от спецификации конкретной системы и возлагаемых на нее функций), системную магистраль 5, являющуюся аппаратной частью интерфейса типа Multibus - ресурсом коллективного пользования, блок управления обп|есистемными ресурсами 4, являющийся аппаратным средст- вом управления доступом процессоров к ресурсам коллективного пользования, а также блок защиты 6, локальную магистраль 7, линию 8., аварийной смены задатчика, .пинию 9 запрета смены задатчика.

Архитектура системы включает подсистему управления общесистемными ресурсами, причем аппаратная часть архитектуры этой подсистемь образована, блоком управления общесистемными ресурсами 4, блоком защиты 6, локальной магистралью 7, линией 8 аварийной смены задатчика и устройствами 10 захвата магистрали, расположенными в каждом процессоре системы. Программная часть архитектуры подсистемы управления ресурсами содеря нт вновь вводимые в интерфейс протоколы обмена, режимы работы и алгоритмы управления , поддерживающие аппаратную ; структуру подсистемы,

МуЛьтипроцессорнай система управления работает следующим образом.

Мультипроцессорная умрлвляюпая система функционирует в рам кях интерфейса Multibus. Процессоры системы могут быть построены любым извостмым способом (за исключением устройств 1 захвата магистрали) , обеспечиваюм им протоколы обмена, предусмотренн1)Ге в Ilultibus, причем наличие локальной магистрали 7 не накладывает никаких ограничений на главньгй процессор 1 , так как протоколы обмена по ней соответствуют Multibus в режиме обращения к устройствам ввода-вывода и инициируются аппаратнь(м или программным прерыванием.

При нормальной работе система функционирует в полном соответствии со спецификациями Multibus, причем подсистема управления общесистемными ресурсами выполняет как обычную функцию управления, так и функцию следящего контроля, при этом выполнение последней не оказывает никакого влия- НИН на работу системы. Однако при возникновении конфликтной ситуации, которая может привести к отказу или зависанию системы, в работу последней автоматически включается протокол защиты к система переходит в режим аварийной работы, т.е. сохраняется функция управления на фоне функции 3 ащиты.

Архитектурной основой подсистемы управления ресурсами является ассоциативный признак конфликта. Признак может быть ложным или обоснованным, однако в любом случае он санкционирует включение в работу системы протокола защиты и соответствующих аппаратных средств системы. Дальнейшее поведение системы при этом полностью определяется результатом классификации признака. Такой подход хотя и допускает возможность ложных отвлечений системы, однако позволяет выявлять в системе на ранних стадиях отказы постепенного характера, выражающиеся первоначально в виде сбоев или конфликтов на системной магистрали 5.

В общем случае все процессоры 1 и системы автономно выполняют возложениые на них задачи, причем главный процессор 1, выполняя общесистемные управляющие функции, чод- держивает в. системе единство програм- мных структур. Все процессоры, являясь потенциальными задатчиками магистрали 5, устанавливают при необходимос

- JQ 15

20 25 Q

40

5

0

П

ти в послрднеГ: тррбуемк|р каклли внутрисистемной связи. Коммуникационные функции в системе выполняет блок управления об|цесистем ыми ресурсами 4, по;щерживая соответствующие протоколы доступа и установленную структуру приоритетов. Такое взаимодействие устройств системы обеспечивает ее функциональное единство при параллельной обработке системньгх и прикладных задач в масштабе реального времени. Блок защить 6 осуществляет следяп1ий контроль за соблюдением доступа и состоянием шины управления ресурсами магистрали.5, а также фиксирует все кЪмму- никационные преобразования в системе. При этом последняя функция блока 6 позволяет восстановить предысторию события на фиксированное число системных циклов . Наличие такого свойства в системах реального времени, которые не дают возможности предугадать последовательность выполнения задач, позволяет осуществить анализ прошедших событий, восстановить предысторию события, провести оптимальную контрольную операцию и выполнить логичес- кий возврат системы в промежуточную точку.

При возникновении в системе нештатного события в блоке защиты-6 формируется сигнал запроса прерывания, который в виде аппаратного сообщения по локальной магистрали 7 поступает в главный процессор I. Одновременно в блок управления 4 по линии 8 поступает сигнал, переводящий систему в монопольный режим главного процессора 1, когда снимаются разрешения передач для процессоров . Главный процессор 1 переходит к протоколу обслуживания ассоциативного отказа подсистекы управления ресурсами, выполняет анализ состояний аппаратных средств подсистемы, классифицирует отказ и осуществляет оптимальньй вариант дальнейшего поведения системы. Блок-схемы алгоритмов работы системы в таком режиме приведены на фиг. 6-11.

Блок защиты 6 подсистемы управления общими ресурсами работает следующим образом.

Часть блока защиты 6, содержащая дешифратор 11, формирователь 12, элемент ЗИ 13, элемент 2 ИЛИ 15, элемент HCiuflO IATOBlEE ИЛИ 20, элемент .задержки 28, элемент ЗИ 14, элемент 2И 25, элемент 2 ШШ 17, счетчи к 23, эле

цент 2 ИЛИ 18, ПВ-тр;иггер 21, IK-триггер 22, элемент 2 ШШ 16 и одновибра- ор 3, является анализатором уц-шьг уп авления ресурсами управления магист- ЗЛИ 5с Основной ее задачей пвпяетсл бнаруяение различных иарушакий в рвоте мультипроцессорной системы и немедленная реакция, Указакньге сред- отра кагот спецификации протокола подсистемы защиты и анализируют следующие ассоциативные признаки иарупге- чий в системе:

-нарушения в работе блока 4 уп-- равлеикя общесистемными ресурсами вьщача разрешения доступа одновременно двум или более эадатчнкан иаистрали)I

-HapyiufHHK цро ;ессорами протоколе орступа к маг и трали;

-отказь в :;:стройствах 0 захвата магистрали процессоров;

-нарушопш в линии занятости магистрали ;

-парущения и (-.бои п (- едствях за- диты системьи

iia нходы де(11ифр. ПпoдкJ ЮчeI;ь

пинии разрешения HPrN0 BS41N7 siii-tHb уп- ранлгмин ресурсами :,llиcтp;lпи 5. Де- Ш1 фратор I i пыпилнсм на сенате .пе- мента П ЗУ. iU.pfibiij выход дешифратора 1 1 переходит- в актинпое состояние Только нрс HajHi UH ил ег о од- ноиремекио болсч однптч) ак1ивно1 ( сигнала tlJ I N, т.е. блок 4 уста

НОВИТ более пдмосо разрешения тадатч И кам одновременно р либо произойдет : .я мыкание линиГ( рнчрешеттич, Лктшзиый сигнал с :)Tui-o выхода, проходя через элемент 2 ИЛИ 15, произведет установ ку RS-тригг ера 21,

Второй вмход дешифратора I1 переходит в актинное состояние при от сутствии активных сигналов на линняк ВРИЫ0-Г 1 К1 7. Этот сит-на; поступает I на первьцТ вход элемента 11-1 13, на ;Два других входа которого поступают Соответственно, сиг нальг таГдаерного i контроля и лянии занятости магистра- I ли 5 BUSY (с учетом инверсии). При этом 5 если за контрольное, яремя тай- I мерного сигнала с инверсного выхода i формирователя 2 не произойдет ociBo- бождения линии занятости BUSY, то 1 на выходе элемента ЗИ i 3 появится : активный сигнал, который, проходя че рез элемент 2 ШШ 15, также произвед установку RS-трнггера 21,

O

0

2-S

-,,

; I

- -

40

50 5$ т

(ледугощая группа из чег., аь хс дов дешифратора i 1 отражает ъ дв . ном виде унитаряьш ко, -:,. :-;,. , с : ; - щкй иа его входах. Очевк/г Н ;, -. .-;:::iD j i ность четырех выходов для такого ; - обрдзорани : связана с тем, что уо,

НИрОЗа гель 12, fSa ВХОДЬ которого ., ПОДЮГ : ; -, ДОЛЖВН фОрМИрОйЗТЬ НЗ

СВОИХ прямом и инверсном зькод х г г й- мерные контрольные сигналы при любэм изменении ситуации на входах дешиф- ;а- тора 1 3 . Формирователь 12 сра6атьшае7 по положительному перепаду на едком ШШ нескольких его входах, поэтому десять логически зкачиг-шх ситуацкй та вкодах деш} фратора i (восемь нор Mdji bKbHi рабочяж снтуац Й5 активен с-,,ин из вйэдоз ншрмальная нерабочая ситуацияS гсогда пассивны все входЫ|И аварийная ситуация, когда активны одновременно два или бол ее входов) .отображаются иа п,есять удобЬ Ь . ; Двоичных кодов из пятнадцати зозмох ных ненулевых на входах формирователя 12. Фориирователь 12-может построен иа осззове, например, одно- вибраторов типа К 155 АГ 3 и ги раег pojj, таймера coGbiTtift, создазаи на в.;л ходах при запуске Р П/ЛЬО 4 5KC5Jpo.vaH- чой длительносп, /иигтг,; } 0i:..:fa пульса равна Г лкснмальь :;:г/ зуене ; , смены задатчика магнстра пх 5, регла-- MeiiTHpoeaHHOMy 1ротоколом ;-, ; геь;ь, и о ределяет промежуток време; ; - в течение которого работаюиц Г- задатч; : должен освободить ма1 истг:. Ь 5, а задатчик, получкви - ii.;i ;- Лйшение от устройства 4, зохиатить ее. Таким образом, формирователь 12 создает Б системе таймерный сигнал кин гроля реального времени.

Схема,, состояща.ч из j.us vi ::;га ИС- КЛО ЧАЮЩЕЕ ШШ 20, элемента адерж ки 28, элемента ЗИ 14, элемшчта 2И 2 элемента 2 ШШ 17, c eтчикa 23, эле-- мента 2 ИЛИ 18 и 1К -триггера 22., f Sec- печивает контроль соблюдениг.. п,.-:чэ- кола смены зада / чика в системе, фиг. 3 гфиведена аременная .пиаграмма поясняющая работу этой скемьи

Элемент ИСК/ЮЧЛЮВДЕ ИЛИ 20, на . один 0КОД которого п ступает сигнал, с линии занятости BUSY магистрали 5 а на другой сигна.п с первого выхода счетчика 23 формирует короткие импульсы, как при освоборкденик магистрали 5 эадатчиком (переход BUSY в состояние лог, i), так и при захвате

MarncTpajFH 5 другии :я,;:ач- иком (. ход BUSY в состояние jsn , 0;, кс.-тс-- J проходя через -j, с...-. / г 2 1- 3-, : о- ступают на счгтггый :;ход счетчика 2 этом в иск(.;т,ном :: , ;-ju. : ьь; одлх счетчика 23 гом... .л,,,,;я JU , г/осле освобождения , с ;рч,:;- 5 ЭсГ- датчнк ом после захвата - 10 , Перс дячп магисп рали 5 от одпиго за-- длтчика другому доджна произойти в ечеиие времени, определенного длительностью таймерь ог о сигнала, по срезу KOTOpoi o срабатывает 1К триг- гер 22, причем, если переключение задатчикол произойдет в устаиовлен- s: ;A гфомежуток времени, то комб1ша- иия iО на выходах счетчика 23 (с учетом иниерсин) не состояния 1К- риггера 22, если произо; 1дет колько освобождение магистрали 5, то комбинация 01 приведет к переклю- чен.ию 1К-триггера 22, если не произойдет даже освоболщеиня магист.;- пи 5;. то комбинация 00 также при.-е- дет к переключению 1К-триггера .

При нормальной передаче м. гистра- ли 5 от одного з дг:гЧ;;ка к др г у сигнал выхода злеменга ЗИ 14 а р- жанньгй относительно ок нчапия т , него импульса при. помощ., t t. задержки 28, через эл .. т . устапоиит счетчик 23 : . . днсе с стояние. Наличие элемент,, ч обуслов.г:ено временем перек, . ...;.:.::-; L ч- тригтсра 22. При Hapyiueniiti чпотокола лередачи магистрали 5 riepeKjna PHKM 1К-триггера 22 сигнал с его инперс- него вьгхода поступает иа один из входов элемента ЗИ 14, запрещая обнуление счетчика 23 после окончания тай- мерного импульса, и на второй вход элемента 2И 25, запрещая дальнейшее переключение счетчика 23 по счетно- 1чу взсоду, причем по состоянию выходов счетчика 23 легко идентифицировать причину срабатывания 1К-тригге- ра 22, а значит, и эозможную причину нарушения протокола.

В случае, когда магистраль 5 освоШ

)5

20

25

30

35

40

c4ei(iCM 1)и-,де ., - .-i к зыв ет .а него ели

Vc raito-sK ; Tpti . е ои 2 , 22 и счет ; л,г 1 i cxoдиo ..стояние . fir- Bcдитпся je ,е элемент 2 HJf) 19 льЬо сигна,. ;Оь cucTpf чого сброса Ул 1Т : магр.стр;.л. либо сигн . r.x .i 1(рюгмамм1-. :-ij об i RSPK с .пок;,.ой магистрали 7,

При срабатына , .ого-либо нг триггеров 2 или 22 не лин5:л 8 ава- смены задатчика тере.-.- элемент 2 ШИ 16 устана1злпяаетгч ачтив- нып CHriia.rij, а в одновибркго. 3 фор мируется л:-1 1у льс запросл npt; . вания

мое гупающий по ггокальнсй магист 7 в глаБН. й процесс jp I .

1 редыдущну:

45

INT, рал и

Свойство регистрации коммуникационных преобразований в си теме,, т.е. запомлнанип системных цик лов смены задатчика в блг.ке защиты 6 обеспеч.: . тся элементом И 26, счет чнЕШ.- 24, тементом задержки 9 И бЛ ком . ухвходовой памя и 32. На

ет ыи п.сод счетчика 24 поступают lepej элeмt т 2И 26 импульс г с вьгхода злемч; 1та 2И 25, отличающие этапы смены задатчика D. системе, Двоичыый код на выходах счетчика 24 являе..я адрсстм ячейки в блоке двухвходовой памяти 12,, D которую - данном цикле записы,., ется г.цформация о состоян и , ЛИН тй залроса магистрали BREQ0-BREQ7 линий па пеп. ения доступа. BPRI I0- Ь РЛч 7 , управления общими ресурсами. Поскольку счетчик 24 работает iio ко.чьдевому принципу, то в блоке 32 всегда содержится информа- дия о шестнадцати предыдущих циклах. .псмент задержки 29 необходим для уверенной записи информации. Особенностью блока памяти 32 является двухсто- рокний доступ,, причем со стороны ма-, гистрали 5 он имеет шестнадцать информационных входов, а со CTOpoirbi по- калькой магистрали 7 - восемь , через которые может быть считана полностью вся информация, записанная по шестнадцатиразрядной группе информационбождается задатчиком, а другой задат- 50 цьж входов. Пример организации такого чик не претендует на ее захват, пере- блока памяти на основе микросхем ключение 1К триггера 22 бхюкируется КР 802ИР приведен на фиг, 12i сигналом с второго выхода дешифратора П, а счетчкк 23 обнуляется, как при нэрмаль ной работе. В случае первичного захвата магистрали 5 имнульс в„ 0лементе ИСКЛЮЧАЮЩЕЕ ИЛ1 1 20 не фор-- мыруетск, а отрицательньЕЙ перепад на

Доступ к информации блока защиты 6 по локальной магистрали 7 осуществля- 55 главным процессором I системы и режиме обращения к устройствам ввода- вывода при помощи селектора 35 по шине адреса н коммутатора 33 с шщпгым

Ш

5

0

5

0

5

0

c4ei(iCM 1)и-,де ., - .-i к зыва- ет .а него ели

Vc raito-sK ; Tpti . е ои 2 , 22 и счет- ; л,г 1 i cxoдиo ..стояние . fir- Bcдитпся je ,е элемент 2 HJf) 19 льЬо сигна,. ;Оь cucTpf чого сброса Ул 1Т : магр.стр;.л. либо сигн . r.x .i 1(рюгмамм1-. :-ij об i RSPK с .пок;,.ой магистрали 7,

При срабатына , .ого-либо нг триггеров 2 или 22 не лин5:л 8 ава- смены задатчика тере.-.- элемент 2 ШИ 16 устана1злпяаетгч ачтив- нып CHriia.rij, а в одновибркго. 3 формируется л:-1 1у льс запросл npt; . вания

мое гупающий по ггокальнсй магист- 7 в глаБН. й процесс jp I .

1 редыдущну:

5

INT, рал и

Свойство регистрации коммуникационных преобразований в системе,, т.е. запомлнанип системных циклов смены задатчика в блг.ке защиты 6, обеспеч.: . тся элементом И 26, счет- чнЕШ.- 24, тементом задержки 9 И бЛ ком . ухвходовой памя и 32. На

ет ыи п.сод счетчика 24 поступают lepej элeмt т 2И 26 импульс г с вьгхода злемч; 1та 2И 25, отличающие этапы смены задатчика D. системе, Двоичыый код на выходах счетчика 24 являе..я адрсстм ячейки в блоке двухвходовой памяти 12,, D которую - данном цикле записы,., ется г.цформация о состоян и , ЛИН тй залроса магистрали BREQ0-BREQ7 линий па пеп. ения доступа. BPRI I0- Ь РЛч 7 , управления общими ресурсами. Поскольку счетчик 24 работает iio ко.чьдевому принципу, то в блоке 32 всегда содержится информа- дия о шестнадцати предыдущих циклах. .псмент задержки 29 необходим для уверенной записи информации. Особенностью блока памяти 32 является двухсто- . рокний доступ,, причем со стороны ма-, гистрали 5 он имеет шестнадцать информационных входов, а со CTOpoirbi по- - калькой магистрали 7 - восемь , через которые может быть считана полностью вся информация, записанная по шестцьж входов. Пример организации такого блока памяти на основе микросхем КР 802ИР приведен на фиг, 12i

Доступ к информации блока защиты 6 по локальной магистрали 7 осуществля- главным процессором I системы и режиме обращения к устройствам ввода- вывода при помощи селектора 35 по шине адреса н коммутатора 33 с шщпгым

20

о|р1мироватеяем 34 по да}п;ьр -. Эле.-- сйт 2И 27 и элемент запер:ч:ки 30 фор- ми|руют сигнал квитгфованг Ш.

; Блок управления снсгемкыку; ресур- 4 работай ) сле/ду ощим обрааон.

Снгнал -. запроса на доступ к ресур - CMf- нагкстрали 5 от npoi eccopoB сис - темь поступает на входь persicxpa 38 запросоБ, где фиксиругстсР-: прн иомоищ е|:гн ша системной скнярсжнзап, BCLiC. Сигналы а -проса с выхода регкстра 38 чераа блок леме51тов 2И 44 посч упают K i вкоды дещ5.5фратог а Л6, На вторые эчодь5 эг сментов 2И блока 4п поступает

у. ; ГНаЛЫ с выходовр ;Г СТра 37 Мне;- s Hj который поз-эопяет при необходин1:)с, ти запретить прохождение тек или нпнх запросов от процессоров на входы де-- 13 и«| ратора 46. ннфоркад|-ги в pfr- гкстр 3 производится rnaBBbSM про- юесссх ом 1 в режиме обращаяик к уст- ройствам ВБОда зыводй по дшне данных системной маг|. 5 при помощи сигнала записи 10 WC с выборкой ре-- Tt- S HC fpa 37 no шине адреса через сепек.- гор 36 и ЗИ 40 Дешифратор А6 1дс:троен на 1зскове запоминающех о уст-

|5ойства I содершгг Т и9лицу приорнте17ОВ процессорен, п.рикят ую в системе .

Но линии на один из .входов регкст- sa 38 поступает снгь аг, запрета сме:кы задатчяка с блока 6 подсистемы 1 нравления общннк --есурсами который йвяяется импульсе тайг .ег;л- ого контро 1ггяс Этот CHrHSji запр гйгае.-: прохой деги-5й Л5 tea выкоды регистра З В запросов,, по- |ступнвшик в период смени задатчнка на Ыагкстрали 5«i- необходим кпя ксклю- е - ия сбоер сйстемь; во время гиаредачи :магистрали

После приоритетной обработки по- CTynHsmtsK запросов в деядифретора 46 па из его вынодов п-ггявляется активный сйгнап, который шрез один

.из вьп одньис элементов (лиВо -блогга меятоа 2И 45 либо эке.неит 2 ИНК 4В) поступает по одной йз рззуеоза - няя доступа BPRH в ианбояее пр норн- - те гный на дашшй момент процзссор cиcтe fЫ,. SO

йрн обнаружении блоком зшдать ;, 6 какого-либо ассощ ат5Ш5юго признака нарушения s функцнонировагн н па.д- снстёг-2 управления обвдами рееуреаьки на птти 8 ааарийной смегк- захдатчнг а 55 i /CTtffiasnHaaafся активный csirHaTij, ко--- ступаютрй в блок управления 4 на кто . рые вжодь элементов 2й блока 45 и

0

t-

Л5

SO

55

вход зламента ИЕ 47. В этом С.ПУЧЯЙ лзо гкоднт пpинyдитeль ШG изиенение структуры приоритетов и аварийная коррекиля протокола доступа к магмст™ р.али 5. Скгнап иа линии 8 запрещает разрешение доступа згедатчиком, под- ключелйЕым к линии BPIlH0-BPRN6s и ди- рэктивно устакавлиззет ектиБКь й уро- ваиь на линир разрешения доступа BPRN 7 к которой подк гкзчеи главный процессор I системы, баз учета запросов па Екоде регистра 38, Снстеаа пе- раходит в моног5ольньгй режим главного процессора l- причем процессор 2, работавший перед этим co5ытиe i на ма- /гистралн 5.; освобождает ее Оста.чь-- 51ые процессоры 2;./ не смогут закват ггь ма|Л1 страль 5 из-за отмаутств:ьш сигнала BPRKs а главный прпцессор i получает магистраль 5 не по протоко.п,, достугга, а по переводу системы « однопроцес- гсорный вариант со всеми вьп екакниими последствиями

Доступ главного ироцассора i к ин- -формации о HHyrpe.HjreK состоянии бло- ; :а управления 4 ос:уН1СС ГЕ1шется в режиме обраш,еямн К устройствам ввода- яыэода ю шике данных .1 агнстраля 5 счгналок 10RC с БЬ боркой по шкне адреса npj-i. not-joiiiH селектора 36 и злЕмен- та 2И 39. Держателем ияфорьадии о энутре1-;ие г состояниг-: является ксмму- гатор 4К имеющий оргакизахихад; ДЯй

восьмиоазряднык каналя один р. „ S Яиразрядньк-i, прнчем при обр;ал ,ении к

каналу X лроцессор 1 получает нкфор мацшо о присутствующих запросах,, а при обращении к каяш1у Y } резуль- TiViVLt приоритетной обработки запросов дешифратором 46«, Шииньй формирователь 43 является буферным . с .тремя состояниями,, а элемент эадер;«. Kg-s А2 формирует сигнал квнтироизлгиЯд Таким образом 5 прр наличии аесоциа-- тивиого признака отказа блока управ- лйния 4 главкь й процессор 1 может i ipO анализировать структуру прксз тствую- щг,$к запросов и правильность приоритетной ик обработки дешяфрзторон 46,

Устройства 10 захвата Мт гиспгра/ш вводящие в состав каяуз.ого ;роцессор сб1стег-1ы и являющ еся - гутщ кп&пьншт элеме {тами подсистемь упрйвлеинг рс- cypc-a№j, работают следугш им образом г.

При необходимости доступа к ресур сам системной магистрали 5 процессор S каждом цикле формируй )знутрен 11й снгиал запроса BSJEQINp которой

ii,(M ii;i nepHi.iii tfxojl блока i()4e- ННЯ Д9, где (.пш ррнизируртся систч м- нь м сигна.ом BCLK и в виде сигнала BKEQL гюступает H, J первый вход элемен

та 2 50, С выхода ) элемента си H .iji зягтроса про1.ессорз ВГГП по iiinfie ynpanjieni- H ресурсами маг истрали 5 поступает на ()д блока управления 4, icoTopbn i после приоритетной обработки лктиг;И кэмрует ji iHr.i; разрешения досту- п- BPHN данног яродессора, , oдF oвpe- M9f:i o :;чимая и игна; BPCN с менее nyi ., : итетного гроцессора. Сигнал BPF. поступ о-г -а второй вход блока под- к.ггс чер -г АЭ ; гпе , объединяясь с сигна BPIIi,, го г RUT к включению блок ак только :лр ,д;,-дущ fi процессор осво- иоднг лиггию заяятост магистрали BUSY с к(5топой постунает на третий Г1ХОД блока по/г.ключения 49, последний устан овнт вну т религии сигнал занятости магистрали 5 В BL SYL, по. т/аающий через элемент 2И линию занятости

магистрат и 5 В BiJSY. С этого момента гфоцессор становится задатчиком магистрали 5. Одновременно lia гретьем рькоде блока подключения 42 устанан- ииваегся активный сигнал BUF, который включает буферные элe eн гы процессора, подключг к его внутрен: ю магистраль к системной ;-глГр5страли 5 . Если блок управления 4 снимет сигнал BPRNs то как-только процессо;: . в данном цикле сь имает сигнал BREQUJ, блок подключения автоматически снимет сигналы BUSYL и BUF, соответст- Бенио освободив л ию BUSY магист: а- ли 5 и отключив процессор от магистрали 5.

Регистр 52 обеспечивает возмож- ность блокировки устройства 10 захвата магистрали внешним задатчиком, причем первый выход регистра 52 позволяет заблокировать сигнал BREO, второй - сигнал BUSY, третий - сигнал BUF.

Регистр 53 обеспечивает возможность контроля состояния устройства 10 захвата. в1 ешним задатчиком. Доступ к регистра м 52 и 53 осуществля- ется по магистрали 5 через селектор 54.

Таким образом, если по ассоциативному признаку, установленному блоком защиты б, главный процессор 1 иденти- фицирует отказ устройства 10 захвата магистрали какого-либо процессора системы, то он имеет возможность при

иу. ИП ельпо 01 к,|к:Ч)Гть этот ироцоссг р и IT яrиt:тpaин 5. считать )-)млци1) о состоянии ег( усгройства 10 захяата ми истралн fi г ролил.ггпг11 ровать .ч- ну отказа.

Ф о р м у л

обретения

10

s

0

5

0

5

5

Мультнпропессорная вычислительная система, содержащая главнь|й процессор, N исполнител ных процессоров и 3лнo инaющec устропсгяо,, причем первьй яход-выход Адрес (,r;;iH {ые) управления гласного проце сора подключен --е- рез еисте.нмо .магистр.ль Общая i; : на к од О1 меннь м входам-выходаг ча л-ДОГО из N ИСГ О1 НПТеЛЬ ЫХ npOl - -р-ч

и Зйпоминающег-о устр .ства, , г . ч а 1-0 щ а я с я те ;, то, ; j; П0) надеж1 ости CJK . счет органнза 1ии следящего ко,-троля Еыггол- нения системных операц.ий, запоминания предыстории использования i..I X ре- cypcoi системы на фиксировл чог число систем ых циклов гт дальнейшей ее обработки для выбора оптимальной стра- TSTiiH пореде;;1:я системы после сбоев и отказов, в нее введены (лок управ- общими ресурсами и блог, -ащитЫр причем вход-выход Адуес (данные) управления главного процессора под- к лючен к oдJ;oимeннo r , входу-выходу блока защттты, нькол аварийной задатчика которого подключен одно- имеНдЧо 5у входу блока управления o i/ - ти ресурсами, ход запрета задатчика которого подключен к одно- имениоь у входу блока защ11ты, . ХОд /V-i pec (дан;ь;г) упра ления которого через с - емнуга маг истраль подключен tc одноименным выходам главного процессора 5 )ходам N исполнитель гьгк npi цес.с.. роя,, вьр .ода;- запоминающего у-т ройства, ВХОД-15ЫХОД Адрес (данные) управления блока, управления обп1Имн ресурсами через системную магистраль подкьточен к одноименным -входам-вь хо дам глазного процессора, пходам-вько- N гисполнительпых процессоров, вхо- ц&м вьгходам запоминающего ус7 ройств а н входам блока ; ащить, при этом блок защиты содержит дешз4)ратор, формирователь сигналов, первый и второй элементы ЗИ, с первого по пятый злемен- ты 2ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, КЗ-триггер, 1К триггеру первый и второй счетчики, с первого по третий элементы ZH, с первого по третий эле

j я блока 3 ащи ты j атора соединен с D элемента 2йЛйс

задержки5 однозибратор, блок дг ухвходозой памяти, ком-мутатор.; формироватехгь и селектор причеи 0ФОДЫ дешифратора 9 первьгй вход гшрвоэлемента ЗИ первьтй вкод перного емента ZPiJlH и группа г нфп НЁЦИонньгх в:юдо8 блока дву входокон памяти оС5- разуют вход Адрес (данные) управле-nepsbsu дешиш- первым зкодом втооовыход КОТОРОГО ПОД-1ючек к 8--аходу. К3 триггера,, второй ::жод дешифратора соедшЕал е вторым

vrs;.;;OM ПврВОГО ЭЛеМйКТй 3Fi 1 ГШрВЫИ

дом третьего элемента 2.HJiKj выхся.

;.)рого подключег-з к R-входу ХК-триг- ера выход первого элемента ЗИ соедя eii с вторым входом второго злеиеПц.

ЙПИ . вьжодь} дешифратора с тратье о

о шастой соединены с. первого по -гетертый входами формирователя скгкалов рямой выход которого подключен к cms ровходу 1К триггера и является ом запрета смены зедатчика блока sa- йты, инверсный аькод формирователя мгналов подключен к третьему входл ервого элемента ЗИ, первому горого элемента ЗИ и входу первого лемекта задержки, выход которого со- ДИМ8Н с вторым входо второго эле-. -5ента ЗИ,, вынод которого .подключен к первому входу четвертого элемента 21ШИ5 которого соедкнен с j ;о-- дом установки нуля первого счетчика I ечетньш вкод которох о подключен к-; вы- i ходу первого элемента 2И и первому i входу второго .элемента 2И, инфор ацн- I окйый выход первого разряда первого счетчика подключен к первому вяод i элемента ИСКЛ№ШОЩЕ ЕПИ, к K.,y : 1К.-трнггера и первому входу ги;:рпол группы входов коммутатора, ии4и:ялмациониый выход второго разряда vr.b;r- :-o

го счетчика подключен к: 1-вкоду IX- триггера и второму входу первой груп пы входов коммутатора э выход элемек - та ИСКЛЮЧАЮЩЕЕ ИЛИ соедш ен с первым входом первого элемента ZH, ,e выхода RS-триггера и 1К триггера соединены соответственно с первым к: зг , 1м входами пятого элем©йта 2ИЛИ5 вьг код которого соединен с входом о,цно вибратора, вторым sз5oдo s второго элемента 2И, шестым входом лерэой пы входов ком гутатора н является вы- ходом аварийной смены задатчика блока защиты ,, ннЕврсный аьпЕод RS-триггб ра подключен к третье входу пепвой

522227

16

5

,

; , -

f «

группы входов коммутатора, а инверс- йый выход 1К-триггера подкпючр.н к четвартоку зходу ггервой группы входов яом-гутат ора, третьему входу второго ЗИ к второг-г/ входу первого элемента 2Й5, выход первого элемента 2ИЛМ соединен с входом установки ну- , ля RS-триггера и второго счетчика, с вторыми входами третьего и четвертого элементов . вькод второго элемен- та 2И подключен к зторог-э эяе- манта задержки и счетному входу второго счетчика, кнформаол-Еокные выходы кот(зрого соединень5 с входами адреса г ервой группь блока двухвходовой памяти и икформациокиыки входами второй группы коммутатораS выход второго элемента задержки соеди-шн с входом заииск блока двухвходовой памяти, вхо- дь8 адреса второй группы и нервый и аторой вкоды вьЕборки которой соёдике яы с первого по шестой вьссодами селектора соответственно, седьмой, вось кон, девятый выходы которого соединены соответственно с первым входом третьего эламента .ЙИ с вкодок выбора .а и входом разрешения коммутато - ра, вьтходь которого поразрядно соедк™ . лены с .на1щонкьти вьtxoдa sи бло™ ка двухвходовой памяти и входамк ашн ного форкярователя, взшд разреатения которого, соадикен е гвыходом Т1эетьего элемента задерлшк, выход одковибрато- ра Я зляется выходом запроса прерывания блока защиты, второй, вход .первого элемента 2FJffl является входом прог раммного сброса блока защиты, вьшоды

шинного формирователя являются вьгаода- ни ддг-HbR ; блока защиты третья го г. задержки является вы- y.o;i,Qi4. квитировання, ооъедштенные второй вход ре гьвх О ;:;-jieMeKTa .2И и вход чтения i;.i ,:;x.-i двухв ждовой памяти яв- ля|отся входом чтення блока защиты, входы селектора являются адреснь5ми входами блока з.ащитЫ5 а блок управле кия, общими ресурсами содержит селек- Top-j первый и второй регистры, элемент 2й, элемент ЗИ, коммутатор,, эле мент задержки, шинныйфop шpoвaтeпь,. первьш д второй блоки элементов 2И, .дешифратор, элемент НЕ и з.яемект 2ИЛИ, rtpH -ser-s группа входов селектора явля ется входами адреса блока управления обпдани ресурсами первый зыхок селектора подключен к первому входу элемента 2И, второй ыьгход которого под- -слгочан к. первому входу элемента Зй,

второй и третий входы которог о являются соотаетственно входом кулевого разряда адреса и входом записи блока управления общими ресурсами, выход элемента ЗИ соединен с синхровходом первого регистра, группа информационных входов которого является входо данных блока управления общими ресурсами, а вход установки нуля являет- ся Входом сброса блока управления общими ресурсами, выходы первого регистра поразрядно подключены к первым входам первого блока элементов 2И, вторые входы которого поразрядно соединены с выходами второго регистра, группа информационных входов которого является входом сигналов запроса доступа блока управления общими рееурсами j синхровход второго регистра является входом синхронизации блока управления общими ресурсами вход запрета записи второго регистра является входом запрета смены задатчика блока управления общими ресурсами, выходы первого блока элементов 2И поразрядно- соединены с входами первой группы коммутатора и входами дещиф- ратора, с первого по седьмой выходы которого подключены пора чрядно к первым входам второго блока элементов

,

лш

15

м 20

25

0

2И, восьмой выход дешифратора подключен к первому входу элемента 2ИЛН, все выходы дешифратора поразрядно подключены к входам второй группы комму татора, вход выбора канала которого является входом нулевого разряда ад реса блока управления общими ресурсами, выходы коммутатора поразрядно подключены к информационным, входам шинного формирователя, вход разрешения которого соединен с входом элемента задержки и выходом элеменга 2И, пер- Bbrfi вход которого является входом чтв ния блока управления общими ресурсами, выход элемента задержки является выходом квитирования блока управления общими ресурсами, выходы шинного формирователя являются выходами Дан ных блока управления общими ресурсами, выходь второго блока элементов 2И и элемента 2ИПИ являются выходами разращения доступа блока з/правления общими ресурсами, вторые входы второго блока элементов 2И и вход эле- мента НЕ соединены между собой и ЯВ ляются входами аварийной смены Задатчика блока управления общими ресурсами , выход элемента НЕ подключен К второму входу элемента 2ИЛИ,

i i 5

- -i i

s

Sfey S:yyt l

S

psjfi if xf (fa i /rT a

lOm/fSs € ffcff § K fffnosfs - 3ffefffft 115 f/fSffu S /fuf/ u e. CufffffffS. &воп (0спвсу а / sS/ f/jpff eccof ном e&puef/m.

u. .

zi«::zziizsziizizzL

, m.S

Giwe .fff i

.i- -.rrT.V--..:V-.I;T. Ф .,. -;,t ,,, flfli / C

9 1

- -J --..,j«

ICSift-imuel i..ffiifi f: ii .;,.

{J:.;iJff i U/m t.::pf7 XfXO t/t dmaAj

a {:/шр ци/f/ra осва- I . . 5

и йг/«/лг -.;

I I f- Vf/ i Offfi/ff iVfui /Vi .--V77A / J

I |/// РбГ :: . ; & ДЛ6 /Й- if

I ,.

;ffp /L;;f-/ -i

;

Л (Р

v7ff&j ( r HOf epoffffi, Wrif wfumi профессор-scifts ci T bw / / pesuemfl 52

Bb/ff / fftimA cueme/ ff Hj c /j / e/fijUH)

ffJ.

.f

4

,.,,

//Г(

.

. / af i/iaeA j.s

: //i vv ) ;; .f

i/7o ,: л .

Л (

OM / f WfmJ-17 fj /f/ ffyec.c&

T-pesi/ff&maf 7 .систеннегв d .

IfpffiTpuri fro JfOf/rpO/fikH&ff

f(a peyi/f Tt fr amt /Аогд Л ЛУ Д I / ff-mb/K е/а.А-/г&.

//em

Wc, MOi oniM&fitiu ретш1 npstjecc p 1

Г-1Я Д-Л

yi:vn,/ f&cf y § ffgucmpS fte Scefi i,i - .. .дц атг;аст«йаиутага«:цщ кя;;а;и 1яа

4umfn лшад И-/ /Шш -4 - ff fium в . I Jpo§epu/n //& i/M See pmp 8&iI

/kufnff в - &/f c f mTff fff BP/}//I

г Емтакг Jf Г. j:x 3r:/л:; ъгг.ьгя1 тэекз1--й г;гак 3 яа :.

« xrb:jira rT3:34C(aTfeEHCr

peiKCfnpM 9нщо9/ й 55 22ZlJ S, .

Bb/§f/ni & S /ffumiSK сбствймаА

llf,..-.J.

t uj e asfas - yt ifyyibv it .# ( Sat-- t . - - -

|e.to-«: ™.,

.V,, Э , .;

Г-1Я Д-Л

cefi

« xrb:jira rT3:34C(aTfeEHCr4JS JTCZ:

55 SL.

t . - - -

C9fumue ТИ flccotfutifnuettnu nput ная cuctnentiftu cfoe

fjffffrfffefaftfta 3-9,

jL

HOH&ne/HfHttu npeyffссора 1

ш -

IYyuKtiUwa/rtftbiu nettfftftejTt fffmafftt/x t ff-mt/x ever, циклах

Ла

OTH/tKftfU nb ffmfaJoff uuu ftffuffeof

f oSefUfr ею IfffHffTpa/f ftttfi резул тат йяпрл емив про1ранн

f f( lfU/f/ OX i

,4a

S&ino/fHumt cucmpffffyto KoppetiifUH)

eiSpam 8 семУнун) fjflPipaMHt/ us. fO

1522227

i/umafnt ffOHO/f Y33 ffffoKo. 6 no /гак. ма г.7 - 1312 Ъ110

ASA ASAZAlAO A5A4 3ltlTi1ZO

8

:rafiffSa7i, tfuc/ic К t{uff/faS xSaret e/w9 c0ftiruff9lNlm9/ff atii&x

Т d

итвгь /ffffffjf ffff ffff/fecy f fiJzZlfgiOl /fOKuMffOu Naiucm /fti 5 - I

Шт - -состо: ни€ JisTJi

7 Т ГТУ У „и.

wurarreaoKWWeS Cff AS1Z5 24ifi 0 ftOKa/fi f pu HCtsucfrtpafltt. 5-fatJm Sf J

Ф:

Байт2)1- с0с тгояни.е шиньг ВРКН

4r

По codepwaffufff (fauro8B0uJifefff9 s/ritn fo /ffoaeHUe г/яиуу/yy /w приоритетов

.

Ш suryDI o/rpeff. aj(Tu$(f6fu . fn

ffepe Cff/ь/тием INT

|,-. 1..

Ла

A5AJ l3l2inO: - SA lSlllllO l

,.

Фиг. 11

0

| Патент США К 4282572, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Органик Э | |||

| ПЛУГ С ВРАЩАЮЩИМИСЯ РАБОЧИМИ ПОВЕРХНОСТЯМИ | 1925 |

|

SU432A1 |

| с англ., М.: МИР, 1987, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-22—Подача