Изобретение относится к области вычислительной техники.

Целью изобретений является расширение функциональных возможностей за счет обеспечения обнаружения ошибок в последовательности передачи управления интерфейсом и исключения данной последовательности при обнаружении ошибки из набора последовательностей обмена.

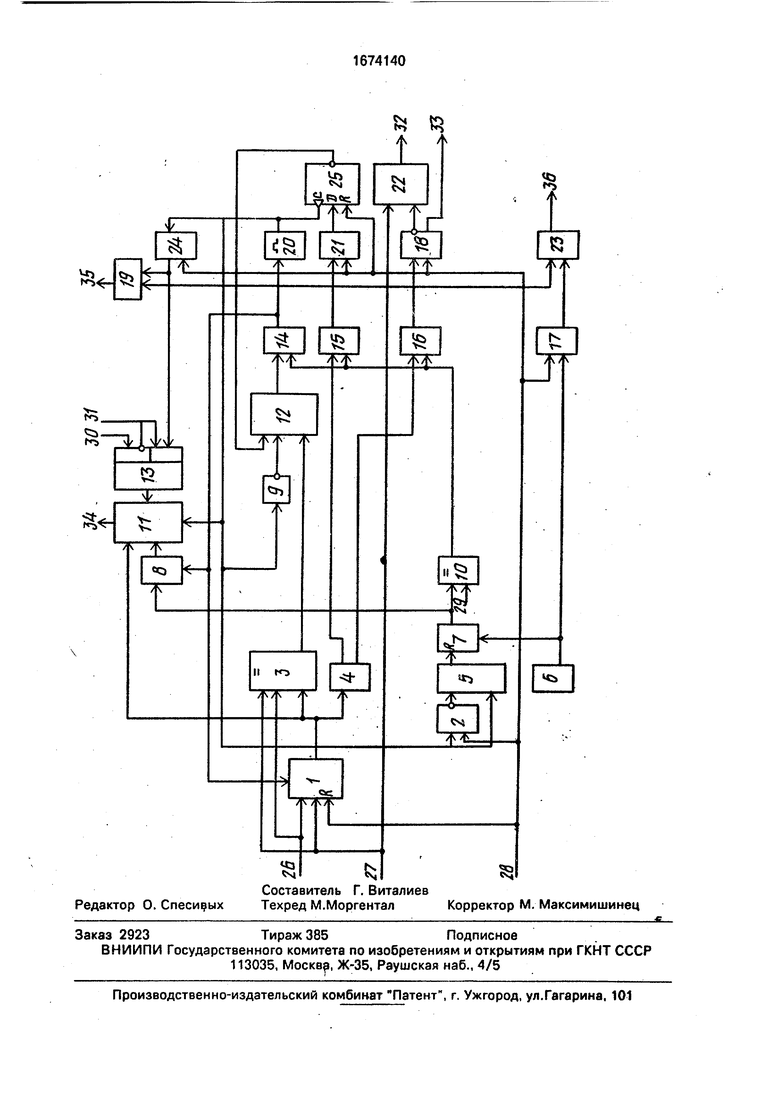

На чертеже представлена структурная схема устройства.

Устройство содержит регистр 1, триггер 2, схему 3 сравнения, дешифратор 4 состояний интерфейса, элемент ИЛИ 5, генератор 6, таймер 7. регистр 8, элемент НЕ 9, схему 10 сравнения, блок 11 памяти, элемент И 12, коммутатор 13 адреса, элементы ИЛИ 14 и 15, элемент И 16, таймер 17, триггер 18, регистр 19, одновибратор 20, триггер 21, элемент И 22, регистр 23, счетчик 24, триггер 25 и имеет информационный вход 26, вход 27 признака запроса магистрали, вход 28 сброса, вход 29 константы, адресный вход 30, вход 31 признака коммутации, выход 32

признака запроса магистрали, выход 33 признака ошибки, выходы 34-36.

Информационный вход регистра 1 совместно с первым входом схемы 3 сравнения соединен с входом 26 устройства и входом 27. Выход регистра 1 соединен с входом дешифратора 4, вторым входом схемы 3 сравнения и информационным входом блока 11 памяти. Выход схемы 3 сравнения подключен к одному из входов элемента 12, другой вход которого соединен с выходом элемента 9, а третий вход элемента 12 соединен с инверсным выходом триггера 25. Выход элемента 12 соединен с одним из входов элемента 14, выход которого соединен с синхровходами регистров 1 и 8. Выход регистра 8 подключен к другому информационному входу блока 11 памяти. Кроме того, выход элемента 14 соединен с входом одновибратора 20. Выход одновибратора 20 соединен, со счетным входом счетчика 24, синхровходом триггера 25, входом элемента 9, установочным входом триггера 2, одним из входов элемента 5 и входом режима блока 11 памяти. Другой вход элемента 5 под&

fe

О

|

S

ю

ключей к инверсному выходу триггера 2. Выход элемента 5 соединен с входом сброса таймера 7, выход которого соединен с входом регистра 8 и одним из входов схемы 10 сравнения. Другой вход схемы 10 сравнения подключен к входу 29 константы. Выход схемы 10 сравнения соединен с оставшимся входом элемента 14, одним из входов элемента 15 и элемента 16. Другой вход элемента 15 соединен с одним из выходов дешифратора 4. Выход элемента 15 соединен с установочным входом триггера 21 и синхровходами регистров 19 и 23. Выход триггера 21 подключен к информационному входу триггера 25. Другой вход элемента 16 соединен с оставшимся выходом дешифратора 4. Выход элемента 16 подключен к установочному входу триггера 18. Инверсный выход триггера 18 соединен с одним из входов элемента 22, другой вход которого соединен с входом 21 устройства. Выход элемента 22 подключен к выходу 32 признака запроса устройства. Прямой выход триггера 18 соединен с выходом 33 сигнала ошибки. Выход генератора 6 подключен к счетным входам таймеров 7 и 17. Вход 28 сброса устройства соединен с входами сброса регистра 1, триггера 2, таймера 17, триггеров 18, 21, 25 и счетчика 24. Выходы блока 11 памяти и регистров 19 и 23 соединены соответственно с информационными выходами 34-36 устройства.

Устройство работает следующим образом.

В исходном состоянии на вход 28 устройства подается сигнал сброса, в соответствии с которым регистр 1. триггеры 2. 18, 21 и 25. таймер 17 и счетчик 24 обнуляются.

Устройство работает в двух режимах Контроль и Вывод.

В режиме Контроль осуществляется контроль состояния сигналов интерфейса и фиксация последовательности изменения состояния сигналов интерфейса.

В режиме Вывод осуществляется считывание из блока 11 информации о состоянии интерфейса с последующей обработкой и регистрацией на одном из стандартных устройств вывода.

Режим работы устройства определяется сигналом на входе 31 устройства. В режиме Контроль при наличии соответствующего сигнала на входе 31 устройства осуществляется подключение выходов счетчика 23 через коммутатор 13 к адресному входу блока 11 памяти. В режиме Вывод при наличии соответствующего сигнала на входе 29 обеспечивается подключение адресного входа 30 устройства через коммутатор 13 к адресному входу блока 11 памяти.

В режиме Контроль сигналы интерфейса с входа 26 устройства поступают на

входы регистра 1 и схемы 3 сравнения. Поскольку в исходном состоянии регистр 1 обнулен, то при появлении на входе 26 устройства сигналов интерфейса на входе схемы 3 сравнения появляется единичный

0 сигнал. В этот момент времени на входах дешифратора 4 присутствует О, а на выходе его находится нулевой сигнал, При поступлении сигнала на вход элемента 12 на остальных его входах находятся единичные

5 разрешающие сигналы, так как в исходном состоянии триггер 24 был обнулен, и на его инверсном выходе присутствует единичный сигнал, а запуск одновибратора 20 отсутствовал, В результате на выходе элемента 20

0 появляется сигнал, поступающий на вход элемента 14. Сигналом с инверсного выхода триггера 2 таймер 7 удерживается в исходном состоянии. На входе 29 устройства присутствует константа, равная значению

5 интервала времени, в течение которого допускается отсутствие изменения состояния сигналов интерфейса, поэтому на выходе схемы 10 сравнения находится нулевой сигнал, поступающий на входы элементов 14 и

0 15, и после поступления единичного сигнала с выхода элемента 12 на вход элемента 14 на его выходе формируется единичный сигнал. По переднему фронту сигнала с выхода элемента 14 в регистре 1 фиксируется состо5 яние сигналов интерфейса на входе 26, а в регистре 8 - код на выходе таймера 7 (в данном случае нулевой код). Кроме того, по сигналу с выхода элемента 14 осуществляется запуск одновибратора 20, С выхода

0 схемы 3 сравнения снимается единичный сигнал. С выхода регистра 1 код сигналов текущего состояния интерфейса поступает на вход дешифратора 4. Если код сигналов состояния интерфейса, поступающий с вы5 хода регистра 1, соответствует нормальной последовательности обмена, то на выходе дешифратора 4 сохраняется нулевой сигнал. Установка триггера 21 при этом отсутствует. По сигналу с выхода одновибратора

0 20 осуществляется запись информации с выходов регистров 1 и 8 по адресу, заданному счетчиком 24, а на выходе элемента 9 появляется сигнал, блокирующий появление сигналов на выходе элемента 12 на вре5 мя цикла записи а блок 11 памяти. По заднему фронту сигналя с выхода одновибратора 20 осуществляется модификация счетчика 24 адреса и запись состояния триггера 21 в триггер 25. При отсутствии ошиб- ки, зафиксированной триггером 21, триггер

25 подтвердит свое исходное состояние, а на его инверсном выходе сохранится единичный сигнал. Кроме того, пс переднему фронту сигнала с выхода одновибратора 20 устанавливается триггер 2. На его инверсном выходе появляется нулевой сигнал, подключающий вход сброса таймера 7 через элемент 5 к выходу одновибратора 20. Поскольку на выходе одновибратора 20 присутствует единичный сигнал, то таймер 7 удерживается в исходном состоянии. После окончания сигнала на выходе одновибратора 20 снимается сигнал со входа сброса таймера 7. При последующем поступлении сигналов временных меток с выхода генератора 6 таймер 7 осуществляет отсчет временного интервала. Код текущего значения интервала времени с выхода таймера 7 поступает на вход схемы 10 сравнения, при помощи которой осуществляется сравнение его со значением константы на выходе 29 устройства.

При отсутствии сигнала на вы/оде схемы 1U сравнения, свидетельствующего об окончании допустимого интервала времени, и при изменении состояния сигналов на входе 26 устройства на выходе схемы 3 сравнения появляется единичный сигнал, поступающий на в.ход элемента 12. Дальнейшая работа устройства осуществляется аналогично описанному.

Если в процессе обмена при помощи регистра 1 зафиксирована комбинация сигналов интерфейса, не соответствующая нормальной последовательности, то на выходе дешифратора 4 формируется сигнал ошибок, поступающий на вход элемента 15. На выходе элемента 15 формируется сигнал, в соответствии с которым осуществляется установка триггера 21, а также фиксац ия в регистре 19 адреса ячейки блока 11 памяти, в которую записывалось последнее состояние сигналов интерфейса и фиксация в регистре 19 времени останова.

По заднему фронту сигнала с выхода одновибратора 20 информация с выхода триггера 21 записывается в триггер 25. На инверсном выходе триггера 25 появляется нулевой сигнал останова, блокирующий появление сигналов на выходе элемента 12.

Если в процессе обмена в течение интервала времени, заданного при помощи константы, на выходе 29 устройства изменение состояния сигналов интерфейса отсутствовало, то после поступления очередного сигнала с генератора 6 код на выходе таймера 7 станет равным значению константы из выходе 29, и на выходе схемы 10 сравнения формируется единичный сигнал, поступающий на входы элементов 14 и 15. На.

выходах элементов 14 и 15 формируются сигналы, по которым в регистре 1 фиксируется состояние сигналов интерфейса на входе 26 устройства и осуществляется запуск 5 одновибратора 20. а также установка триггера 21.

Дальнейшая работа устройства осуществляется аналогично описанному.

При запросе магистрали интерфейса 0 для осуществления передачи данных в режиме прямого доступа в память из соотзет ствующего устройства на шину магистрали, подключенной к входу 27 устройства, подается сигнал запроса (BIVi), поступающий на

5 вход регистра 1, вход схемы 3 сравнения и вход элемента 22. На выходе схемы 3 сравнения формируется сигнал, поступающий через элементы 12 и 14 на вход регистра 1. и в регистре 1 фиксируется состояние сигна0 лов интерфейса на входах 26 и 27 устройства. При наличии на выходах регистра 1 сигнала запроса магистрали (ЗМ) в отсутствие сигнала разрешения захвата магистрали (РЗМ) от ведущего устройства на

5 выходе дешифратора 4 присутствует нулевой сигнал, поступающий на вход элемента 16 и блокирующий появление сигнала уста- носки триггера 18. В результате на выходах 35 и 36 устройства появляется информация,

О соответствующая адресу ячейки блока 11. в котирую произведена последняя запись информации, и коду времени останова. Триггер 13 находится в нулевом состоянии, и с его инверсного выхода поступает единич5 ный сигнал, разрешающий передачу сигнала с входа 27 устройства на выход 32 устройства. С выхода 32 устройства сигнал запроса магистрали (ЗМ) поступает на соответствующий вход ведущего устройства

0 магистрали. В ответ на поступление сигнала запроса магистрали (ЗМ) ведущее устройство вырабатывает сигнал разрешения захвата магистрали (РЗМ), передаваемый через устройства системы, а также парал5 лельно с этим поступающий на вход 26 устройства. На выходе схемы 3 сравнения формируется сигнал, поступающий через элементы 12 и 14 на вход регистра 1. В регистре 1 фиксируется состояние сигналов

0 на входах 26 и 27 устройства. С выхода регистра 1 комбинация сигналов, содержащая сигналы запроса магистрали (ЗМ) и разрешения захвата магистрали (РЗМ), поступает на входы блока 11 памяти, схемы 3

5 сравнения и дешифратора 4. На выходе дешифратора 4 вырабатывается единичный разрешающий сигнал, поступающий на вход элемента 16 Поскольку в этот момент времени на выходе схемы 1С сравнения присутствует нулевой сигнал (код на выходе

таймера 7 не равен коду на входе 29 устройства), установка триггера 18 отсутствует. При появлении сигнала подтверждения захвата магистрали (ПЗ) на входе 26 устройства на выходе схемы 3 сравнения формируется сигнал, в соответствии с которым осуществляется запись в регистр 1 состояния сигналов на входах 26 и 27 устройства. На выходе регистра 1 появляется комбинация сигналов, включающая сигнал подтверждения захвата магистрали (ПЗ), а с выхода дешифратора 4 снимается разрешающий сигнал, блокируя установку триггера 18.

Дальнейшая работа устройства осуществляется аналогично описанному.

Если неисправность одного из устройств, через которые транслируется сигнал разрешения захвата магистрали (РЗМ), приводит его к потере для остальных устройств и в результате этого сигнал разрешения не поступает на вход запросившего магистраль устройства, работа системы, магистраль которой контролируется, блокируется и изменение состояния сигналов интерфейса на входах 26 и 27 устройства прекращается. После Поступления очередного сигнала с выхода генератора 6 на вход таймера 7 код на выходе его станет равным значению константы на входе 29 устройства, и на выходе схемы 10 сравнения вырабатывается единичный разрешающий сигнал, поступающий на входы элементов 14-16. На другом входе элемента 16 присутствует единичный разрешающий сигнал. В результате на выходе элемента 16 формируется Сигнал установки триггера 18. Нулевой сигнал с выхода триггера 18 блокируется передачу сигнала с входа 27 на выход 32 устройства. Сигнал запроса магистрали (ЗМ) с выхода 32 устройства снимается, в ответ ведущее устройство сбрасывает сигнал разрешения захвата магистрали (РЗМ) и возобновляется дальнейшая работа контролируемой системы. С прямого выхода триггера 18 на выход 33 поступает сигнал ошибки, свидетельствующий о неисправности одного из устройств системы. Данный сигнал может использоваться в качестве радиального прерывания ведущего устройства магистрали.

В режиме Вывод осуществляется считывание блока 11 памяти зафиксированной в процессе контроля информации по адресам, задаваемым при помощи сигналов на входе 30 устройства, для дальнейшей ее обработки и регистрации на одном из стандартных носителей. Для этого на вход 31 подается сигнал, в соответствии с которым осуществляется подключение входа 30 устройства к адресному входу блока 11 памяти.

Далее на вход 30 устройства подается адрес считываемой ячейки блока 11, на выходе которого появляется информация, содержащаяся в выбранной ячейке и поступающая на выход 34 устройства для дальнейшей обработки.

Формула изобретения Устройство для контроля интерфейса ввода-вывода по авт.св. N: 1383374, отличающееся тем, что, с целью расширения

функциональнах возможностей за счет обеспечения обнаружения ошибок в последовательности передачи управления интерфейсом и исключения данной последовательности при обнаружении

ошибки из набора последовательностей обмена, в него введены второй и третий элементы И и четвертый триггер, причем первый и второй входы и выход второго элемента И соединены с вторым выходом дешифратора состояний интерфейса, выходом второй схемы сравнения и установочным входом четвертого триггера, вход сброса которого подключен к входу сброса устройства, прямой выход четвертого триггера

является выходом признака ошибки устройства, первый и второй входы третьего элемента И соединены соответственно с инверсным выходом четвертого триггера и разрядом признака запроса магистрали информационного входа устройства, а выход третьего элемента И является выходом признака запроса магистрали устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интерфейса ввода-вывода | 1989 |

|

SU1649557A2 |

| Устройство для контроля интерфейса ввода-вывода | 1986 |

|

SU1383374A1 |

| Устройство для контроля интерфейса ввода-вывода | 1991 |

|

SU1798792A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для контроля интерфейса ввода - вывода | 1986 |

|

SU1441410A2 |

| Устройство для контроля интерфейса ввода-вывода | 1990 |

|

SU1829039A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

Изобретение относится к области вычислительной техники. Целью изобретения является расширение функциональных возможностей за счет обеспечения обнаружения ошибок в последовательности передачи управления интерфейсом и исключения данной последовательности при обнаружении ошибки из набора последовательностей обмена. С этой целью в устройство введены второй и третий элементы И и четвертый триггер. 1 ил.

| Устройство для контроля интерфейса ввода-вывода | 1986 |

|

SU1383374A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1988-01-25—Подача