через элемента НЕ , а второй ственно соединены с вюрыми непосред-cooTseiч;твенно третьего н четве{)того входами 1197088.V| элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Устройство связи с дельта-модуляцией | 1986 |

|

SU1365364A1 |

| Дельта-кодер | 1985 |

|

SU1290529A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Устройство для измерения глубины скважины | 1986 |

|

SU1406354A1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

ДЕЛЬТА-КОДЕР,, содержавший соединенные последовательно компаратор, первый вход которого является входом устройства, триггер и регистр сдвига, четыре элемента И, элемент . ИЛИ, элемент эквивалентности, реверсивный счетчик, первый буферный регистр, арифметико-логический блок и цифроаналоговый преобразователь, выход которого соединен с вторым входом компаратора, а входы объединены с соответствующими первыми входами арифметико-логического блока и подключены к выходам первого буферного регистра, входы которого соединены с выходами арифметико-логического блока, управляющий вход которого подключен к выходу триггера, являющемуся выходом устройства, входы синхронизации триггера и регистра сдвига объединены и подключены к гаине синхронизации, прямые и инверсные выходы первого и второго разрядов регистра сдвига со- с первым и вторым входами соответственно первого и второго элементов И, выходы которых подключены к элементу ИЛИ, выходы третьего и четвертого элементов И соединены с входами соответственно обратного и прямого счета реверсивного счетчика, отличающийся тем, что, с целью повышения отношения сигнал/ шум и устранения шумов свободного канала, в него введены первый и второй счетчики, дешифратор, второй и третий буферные регистры, элемент НЕ, блок постоянной памяти и блок мультиплексоров , управляющие, входы которого подключены к выходам реверсивного счетчика, установочные входы которого объединены с соот ветствующими вторыми входами арифметико-логического блока и подключены к выходам третьего буфер ного регистра, входы которого соединены с выходами блока мультиплексо(Л ров , информационные входы которого подключены к первым выходам блока постоянной памяти, вторые -выходы которого соединены с первыми входами элемента эквивалентности,вторые входы которого подключены к выходам второго счетчика, счетный вход косо торого объединен с входом обнуления М первого буферного регистра и Т1 етьио ми входами первого и второго элеменQG 00 тов И и соединен с шиной синхронизации, выход элемента эквивалентности подключен к первым входам третьего и четвертого элементов И и входам обнуления реверсивного счетчика, второго и третьего буферных регистров и лервого и второго счетчиков, счетный вход первого счетчика соединен с выходом элемента ИЛИ, а выходы подключены к входам дешифраторр,первыйи второй выходы которого подключены к соответствующим входам второго буфер ного регистра,первый выход которого

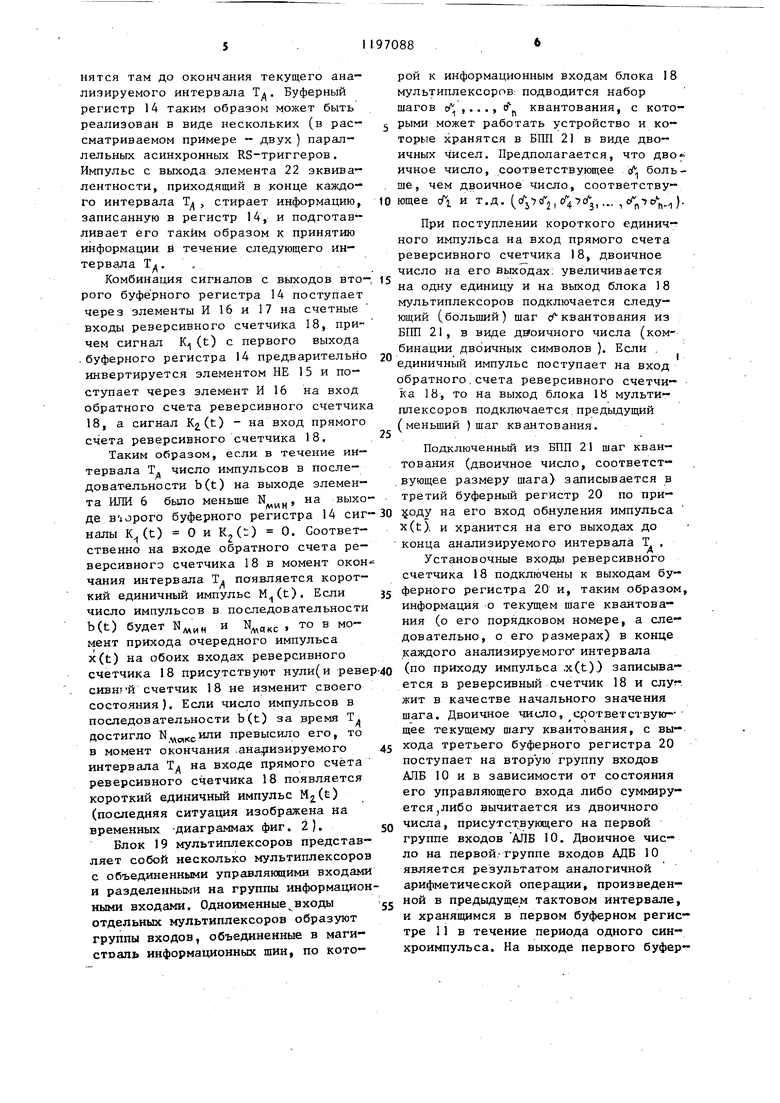

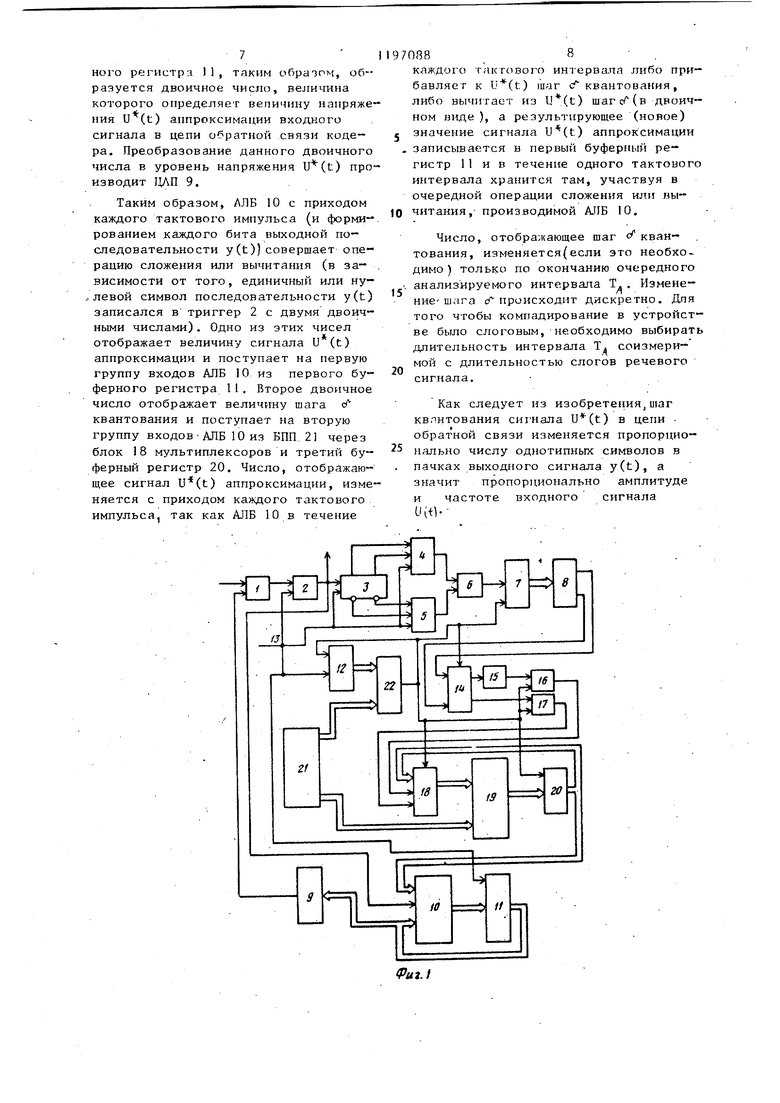

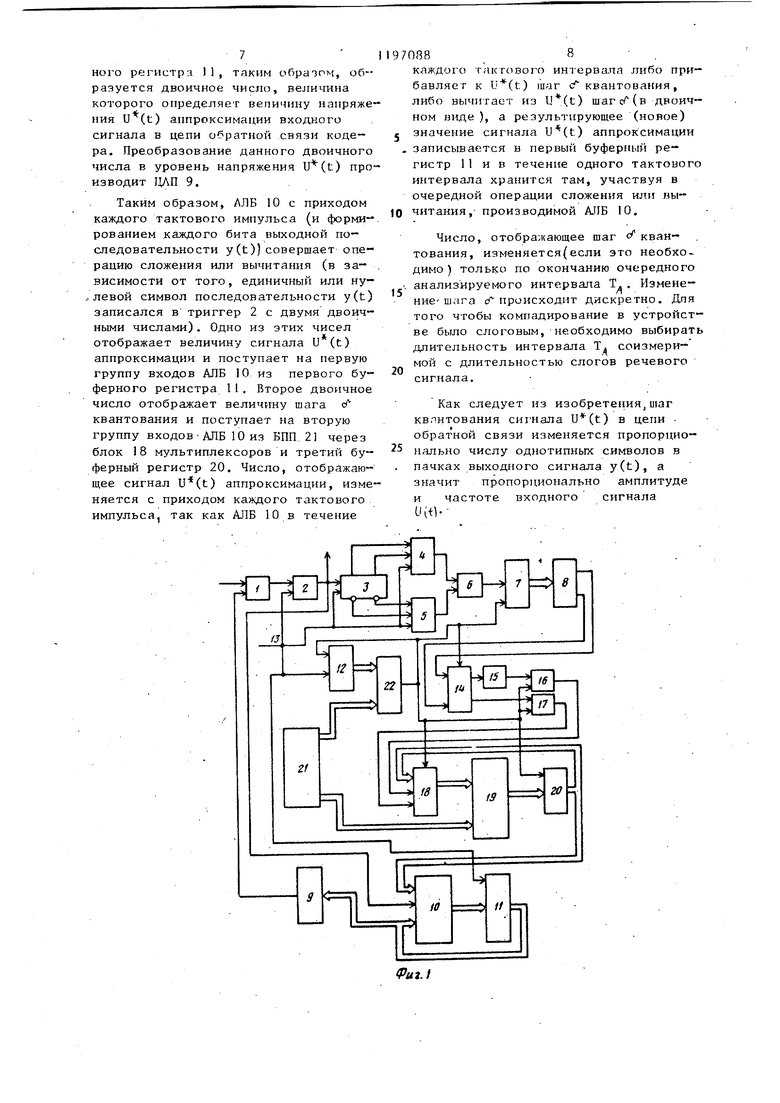

Изобретение относится к вычислительной технике и электросвязи и предназначено для преобразования аналоговых сигналов в нифровую форму Целью изобретения является повышение отношения сигнал/шум и устране ние шумов свободного канала. На фиг. 1 представлена, структурная схема дельта-кодера; на фиг. 2 - временные диаграммы, пояснякяцие работу дельта-кодера; на фиг. 3 структурнГая схема блока мультиплексо ров . Дельта-кодер содержит компаратор 1, первый вход которого является входом устройства, а выход соединен с информационным входом триггера 2, выход которого подключен к информационному входу регистра 3 сдвига. Прямые и инверсные выходы разрядов регистра 3 сдвига подключены к первым двум входам соответственно первого и второго элементов И 4 и 5, вы ходы которых соединены с входами элемента ИЛИ 6, выход которого подключен к счетному входу первого счет чика 7, выходы которого соединены с входами дешифратора 8; второй вход компаратора 1 подключен к выходу циф роаналогового преобразователя (ЦАП) 9, входы которого объединены с соответствующими первыми входами арифметико-логического блока (АЛБ) 10 и подключены к выходам первого буферно го регистра 11, входы которого соеди нены с выходами АЛБ 10, а вход обнуления совместно с счетным входом второго счетчика 12, входами синхронизации триггера 2 и регистра 3 сдви га и третьими входами элементов И А и 5 подключен к шине 13 синхронизации; первый и второй выходы дешифратора 8 соединены с соответствуюшл- ми входами второго буферного регистра 14, первый выход которого через элемент НЕ 15, а второй - непосредст венно подключены к входам соответственно третьего и четвертого элементов И 16 и 17, выходы которых соединены с входами соответственно обратного и прямого счета реверсивного счетчика 18, выходы пос-педнего подключены к управлякщим входам блока 19 мультиплексоров, выходы которого соединены с входами третьего буферного регистра 20, выходы которого подключены к установочным входам реверсивного счетчика 18 и вторым входам АЛБ 10, управляющий вход которого соединен с выходом триггера 2, являющимся выходом устройства. Информационные входы блока 19 мультиплексоров подключены к первым выходам блока 21 постоянной памяти (ВПЛ), вторые выходы которого соединены с первыми входами элемента 22 эквивалентности, вторые входы которого подключены к.выходам второго счетчика 12, а выход -. к другим входам элементов И 16 и 17 и входам обнуления счетчиков 7, 12 и 18 и буферных регистров 14 и 20. На фиг. 2 обозначено: а - последовательность синхроимпульсов с час- тотой fр; б - выходной сигнал y(t) на выходе триггера 2; в и г - сигналы а(с), а.(t) на выходах элементов И 4, 5; д - сигнал b(t) на выходе элемента 6 ИЛИ; е - сигнал x(t) на выходе элемента 22 эквивалентности; ж и 3 - сигналы С (t ), С (t) на выходах дешифратора 8; и и к - выходные сигналы K(t) К (t) второго буферного регистра 14.; л - сигнал К. (t) на выходе элемента НЕ 15; мин- сигналы M(t), M(t) на выходах элементов И 16 и 17. Устройство работает следующим образом. Результаты сравнения компаратором 1 входного U(t) и аппроксимирующего и (t) напряжений в виде единичных или нулевых битов записываются в триггер 2 по информационному входу моменты поступления на его вход синхронизации синхроимпульсов f (фиг. 2а) по шине 13. Цифровая поледовательность y(t) (фиг. 2б) с вы ода триггера 2 является выходным

сигналом кодера и одновременно записывается в регистр 3 сдвига по приходу очеред1а1х синхроимпульсов f на его вход синхронизации. Продвигаясь по регистру 3 сдвига, импульсная последовательность у (t) анализируется элементами И 4 и 5 и элементом ИЛИ 6 на выходе которого генерируются короткие единичные импульсы b(t) (фиг. 2д) всякий раз, когда в последовательности y(t) появляются два (и более ) одинаковых единичных или нулевых символа, следующих подряд. Длительность единичных импульсов b(t) определяется длительностью син- хроимпульсов (;, что обусловлено соединением шины 13 с третьими входами элементов И 4 и 5. Производимое таким образом укорочение импульсов a(t), aj(t) и b(t) необходимо для

обеспечения нормальной работы первого счетчика 7.

Как известно, двух-, и более элементные пачки появляются в выходно сигнале y(t) дельта-кодера тогда, когда сигнал аппроксимации U(t) не может догнать быстро изменяющийся входной сигнал и(t) на протяжении двух и. более тактовыхинтервалов. Наличие многоэлементных пачек в сигнале y(t) свидетельствует о том, что дельта-кодер работает в режиме перегрузки, что сигнал U(t) восстанавливается с большими искажениями из-за слишком малого шага квантования . Присутствие в выходном сигнале у (t) малоэлементных пачек, на протяжении длительного интервала времени ,как правило, свидетельствует о том что шаг квантования с выбран слишком большим и восстанавливаемый сигнал U(t) имеет низкое отношение сигнал/шум из-за большой мощности шумов квантования,

Зная, таким образом, параметры входного сигнала U(t), с которым должен работать дельта-кодер, можно установитьчисло импульсов в последовательности b(t) в течение некоторого анализируемого интервала времени Тд, которое свидетельствует о том, что кодер работает в режиме перегрузки (велика MomHoctb шумов перегрузки ) и что шаг сЛ квантования необходимо увеличить. Обозначим данное число импульсов :N д,ац «

Кроме того, можно установить чис ло импульсов в последовательности

|

bt) в .течение интервала времени Т., которое свидетельствует о том, что кодер работает со слишком большим шагом сГ квантования (а следовательно . низким отношением сигнал/шум квантования), и что шаг квантования с/ необходимо уменьшить. Обозначим данное число импульсов N Очевидно, тогда любое число им-

пульсов b(t) за время Тд между NJ,н будет свидетельствовать о TOM,V что кодер работает с оптимальным шагом квантования, менять который not ка не следует,

Функцию счета импульсов b(t) на интервале Тд в ycTpoficTBe выполняет первый счетчик 7, на счетный вход которого поступает последовательность b(t) с выхода элемента-ИЛИ 5. Периодический интервал времени Тд, на котором проводится анализ выходной последовательности y(t), определяется числом, храня1цимся(в двоичном коде) в БПП 21 и постоянно присутствую-.

щим на второй группе вьшодов БПП 21, а следовательно, и на первой группе входов элемента 22 эквивалентности. Это число должно быть равно количеству тактовых импульсов синхропосле-

довательности f, укладывающихся в интервал Тд, Таким образом, как только второй счётчик 12, счетный вход которого соединен с шиной I3, досчитает до числа, присутствующего на второй

группе выводов БПП 21, так на выходе

элемента 22 эквивалентности появится

единичный импульс X(t) (фиг, 2е),

который, сбросив первый 7 и второй

12 счетчики и поступив в качестве

управляющего и вспомогательного сигнала на другие узлы устройства, отметит конец предыдущего и начало следующего анализируемого интервала Тд выходного сигнала y(t) (а следовательно, и входного сигнала U(t)).

Результаты счета импульсов b(t) первым счетчиком 7 постоянно анализируются дешифратором 8, который на первом своем выходе С (t) генерирует

короткий единичный импульс в тот момент, когда первый счетчик 7 досчитает до J, а на втором выходе С,(t) - такой же импульс, когда счетчик досчитает до N(,.. Резупьтаты анализа последовательностей y(t) и b(t) (сигналы C(t) и C(t)) в момент их появления записываются во второй буферный регистр 14 и хранятся там до окончания текущего ana- лизируемого интервала Т. Буферный регистр 14 таким образом может быть реализован в виде нескольких (в рас- сматриваемом примере - двух ) параллельных асинхронных RS-триггеров. Импульс с выхода элемента 22 эквивалентности, приходящий в конце каждого интервала Тд, стирает информацию, записанную в регистр 14, и подготавливает его таким образом к принятию информации и течение следующего интервала Тд. , ., ,

Комбинация сигналов с выходов вто- рого буферного регистра 14 поступает через элементы И 16 и 17 на счетные входы реверсивного счетчика 18, причем сигнал К,, (t) с первого выхода .буферного регистра 14 предварительно инвертируется элементом НЕ 15 и поступает через элемент И 16 на вход обратного счета реверсивного счетчик 18, а сигнал K(t) - на вход прямого счета реверсивного счетчика 18,

Таким образом, если в течение интервала Т. число импульсов в последовательности b(t) на выходе элемента ИЛИ 6 было меньше ,, на выходе Bloporo буферного регистра 14 сиг налы К(t) О и ) 0. Соответственно на входе обратного счета реверсивного счетчика 18 в момент окоН чания интервала Т. появляется короткий единичный импульс M(t). Если число импульсов в последовательности b(t) будет N,,H и . то в момент прихода очередного импульса x(t) на обоих входах реверсивного счетчика 18 присутствуют нули(и реве сивнмй счетчик 18 не изменит своего состояния). Если число импульсов в последовательности b(t) за время Т достигло превысило его, то в момент окончания .анализируемого интервала Тд на входе прямого счёта реверсивного счетчика 18 появляется короткий единичный импульс П(.) (последняя ситуация изображена на временных -диаграммах фиг. 2).

Блок 19 мультиплексоров представляет собой несколько мультиплексоров с объединенными управляющими входами и разделенными на группы информационными входами. Одноименные входы отдельных мультиплексоров образуют группы входов, объединенные в магистоаль информационных шин, по которой к информационным входам блока I8 мультиплексоров подводится набор шагов сЛ ,... , f квантования, с которыми может работать устройство и которые хранятся в БПП 21 в виде двоичных чисел. Предполагается, что дво ичное число, соответствующее Л больше, чем двоичное число, соответству- ющее cTi и т,д, ( ,... ,оГ1с,.,

При поступлении короткого единичного импульса на вход прямого счета реверсивного счетчика 18, двоичное число на его выходах; увеличивается на одну единицу н на выход блока 18 мультиплексоров подключается следующий (больший) шаг сЛквантования из БПП 21, в виде дэоичного числа (комбинации двоичных символов ), Если . единичный импульс поступает на вход обратного,счета реверсивного счетчика 18, то на выход блока « мультиппексоров подключается предыдущий (меньший ) шаг квантования.

Подключенный из ВПП 21 шаг квантования (двоичное число, соответствующее размеру шага) записывается в третий буферный регистр 20 по при- на его вход обнуления импульса x(t)i и хранится на его выходах до конца анализируемого интервала Т ,

Установочные входы реверсивного счетчика 18 подключены к выходам буферного регистра 20 и, таким образом информация -о текущем шаге квантования (о его порядковом номере, а следовательно, о его размерах) в конце каждого анализируемого интервала (по приходу импульса .x(t).) записывается в реверсивный счетчик 18 и в качестве начального значения шага. Двоичное число, срответствукг-щее текущему шагу квантования, с выхода третьего буферного регистра 20 поступает на вторую группу входов АПБ 10 и в зависимости от состояния его управляющего входа либо суммируется,либо вычитается из двоичного числа, присутствующего на первой группе входов АЛБ 10. Двоичное число на первой.труппе входов ДЦБ 10 является результатом аналогичной арифметической операции, произведенной в предыдущем тактовом интервале, и хранящимся в первом буферном регистре 11 в течение периода одного синхроимпульса. На выходе первого буфер7

Horo регистр: 11, таким образом, образуется двоично( число, величина которого определяет величину напряжения и (t) анпроксимации входного сигнала в цепи обратной связи кодера. Преобразование, данного двоичного числа в уровень напряжения U(f.) производит идп 9.

Таким образом, ЛЛБ 10 с приходом каждого тактового импульса (и формированием каждого бита выходной последовательности у(t))совершает операцию сложения или вычитания (в зависимости от того, единичный или ну.-левой символ последовательности y(t) записался в триггер 2 с двумя двоичными числами). Одно из этих чисел отображает величину сигнала U(t) аппроксимации и поступает на первую группу входов АЛВ 10 из первого буферного регистра II. Второе двоичное число отображает величину шага сЛ квантования и поступает на вторую группу входов-АПК 10 из КПП 21 через блок 18 мультиплексоров и третий буферный регистр 20. Число, отображающее сигнал U(t) аппроксимации, изменяется с приходом каждого тактового импульса, так как АЛБ 10 в течение

0888

каждого тактового интервала либо прибавляет к U(t) шаг « квантования, либо ныч ггаст из U(t) шаг сЛ(в двоичном виде), а результирующее (новое) значение сигнала U(t.) аппроксимации записывается в первый буферный регистр 11 и в течение одного тактового интервала хранится там, участвуя в очередной операции сложения или нычитания,- производимой AJJB 10.

Число, отображающее шаг квантования, изменяется(если это необходимо) только по окончанию очередного анализируемого интервала Т., Изменение-шага сЛ происходит дискретно. Доя того чтобы компадирование в устройстве было слоговым, необходимо выбирать лительность интервала Т. соизмеримой с длительностью слогов речевого сигнала.

Как следует из изобретения,шаг квлнт ования сигнала U(t) в цепи . обратной связи изменяется пропорционально числу однотипных символов в пачках выходного сигнала y(t), а значит пропорционально амплитуде и частоте входного сигнала

u(ti.s,

I Ко tmopvHy L 1уфернему регистру

| Дельта-модулятор | 1983 |

|

SU1129732A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3835385, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-07—Публикация

1984-04-09—Подача