4

(fjua.l

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов.Цель изобретения - повышение точности устройства.

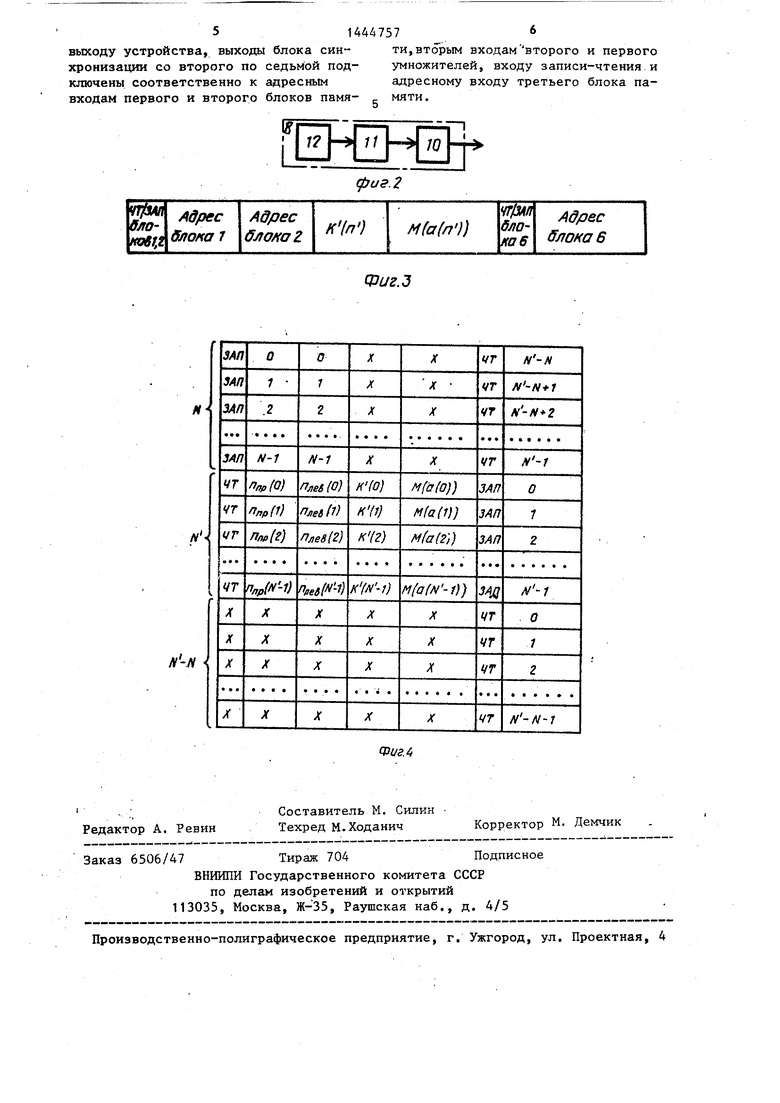

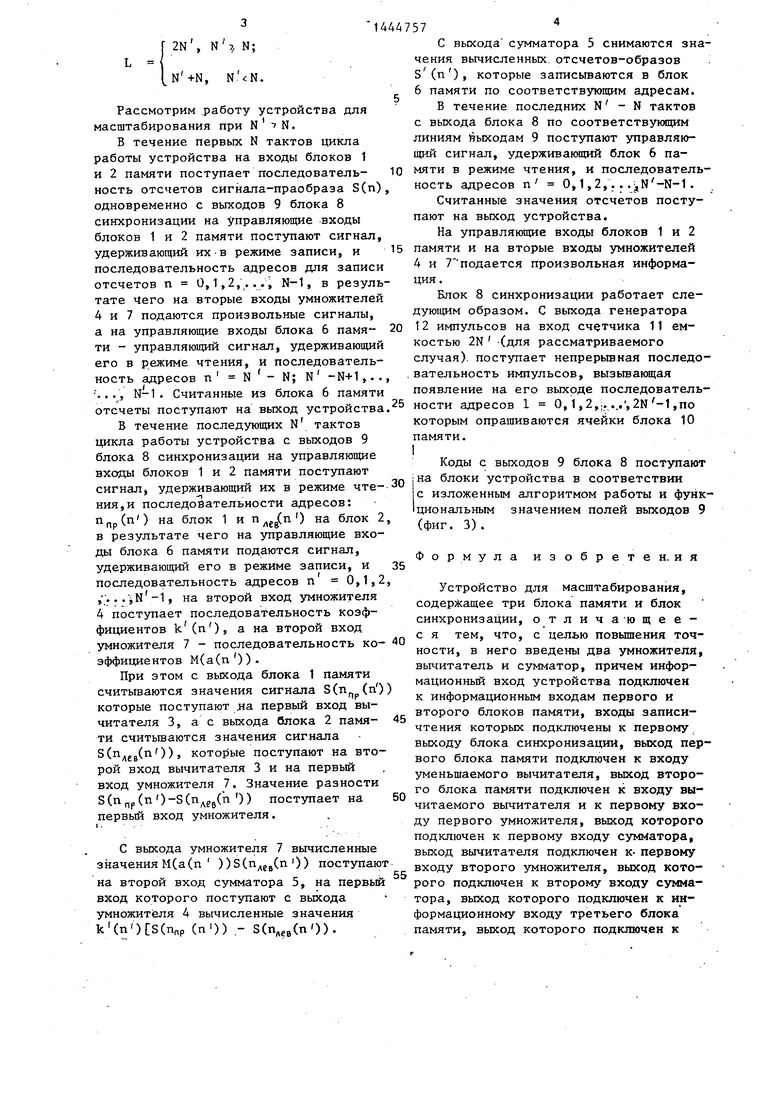

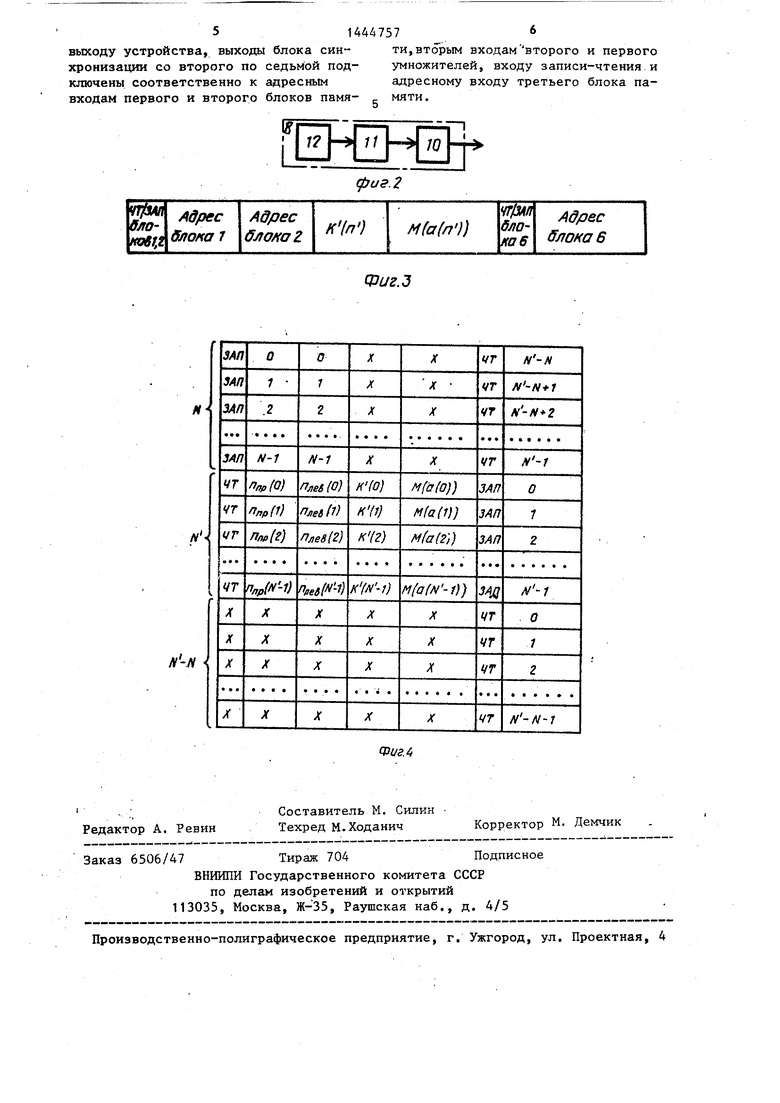

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг, 2 - функциональная схема блока синхронизации; на фиг. 3 - функциональное назначение выходов блока синхронизации; на фиг. 4 - таблица состояний управляющих сигналов (по- тактно).

Устройство содержит блоки 1 и 2 памяти, вычитатель 3, умножитель 4, сумматор 5, блок 6 памяти, умножител 7, блок 8 синхронизации, выходы 9 блока синхронизации, блок 10 памяти, счетчик 11 и генератор 12 импульсов.

Блоки 1, 2 и 6 памяти представляю собой ОЗУ, блок 10 памяти - ПЗУ.

Устройство работает следующим образом.

Отображение сигнала S в новый масштаб аргумента описывается выражением

S(a)-ls (a ) M(a)S(ga) Обозначим

S(ga) S(a ); а ga;

значение аргумента отсчетапраобраза;

значение аргумента отсчета- образа;

оператор отображения (преоб- 40 разования масштаба аргумента) ;

обратный оператор; нормирующий амплитудный множитель, введенный для уравни- вания энергии сигнала-праоб-: раза и сигнала-образа. лучения образа необходимо

задаться начальньп 1 а

на ч

И конечным

значениями нового аргумента, выб-50 рав их из множества а 5 при условии что

|g а«е,ч1 ila l i-l g . (3)

Новый интервал дискретизации а а 55 находится из выражения

da

la кон I а нй NI

(4)

где N - требуемое количество отсчетов в реализации-образе. Тогда значения аргумента для отсчетов-образов будут определяться из вьфажения

а (п ) а ,

мач

Ла п

где п - порядковый номер отсчета- образа, п 0,1,2,:...,, - 1.

Рассчитав все значения множества аргументов а (п )1 ,. необходимо вычислить все значения множества аргументов отсчетов-праобразов а(п )) по формуле (2).

Для каждого из найденных а(п ) необходимо вычислить значение М(а), Поскольку интервал дискретизации и а соответствует требованиям теоремы Котельникова, то при известных значениях отсчетов S(n) и S(n+1) можно вычислить значение любого отсчета для соответствующего значения аргумента S(n+k), где k 1, методом линейной интерполяции отсчетов S(n) и S(n+1) по формуле

S(n+k)k(S(n-f1)-S(n))+S(n). (5)

Вычисленные в количестве интервалов дискретизации значения а(п ) являются значениями П|(п ):

п(п1) а(п ). (6)

Целая часть значения П|.(п ) является значением (п ), дробная часть значения Пк(п ) является значением k(n ). Значение ) находится из вьфажения

p(n ) п,еб (п ) 4 1. (7)

Для всех п рассчитьтаются значения К (п ) по формуле

k (n ) М(а(п )) k(n ), (8)

Из (1) - (8) получим

s4n )k (n)(S(n,(n ))-S(n,; (п ))) + + М(аСп )) S((n X). (9)

Выражение (9) представляет собой алгоритм работы устройства, реализуемый за один рабочий цикл, который в зависимости от соотношения N и N (N - число отсчетов в сигнале-праобразе), содержит L тактов, где

2N

N .

3

, N;

L

N +N, .

25

Рассмотрим .работу устройства для масштабирования при N N.

В течение первых N тактов цикла работы устройства на входы блоков 1 и 2 памяти поступает последователь- Ю кость отсчетов сигнала-праобраза S(n), одновременно с выходов 9 блока 8 синхронизации на управляющие входы блоков 1 и 2 памяти поступают сигнал, удерживающий их-в режиме записи, и 5 последовательность адресов для записи отсчетов п 0,1,2,... N-1, в результате Чего на вторые входы умножителей 4 и 7 подаются произвольные сигналы, а на управляющие входы блока 6 памя 20 ти - управляющий сигнал, удерживающий его в режиме чтения, и последовательность адресов п N - N; N -N+1,. ., .. ., N-1 . Считанные из блока 6 памяти отсчеты поступают на выход устройства

В течение последующих N тактов цикла работы устройства с выходов 9 блока 8 синхронизации на управляющие входы блоков 1 и 2 памяти поступают сигнал, удерживающий их в режиме чтения, и последовательности адресов:

на блок 1 и n jgCn ) на блок 2, результате чего на управляющие входы блока 6 памяти подаются сигнал, удерживающий его в режиме записи, и 35 последовательность адресов п 0,1,2, ,-;.. . jN -1, на второй вход умножителя 4 поступает последовательность коэффициентов k (n ), а на второй вход умножителя 7 - последовательность ко- О эффициентов М(а(п )).

При этом с выхода блока 1 памяти считываются значения сигнала которые поступают ла первый вход вы- читателя 3, ас выхода блока 2 памя- 45 ти считьшаются значения сигнала 5(Пд(пО)5 которые поступают на второй вход вычитателя 3 и на первый вход умножителя 7. Значение разности S(nnp(n )-S((n )) поступает на первый вход умножителя.

-.

С выхода умножителя 7 вычисленные значения М(а(п ))5(Пд55(п )) поступают

30

Ппр(п )

S(n,p(n ))

50

В течение последних N - N тактов с выхода блока 8 по соответствующим линиям йыходам 9 постзтают управляющий сигнал, удерживакиций блок 6 памяти в режиме чтения, и последовательность адресов п 0,1,2,. . .(N -N-1 .

Считанные значения отсчетов поступают на выход устройства.

На управляющие входы блоков 1 и 2 памяти и на вторые входы умножителей 4 и 7 подается произвольная информация .

Блок 8 синхронизации работает сле- ДУЮ1ЦИМ образом. С выхода генератора 12 импульсов на вход счетчика 11 емкостью 2N -(для рассматриваемого случая), поступает непрерьшная последовательность импульсов, вызывающая появление на его выходе последовательности адресов 1 0,1,2,-...,, 2N -1 ,по которым опрашиваются ячейки блока 10 памяти. I

Коды с выходов 9 блока 8 поступают на блоки устройства в соответствии с изложенным алгоритмом работы и функ циональным значением полей выходов 9 (фиг. 3).

Формула изобретен, ия

Устройство для масштабирования, содержащее три блока памяти и блок синхронизации, отлича-ющее- с я тем, что, с целью повышения точности, в него введены два умножителя, вычитатель и сумматор, причем информационный вход устройства подключен к информационным входам первого и второго блоков памяти, входы записи- чтения которых подключены к первому выходу блока синхронизации, выход первого блока памяти подключен к входу уменьшаемого вычитателя, выход второго блока памяти подключен к входу вычитаемого вычитателя и к первому входу первого умножителя, выход которого подключен к первому входу сумматора, выход вычитателя подключен к- первому

входу второго умножителя, выход кото- на второй вход сумматора 5, на первый рого подключен к второму входу сумма- вход которого поступают с выхода тора, выход которого подключен к ин- умножитёля 4 вычисленные значения формационному входу третьего блока k (n )CS(nnp (п )) - 3(Пд5в(п )). памяти, выход которого подключен к

1444757

5

5 0

5 О

5

0

0

С выхода сумматора 5 снимаются значения вычисленных отсчетов-образов S (n ), которые записьгоаются в блок 6 памяти по соответствующим адресам,

В течение последних N - N тактов с выхода блока 8 по соответствующим линиям йыходам 9 постзтают управляющий сигнал, удерживакиций блок 6 памяти в режиме чтения, и последовательность адресов п 0,1,2,. . .(N -N-1 .

Считанные значения отсчетов поступают на выход устройства.

На управляющие входы блоков 1 и 2 памяти и на вторые входы умножителей 4 и 7 подается произвольная информация .

Блок 8 синхронизации работает сле- ДУЮ1ЦИМ образом. С выхода генератора 12 импульсов на вход счетчика 11 емкостью 2N -(для рассматриваемого случая), поступает непрерьшная последовательность импульсов, вызывающая появление на его выходе последовательности адресов 1 0,1,2,-...,, 2N -1 ,по которым опрашиваются ячейки блока 10 памяти. I

Коды с выходов 9 блока 8 поступают на блоки устройства в соответствии с изложенным алгоритмом работы и функциональным значением полей выходов 9 (фиг. 3).

Формула изобретен, ия

Устройство для масштабирования, содержащее три блока памяти и блок синхронизации, отлича-ющее- с я тем, что, с целью повышения точности, в него введены два умножителя, вычитатель и сумматор, причем информационный вход устройства подключен к информационным входам первого и второго блоков памяти, входы записи- чтения которых подключены к первому выходу блока синхронизации, выход первого блока памяти подключен к входу уменьшаемого вычитателя, выход второго блока памяти подключен к входу вычитаемого вычитателя и к первому входу первого умножителя, выход которого подключен к первому входу сумматора, выход вычитателя подключен к- первому

5144- 757

выходу устройства, выходы блока син- ти, вторым входам второго и первого хронизации со второго по седьмой под- умножителей, входу записи-чтения и ключены соответственно к адресным адресному входу третьего блока па- входам первого и второго блоков памя- g мяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для масштабирования | 1989 |

|

SU1649565A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Фурье-Чебышеву | 1983 |

|

SU1136181A1 |

| Устройство для вычисления мультипликативной свертки | 1987 |

|

SU1451723A2 |

| Устройство для вычисления функций | 1987 |

|

SU1411775A1 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Цифровой фильтр | 1987 |

|

SU1390784A1 |

| Устройство для вычисления коэффициентов цифрового фильтра | 1980 |

|

SU961103A1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов. Целью изобретения является повьшение точности. Устройство содержит блоки 1, 2 памяти, вы- читатель 3, умножитель 4, сумматор 5 блок 6 памяти, умножитель 7, блок 8 синхронизации. Поставленная цель достигается за счет учета масштабирукяцих множителей по амплитуде. 4 ил.

(pus.2

сриг.З

| Авторское, свидетельство СССР № 1086428, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США 4378593, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-27—Подача