4 4 4 1

О) СО

Изобретение относится к вычислительной технике и может быть использовано при организации вычислительно- го процесса в многопроцессорной системе.

Цель изобретения - расширение функциональных возможностей устройства за счет увеличения количества обслуживаемых процессоров,

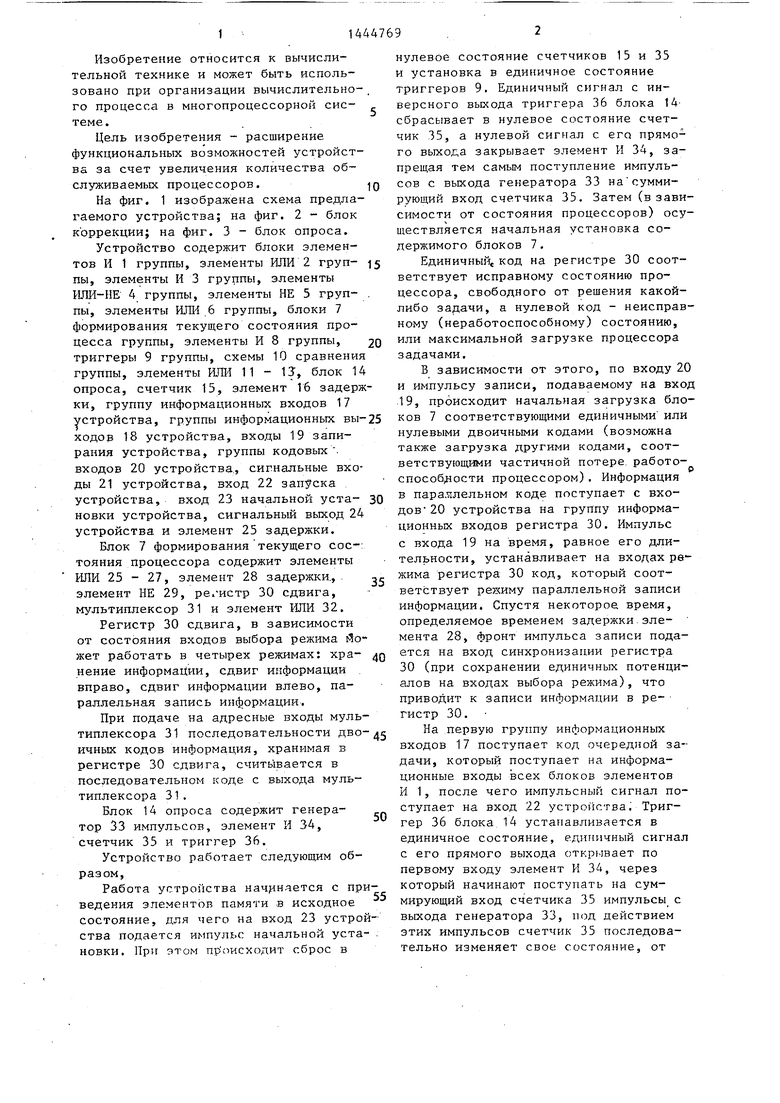

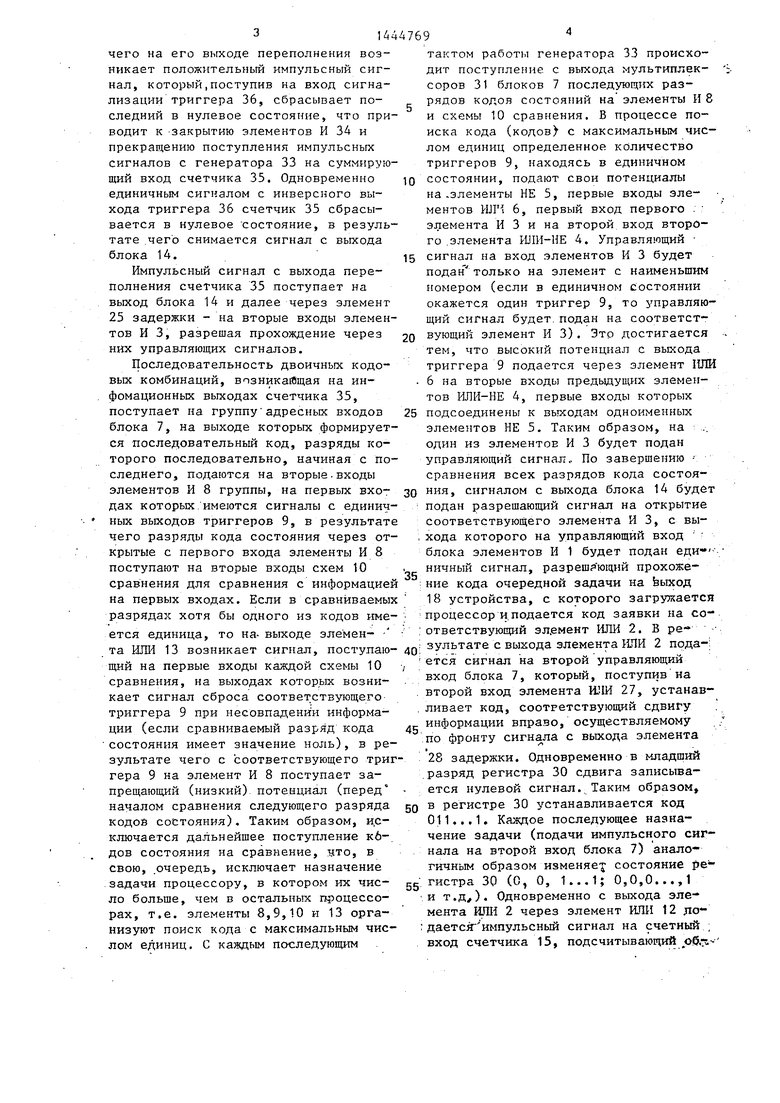

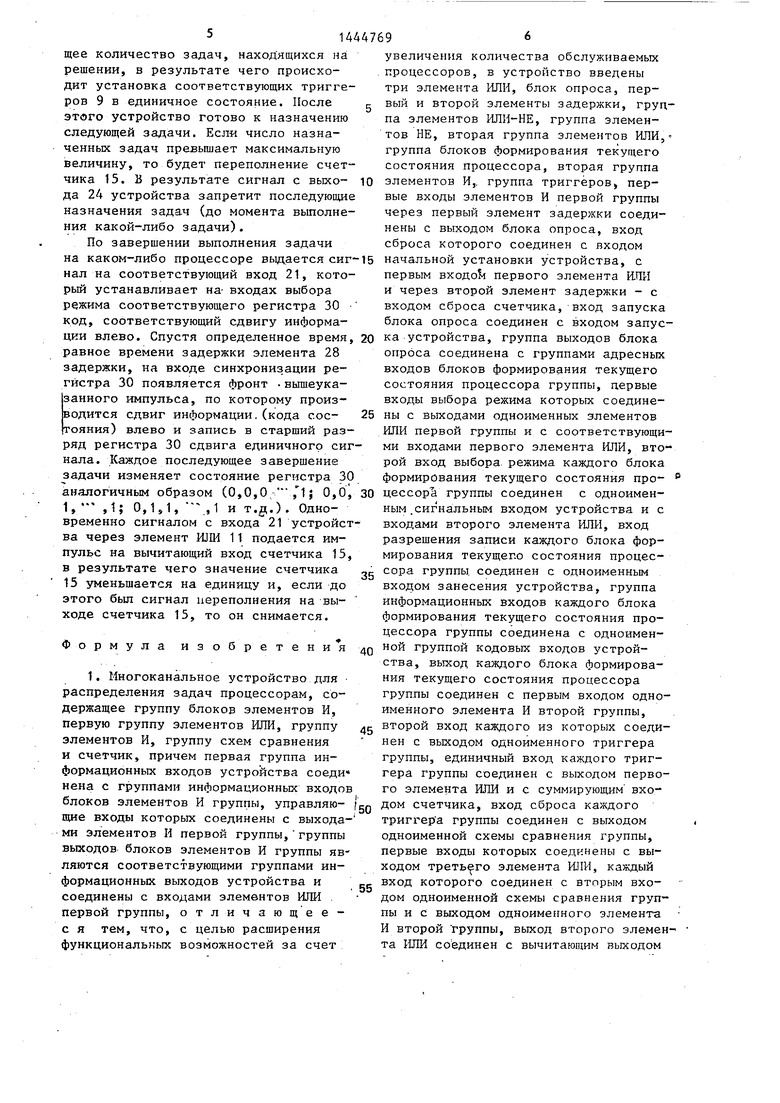

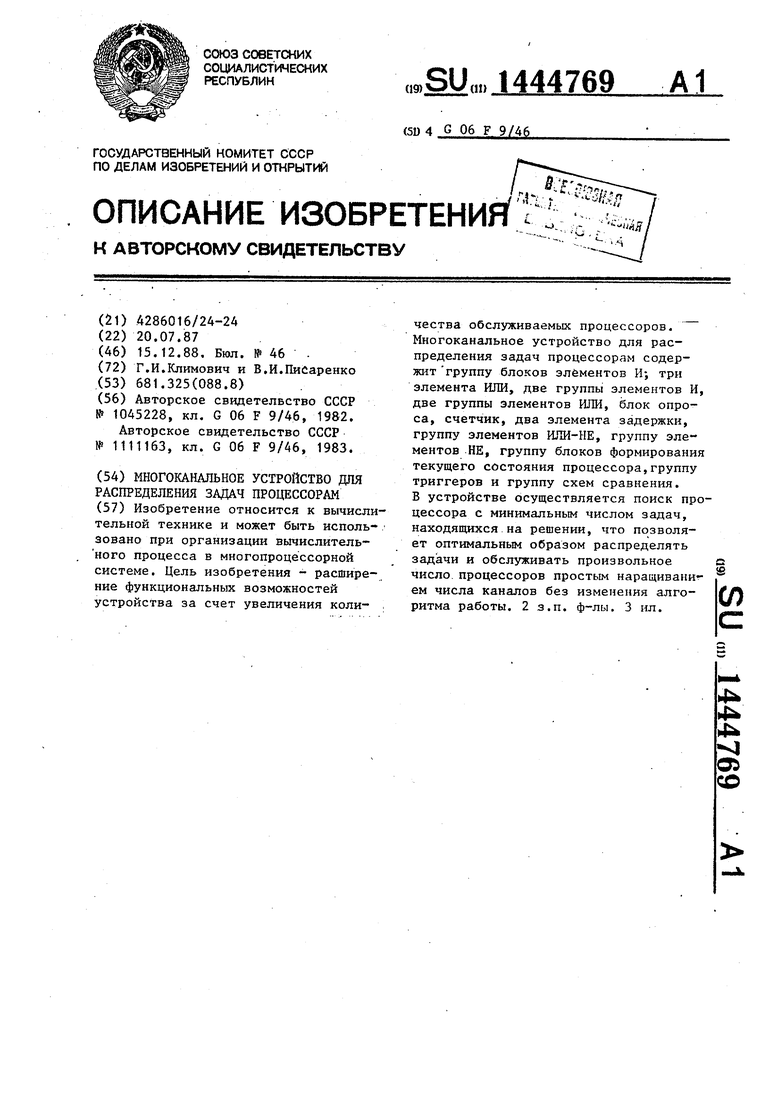

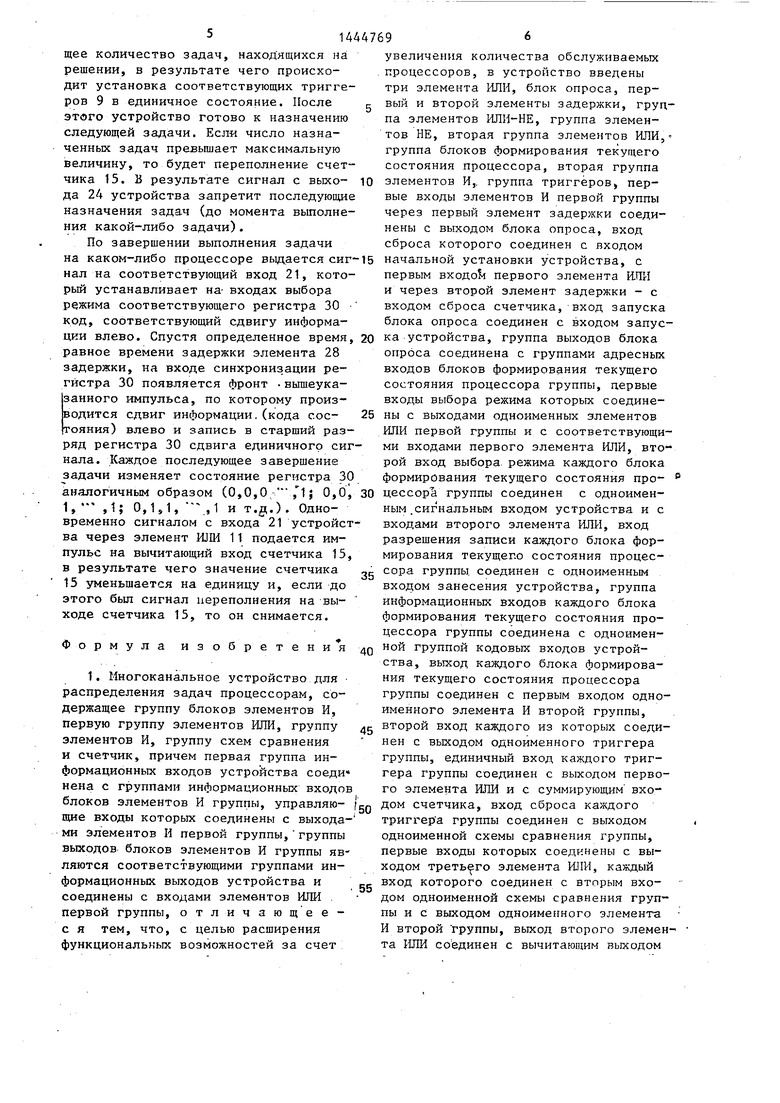

На фиг, 1 изображена схема предлагаемого устройства; на фиг. 2 - блок коррекции; на фиг. 3 - блок опроса.

Устройство содержит блоки элементов И 1 группы, элементы ИЛИ 2 груп- пы, элементы И 3 группы, элементы ИЛИ-НЕ 4 группы, элементы НЕ 5 груп- пы, элементы ИЛИ .6 группы, блоки 7 формирования текущего состояния процесса группы, элементы И 8 группы, триггеры 9 группы, схемы 10 сравнения группы, элементы ИЛИ 11 - 1, блок 14 опроса, счетчик 15, элемент 16 задержки, группу информационных входов 17 устройства, группы информационных выходор 18 устройства, входы 19 запирания устройства, группы кодовых , входов 20 устройства,, сигнальные входы 21 устройства, вход 22 запуска устройства, вход 23 начальной уста- новки устройства, сигнальный выход 24 устройства и элемент 25 задержки.

Блок 7 формирования текущего сое-: тояния процессора содержит элементы ИЛИ 25 - 27, элемент 28 задержки., элемент НЕ 29, ре. истр 30 сдвига, мультиплексор 31 и элемент ИЛИ 32,

Регистр 30 сдвига, в зависимости от состояния входов выбора режима йо- жет работать в четырех режимах: хра- нение информации, сдвиг информации вправо, сдвиг информации влево, параллельная запись информации.

При подаче на адресные входы мультиплексора 31 последовательности двоичных кодов информа.ция, хранимая в регистре 30 сдвига, считывается в последовательном коде с выхода мультиплексора 31 .

Блок 14 опроса содержит генератор 33 импульсов, элемент И 34, счетчик 35 и триггер 36.

Устройство работает следующим образом.

Работа устройства начиняется с приведения элементов памяти а исходное состояние, для чего на вход 23 устройства подается импульс начальной уста- . новки. При этом пр оисходит сброс в

0 0

c

Q

д

0

5

нулевое состояние счетчиков 15 и 35 и установка в единичное состояние триггеров 9. Единичный сигнал с инверсного выхода триггера 36 блока 14- сбрасывает в нулевое состояние счетчик 35, а нулевой сигнал с его прямого выхода закрывает элемент И 34, запрещая тем самым поступление импульсов с выхода генератора 33 на суммирующий вход счетчика 35. Затем (в зависимости от состояния процессоров) осуществляется начальная установка содержимого блоков 7.

Единичный, код на регистре 30 соответствует исправному состоянию процессора, свободного от решения какой- либо задачи, а нулевой код - неисправному (неработоспособному) состоянию, или максимальной загрузке процессора задачами.

В зависимости от этого, по входу 20 и импульсу записи, подаваемому на вход 19, происходит начальная загрузка блоков 7 соответствующими единичными или нулевыми двоичными кодами (возможна также загрузка другими кодами, соответствующими частичной потере, работо- cпocoб ocти процессором) . Информация в параллельном коде поступает с входов 20 устройства на группу информационных входов регистра 30. Импульс с входа 19 на время, равное его длительности, устанавливает на входах режима регистра 30 код, который соответствует режиму параллельной записи информации. Спустя некоторое время, определяемое временем задержки.эле- мента 28, фронт импульса записи подается на вход синхронизации регистра 30 (при сохранении единичных потенциалов на входах выбора режима), что приводит к записи информации в ре- гистр 30.

На первую группу информационных входов 17 поступает код очередной задачи, который поступает на информационные входы всех блоков элементов И 1, после чего импульснь й сигнал поступает на вход 22 устройства. Триггер 36 блока.14 устанавливается в единичное состояние, единичный сигнал с его прямого выхода откр1-1вает по первому входу элемент И 34, через который начинают поступать на суммирующий вход счетчика 35 импульсы с выхода генератора 33, под действием этих импульсов счетчик 35 последовательно изменяет свое состояние, от

чего на его выходе переполнения возникает положительный импульсный сигнал, который,поступив на вход сигнализации триггера 36, сбрасывает последний в нулевое состояние, что приводит к -закрытию элементов И 34 и прекрапдению поступления импульсных сигналов с генератора 33 на суммирующий вход счетчика 35. Одновременно единичным сигналом с инверсного выхода триггера 36 счетчик 35 сбрасывается в нулевое состояние, в результате .чего снимается сигнал с выхода блока 14.

Импульсный сигнал с выхода переполнения счетчика 35 поступает на выход блока 14 и далее через элемент 25 задержки - на вторые входы элементов ИЗ, разрешая прохождение через них управляющих сигналов.

Последовательность двоичных кодовых комбинаций, впзникайщая на ин- фомационных выходах счетчика 35, поступает на группу адресных входов блока 7, на выходе которых формируется последовательный код, разряды которого последовательно, начиная с последнего, подаются на вторые-входы элементов И 8 группы, на первых входах которых имеются сигналы с единич- ных выходов триггеров 9, в результате чего разряды кода состояния через открытые с первого входа элементы И 8 поступают на вторые входы схем 10 сравнения для сравнения с информацией на первых входах. Если в сравниваемых разрядах хотя бы одного из кодов имеется единица, то на-выходе элемен- - та ШШ 13 возникает сигнал, поступающий на первые входы каждой схемы 10 сравнения, на выходах которых возникает сигнал сброса соответствующего триггера 9 при несовпадении информации (если сравниваемый разряд кода состояния имеет значение ноль), в результате чего с соответствующего триггера 9 на элемент И 8 поступает запрещающий (низкий) потенциал (перед началом сравнения следующего разряда кодой состояния). Таким образом, исключается дальнейшее поступление к6-. дов состояния на сравнение, уто, в свою, .очередь, исключает назначение задачи процессору, в котором их число больше, чем в остальных процессорах, т.е. элементы 8,9,10 и 13 организуют поиск кода с максимальным числом единиц. С каждым последующим

тактом работы генератора 33 происходит поступление с выхода мультиплексоров 31 блоков 7 последующих разрядов кодов состояний на элементы И 8 и схемы 10 сравнения. В процессе поиска кода (кодов) с максимальньм числом единиц определенное количество триггеров 9, находясь в единичном

0 состоянии, подают свои потенциалы на .элементы НЕ 5, первые входы элементов ИЛМ 6, первый вход первого . элемента И 3 и на второй вход второго .элемента ШШ-НЕ 4. Управляющий

5 сигнал на вход элементов И 3 будет подан только на элемент с наименьшим номером (если в единичном состоянии окажется один триггер 9, то управляющий сигнал будет, подан на соответст0 вующий элемент И 3). Этр достигается тем, что высокий потенциал с выхода триггера 9 подается через элемент 1ШЙ . 6 на вторые входы предьщущих элементов ИЛИ-НЕ 4, первые входы которых

5 подсоединены к выходам одноименных элементов НЕ 5. Таким образом, на один из элементов И 3 будет подан управляющий сигнал.. По завершению сравнения всех разрядов кода состоя0 ния, сигналом с выхода блока 14 будет подан разрешающий сигнал на открытие соответствующего элемента ИЗ, с вы- , хода которого на управляющий вход блока элементов И 1 будет подан еди- - ничный сигнал, разрешрющий прохоже- ние кода очередной задачи на Ьыход 18 устройства, с которого загружается iпроцессор и.подается код заявки на со- ; ответствующий эл.емент ИЛИ 2. В ре- зультате с выхода элемента 1ИИ 2 пода5

0

ется сигнал на второй управляющий

вход блока 7, который, поступив на . второй вход элемента ШШ 27, устанав- . ливает код, соотретствующий сдвигу информации вправо, осуществляемому по фронту сигнала с выхода элемента

28 задержки. Одновременно в младший разряд регистра 30 сдвига записывается нулевой сигнал. Таким образом, 0 в регистре 30 устанавливается код 011...1. Казкдое последующее назначение задачи (подачи импульсного сигнала на второр вход блока 7) аналогичным образом иsмeняeJ состояние ре- 5 гистра 30 (О, О, 1...1; 0,0,0...,

и т.д,). Одновременно с выхода элемента ШШ 2 через элемент ИЛИ 12 до; дается импульсный сигнал на счетный ; вход счетчика 15, подсчитывающий об,щее количество задач, решении, в результате

находящихся па чего происхоувеличения количества обслуживаемых процессоров, в устройство введены три элемента ИЛИ, блок опроса, первый и второй элементы задержки, груп па элементов ИЛИ-НЕ, группа элементов НЕ, вторая группа элементов ИЛИ, группа блоков формирования текущего состояния процессора, вторая группа элементов И,, группа триггеров, первые входы элементов И первой группы через первый элемент задержки соединены с выходом блока опроса, вход сброса которого соединен с входом

дит установка соответствующих триггеров 9 в единичное состояние. После этого устройство готово к назначению следующей задачи. Если число назначенных задач превышает максимальную величину, то будет переполнение счетчика 15. В результате сигнал с выхо- ю да 24 устройства запретит последующие назначения задач (до момента выполнения какой-либо задачи).

По завершении выполнения задачи

на каком-либо процессоре выдается сиг-15 начальной установки устройства, с нал на соответствующий вход 21, кото- первым входов первого элемента ИПИ рый устанавливает на- входах выбора режима соответствующего регистра 30 код, соответствующий сдвигу информации влево. Спустя определенное время, равное времени задержки элемента 28 задержки, на входе синхронизации регистра 30 появляется фронт вышеука- 1занного импульса, по которому производится сдвиг информации.(кода сос- ггояния) влево и запись в старший разряд регистра 30 сдвига единичного сигнала. Каждое последующее завершение задачи изменяет состояние регистра 30

аналогичным образом (0,0,0,,1; 0,OJ 30 цессор группы соединен с одноимен- 1, ,1; 0,1,1, ,1 и т.(.). Одно- ным .сигнальным входом устройства и с временно сигналом с входа 21 устройст- входами второго элемента ИЛИ, вход ва через элемент ИЛИ 11 подается им20

25

и через второй элемент задержки - с входом сброса счетчика, вход запуска блока опроса соединен с входом запуска устройства, группа выходов блока опроса соединена с группами адресных входов блоков формирования текущего состояния процессора группы, первые входы выбора режима которых соединены с выходами одноименных элементов ИЛИ первой группы и с соответствующими входами первого элемента ИЛИ, вто рой вход выбора режима каждого блока формирования текущего состояния про-

разрешения записи каждого блока формирования текущего состояния процессора группы, соединен с одноименным входом занесения устройства, группа информационных входов каждого блока формирования текущего состояния процессора группы соединена с одноименной группой кодовых входов устройства, выход каждого блока формирования текущего состояния процессора группы соединен с первым входом одноименного элемента И второй группы, 45 второй вход каждого из которых соединен с выходом одноименного триггера группы, единичный вход каждого триггера группы соединен с выходом первого элемента ИЛИ и с суммирующим вхопульс на вычитающий вход счетчика 15, в результате чего значение счетчика 15 уменьшается на единицу и, если до этого был сигнал переполнения на выходе счетчика 15, то он снимается.

Формула изобретени я

1. Многоканальное устройство для распределения задач процессорам, содержащее группу блоков элементов И, первую группу элементов ИЛИ, группу элементов И, группу схем сравнения и счетчик, причем первая группа информационных входов устройства соеди« нена с группами информационных входов

увеличения количества обслуживаемых процессоров, в устройство введены три элемента ИЛИ, блок опроса, первый и второй элементы задержки, группа элементов ИЛИ-НЕ, группа элементов НЕ, вторая группа элементов ИЛИ, группа блоков формирования текущего состояния процессора, вторая группа элементов И,, группа триггеров, первые входы элементов И первой группы через первый элемент задержки соединены с выходом блока опроса, вход сброса которого соединен с входом

начальной установки устройства, с первым входов первого элемента ИПИ

цессор группы соединен с одноимен- ным .сигнальным входом устройства и с входами второго элемента ИЛИ, вход

и через второй элемент задержки - с входом сброса счетчика, вход запуска блока опроса соединен с входом запуска устройства, группа выходов блока опроса соединена с группами адресных входов блоков формирования текущего состояния процессора группы, первые входы выбора режима которых соединены с выходами одноименных элементов ИЛИ первой группы и с соответствующими входами первого элемента ИЛИ, вто рой вход выбора режима каждого блока формирования текущего состояния про-

цессор группы соединен с одноимен- ным .сигнальным входом устройства и с входами второго элемента ИЛИ, вход

разрешения записи каждого блока формирования текущего состояния процессора группы, соединен с одноименным входом занесения устройства, группа информационных входов каждого блока формирования текущего состояния процессора группы соединена с одноименной группой кодовых входов устройства, выход каждого блока формирования текущего состояния процессора группы соединен с первым входом одноименного элемента И второй группы, второй вход каждого из которых соединен с выходом одноименного триггера группы, единичный вход каждого триггера группы соединен с выходом первого элемента ИЛИ и с суммирующим вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1179364A1 |

| Устройство для выбора по приоритету | 1989 |

|

SU1619274A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| Устройство для формирования очереди | 1986 |

|

SU1446626A1 |

| СПОСОБ АВТОМАТИЧЕСКОГО ГРУППОВОГО ВОЖДЕНИЯ ДОРОЖНЫХ МАШИН И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2017 |

|

RU2664033C1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1594543A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1984 |

|

SU1211734A1 |

Изобретение относится к вычислительной технике и может быть использовано при организации вычислитель- ного процесса в многопроцессорной системе. Цель изобретения - расширение функциональных возможностей устройства за счет увеличения количества обслуживаемых процессоров. Многоканальное устройство для распределения задач процессорам содержит группу блоков элементов И; три элемента ИЛИ, две группы элементов И, две группы элементов ИЛИ, блок опроса, счетчик, два элемента задержки, группу элементов ИЛИ-НЕ, группу элементов НЕ, группу блоков формирования текущего состояния процессора,группу триггеров и группу схем сравнения. В устройстве осуществляется поиск процессора с минимальным числом задач, находящихся.на решении, что позволяет оптимальным образом распределять задачи и обслуживать произвольное с число, процессоров простым наращиваниг- ем числа каналов без изменения алгоритма работы. 2 з.п. ф-лы. 3 ил. (Л

блоков элементов И группы, управляю- fgQ дом счетчика, вход сброса каждого

щие входы которых соединены с выхода- ми элементов Н первой группы, группы выходов блоков элементов И группы являются соответствующими группами информационных выходов устройства и соединены с входами элементов ИЛИ . первой группы, отличающ ее- с я тем, что, с целью расширения функциональных возможностей за счет

55

триггер а группы соединен с выходом одноименной схемы сравнения группы первые входы которых соединены с в ходом третьего элемента ИЛИ, кажды вход которого соединен с вторым вх дом одноименной схемы сравнения гр пы и с выходом одноименного элемен И второй группы, выход второго эле та 1ШИ соединен с вычитающим выход

5

триггер а группы соединен с выходом одноименной схемы сравнения группы, первые входы которых соединены с выходом третьего элемента ИЛИ, каждый вход которого соединен с вторым входом одноименной схемы сравнения группы и с выходом одноименного элемента И второй группы, выход второго элемента 1ШИ соединен с вычитающим выходом

.5

10

15

счетчика, выход переполнения счетчика соединен с сигнальным выходом устройства, второй вход первого элемента И первой группы соединен с выходом первого триггера группы, с первым входом первого элемента ИЛИ второй группы и с первым .входом первого элемента ШШ-НЕ группы, второй вход каждого элемента И первой группы, начиная с второго, соединен с выходом элемента ИЛИ-КЕ группы, начиная с первого, второй вход первого элемента ИЛИ второй группы соединен с выходом второго триггера группы и через первый элемент НЕ группы - с вторым вх.одом первого элемента ИЛИ-ИЕ группы, выход i-rp (,...п-1, где п - число обслужива емых процессоров) элемента ИЛИ второй группы соединен с первыми ВХОДАМИ (i+1)-ro элемента ИЛИ второй группы и с первым входом (i+1)-ro элемента ИЛИ-НЕ группы, вторые входы элементов ИЛИ-ИЕ группы соединен1: с вьЬсодами соответствующих 25 элементов НЕ группы, вторые входы элементов ИЛИ второй группы соединены с выходами соответствующих триггеров группы, входы элементов НЕ группы, начиная с второго, соединены с выхода- р ;ми соответствующих триггеров группы.

20

1

40

к выходу элемента И, второй вход кото- рого соединен с выходом генератора импульсов, информационные выходы счетчика являются группой выходов блока, выход переполнения счетчика подключен к тактовому входу триггера и является выходом блока.

.5

10

15

25

А47693

с вторым входом второго элемента ИЛИ и является первым входом выбора режима блока, выход первого элемента ИЛИ подключен к входу элемента -задержки, выход которого соединен с входом синхронизации регистра сдвига, вход сдвига влево которого подключен к выходу элемента НЕ, вход которого соединен с входом сдвига вправо регистра сдвига .и подключен к входу логического нуля устройства, информационные входы регистра сдвига образуют группы информационных входов блока, выходы второго и третьего элементов ИЛИ со- едине ы соответственно с первым и вто- входами выбора режима регистра сдвига, информационные выходы которого подключены к информационным входам мультиплексора, адресные входы которого образуют группу адресных входов блока, выход мультиплексора является выходом блока.

20

1

к выходу элемента И, второй вход кото- рого соединен с выходом генератора импульсов, информационные выходы счетчика являются группой выходов блока, выход переполнения счетчика подключен к тактовому входу триггера и является выходом блока.

Фаз 2

.д

| Устройство для управления обслуживанием запросов | 1982 |

|

SU1045228A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий между ЭВМ | 1983 |

|

SU1111163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-20—Подача