Изобретение относится к вычислительной технике и может быть использовано в системах диагностирования цифровых объектов.

Целью изобретения является расширение функциональных возможностей за счет опроса заданного количества входов в .период между подачей тестовых воздействий.

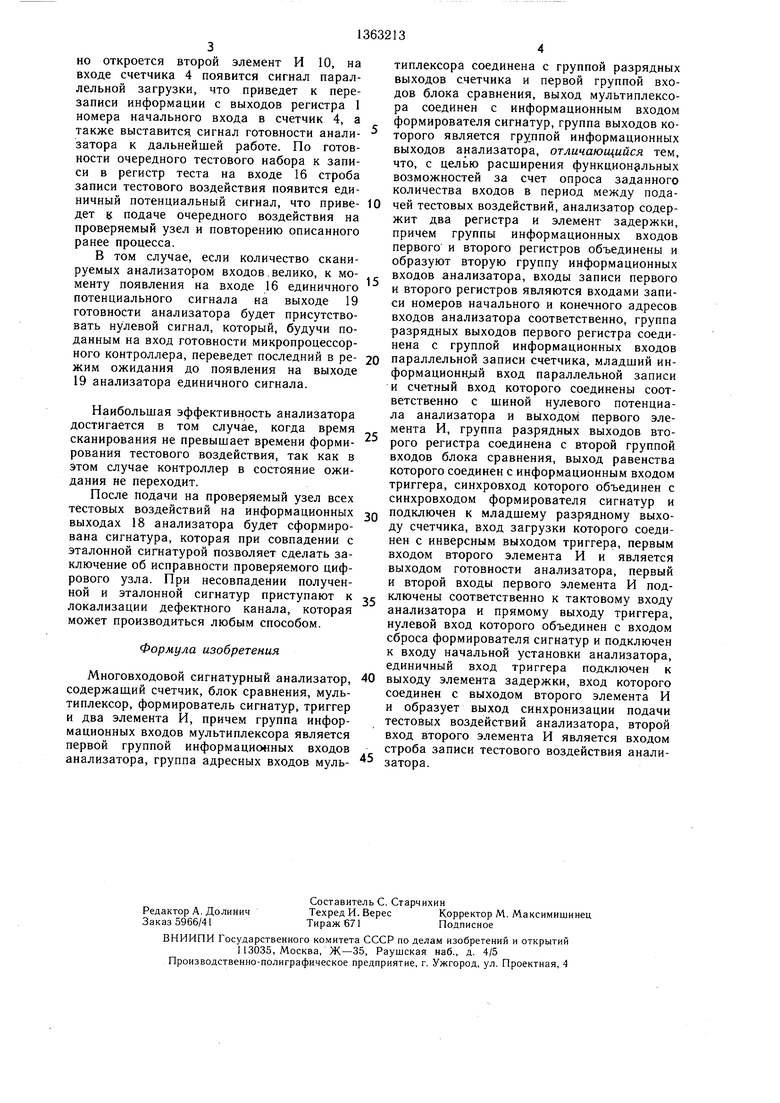

На чертеже представлена структурная схема входового сигнатурного анализатора

счетчик 4, мультиплексор 5, блок 6 сравнения, формирователь 7 сигнатур, триггер 8, элемент 9 задержки, второй элемент И 10, входы 11 и 12 записи соответственно регистров начального и конечного адресов входов анализатора, вторая группа информационных входов 13 анализатора тактовый вход 14 анализатора, вход 15 начальной установки анализатора, вход 16 строба зазатора, который определяет первый проверяемый вход, происходит коммутация начального входа на информационный вход формирователя 7 сигнатур.

Начало проведения проверки определяется подачей на вход 16 строба записи тестового воздействия единичного потенциального сигнала, свидетельствующего о готовности тестового набора к записи в регистр теста (не показан). Ввиду того.

Анализатор содержит первый регистр 1, 10 что второй элемент И 10 находится в от- второй регистр 2, первый элемент И 3, крытом состоянии, то строб записи проходит

через анализатор и поступает на выход 20 синхронизации подачи тестовых воздействий. По окончании записи информации в регистр сигнал с входа 16 строба записи тестового воздействия снимается. С выходов регистра теста на проверяемый цифровой узел поступает тестовое воздействие. После завершения переходных процессов, связанных с переключением элементов объекта

писи тестового возде йствия, первая группа 20 контроля, на входах 17 анализатора фик- информационных входов 17 анализатора, сируются реакции проверяемого узла на по- информационные выходы 18 анализатора, данное тестовое воздействие, при этом с выход 19 готовности анализатора, выход 20 выхода элемента 9 задержки поступает сиг- синхронизации подачи тестовых воздействий. нал, переключающий триггер 8 в единич- Многовходовой сигнатурный анализатор ное состояние, что приводит к снятию с работает под управлением микропроцессор- 25 выхода 19 сигнала готовности, закрытию ного контролера (не показан), в функ- второго элемента И 10 и открытию пер- ции которого входит управление режима вого элемента И 3. Нулевой логический проверки, связь с внешними устройствами сигнал с инверсного выхода триггера 8 памяти и центральной ЭВМ, а также запрещает параллельную запись информа- генерация совокупности тестовых воздейст- Ции в счетчик 4. Под действием такто- вий для проверяемого цифрового узла. По- вых импульсов, поступающих через открытый

первый элемент И 3 на счетный вход счетчика 4, счетчик 4 последовательно меняет свое состояние, причем по фронту каждого нечетного импульса младший разряд устанавливается в единичное состояние, а по фронту каждого четного импульса происходит изменение состояния разрядов, подключ,енных к адресным входам мультиплексора 5 и первой группе входов блока 6 сравнения. По фронту импульса, поступульсов через первый элемент И 3 на счет- 40 пающего с младшего разряда счетчика 4, ный вход счетчика 4. Единичный потен- в формирователе 7 сигнатур происходит циал на инверсном выходе триггера 8 сдвиг и сжатие информации, коммутируе- выставляет сигнал параллельной загрузки мой мультиплексором 5 с входов 17 ана- на входе счетчика 4, открывает второй эле- лизатора на информационный вход формиро- мент И 10 и выставляет на выходе 19 вателя 7, а также синхронизация записи сигнал готовности. На информационные информации по информационному входу входы 13, совмещенные с шиной данных триггера 8. Описанный процесс будет микропроцессорного контролера, последовательно выставляются коды начального и конечного адресов входов, которые по сигналам записи, подаваемым на входы 11 и 12 анализатора, записываются в соответствующие регистры 1 и 2. Так как на входе счетчика 4 присутствует сигнал загрузки, то информация с выходов регистра 1 номера начального адреса переписывается в

счетчик 4, младший разряд которого уста- 55 8 переключится в нулевое состоя- навливается в нулевое состояние. На ад- ние, закроется первый элемент И 3 и ресных входах мультиплексора 5 устанавли- прекратится подача тактовых импульсов вается код номера начального адреса анали- на счетный вход счетчика 4. Одновремендача тестов на объект контроля синхронизируется сигнатурным анализатором.

Анализатор работает следующим образом.

На вход 15 начальной установки подается импульсный сигнал, который устанавливает формирователь 7 сигнатур и триггер 8 в нулевое состояние. Нулевой потенциал на прямом выходе триггера 8 закрывает путь прохождения тактовых им35

50

продолжаться до тех пор, пока код текущего входа анализатора, определяемый состоянием разрядов счетчика 4, подключенных к адресным входам мультиплексора 5 и первой группе входов блока 6 сравнения, не сравняется с кодом номера конечного входа, хранимого в регистре 2. При этом на выходе блока 6 сравнения появится нулевой потенциальный сигнал.

пающего с младшего разряда счетчика 4, в формирователе 7 сигнатур происходит сдвиг и сжатие информации, коммутируе- мой мультиплексором 5 с входов 17 ана- лизатора на информационный вход формиро- вателя 7, а также синхронизация записи информации по информационному входу триггера 8. Описанный процесс будет

8 переключится в нулевое состоя- ние, закроется первый элемент И 3 и прекратится подача тактовых импульсов на счетный вход счетчика 4. Одновремен

продолжаться до тех пор, пока код текущего входа анализатора, определяемый состоянием разрядов счетчика 4, подключенных к адресным входам мультиплексора 5 и первой группе входов блока 6 сравнения, не сравняется с кодом номера конечного входа, хранимого в регистре 2. При этом на выходе блока 6 сравнения появится нулевой потенциальный сигнал.

3

но откроется второй элемент И 10, на входе счетчика 4 появится сигнал параллельной загрузки, что приведет к перезаписи информации с выходов регистра 1 номера начального входа в счетчик 4, а также выставится сигнал готовности анали- затора к дальнейшей работе. По готовности очередного тестового набора к записи в регистр теста на входе 16 строба записи тестового воздействия появится единичный потенциальный сигнал, что привё- дет к подаче очередного воздействия на проверяемый узел и повторению описанного ранее процесса.

В том случае, если количество сканируемых анализатором входов.велико, к моменту появления на входе 16 единичного потенциального сигнала на выходе 19 готовности анализатора будет присутствовать нулевой сигнал, который, будучи поданным на вход готовности микропроцессорного контроллера, переведет последний в ре- жим ожидания до появления на выходе 19 анализатора единичного сигнала.

Наибольшая эффективность анализатора достигается в том случае, когда время сканирования не превышает времени формирования тестового воздействия, так как в этом случае контроллер в состояние ожидания не переходит.

После подачи на проверяемый узел всех тестовых воздействий на информационных выходах 18 анализатора будет сформирована сигнатура, которая при совпадении с эталонной сигнатурой позволяет сделать заключение об исправности проверяемого цифрового узла. При несовпадении полученной и эталонной сигнатур приступают к локализации дефектного канала, которая может производиться любым способом.

Формула изобретения

Многовходовой сигнатурный анализатор, содержащий счетчик, блок сравнения, мультиплексор, формирователь сигнатур, триггер и два элемента И, причем группа информационных входов мультиплексора является первой группой информационных входов анализатора, группа адресных входов муль-

Составитель С. Старчихин

Техред И. ВересКорректор М. Максимишинец

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

0

0

5

5

о

0

5

типлексора соединена с группой разрядных выходов счетчика и первой группой входов блока сравнения, выход мультиплексора соединен с информационным входом формирователя сигнатур, группа выходов которого является группой информационных выходов анализатора, отличающийся тем, что, с целью расширения функциональных возможностей за счет опроса заданного количества входов в период между подачей тестовых воздействий, анализатор содержит два регистра и элемент задержки, причем группы информационных входов первого и второго регистров объединены и образуют вторую группу информационных входов анализатора, входы записи первого и второго регистров являются входами записи номеров начального и конечного адресов входов анализатора соответственно, группа разрядных выходов первого регистра соединена с группой информационных входов параллельной записи счетчика, младший ин- формационн 1Й вход параллельной записи и счетный вход которого соединены соответственно с шиной нулевого потенциала анализатора и выходом первого элемента И, группа разрядных выходов второго регистра соединена с второй группой входов блока сравнения, выход равенства которого соединен с информационным входом триггера, синхровход которого объединен с синхровходом формирователя сигнатур и подключен к младшему разрядному выходу счетчика, вход загрузки которого соединен с инверсным выходом триггера, первым входом второго элемента И и является выходом готовности анализатора, первый и второй входы первого элемента И подключены соответственно к тактовому входу анализатора и прямому выходу триггера, нулевой вход которого объединен с входом сброса формирователя сигнатур и подключен к входу начальной установки анализатора, единичный вход триггера подключен к выходу элемента задержки, вход которого соединен с выходом второго элемента И и образует выход синхронизации подачи тестовых воздействий анализатора, второй вход второго элемента И является входом строба записи тестового воздействия анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах диагностирования цифровых объектов. Целью изобретения является расширение функциональных возможностей за счет опроса заданного количества входов в период между подачей тестовых воздействий. Анализатор содержит два регистра 1 и 2, первый элемент И 3, счетчик 4, мультиплексор 5, блок 6 сравнения, формирователь 7 сигнатур, триггер 8, элемент 9 задержки, второй элемент И 10. Сигнатурный анализатор в процессе работы за период между подачей двух последовательных тестовых воздействий производит с помощью мультиплексора опрос всех входов контролируемого объекта в диапазоне между начальным и конечным адресами, записываемыми соответственно в первый и второй регистры. 1 ил. i сл со 05 со to со

| Сигнатурный анализатор | 1983 |

|

SU1180896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-22—Подача