Изобретение отнЬсится к автоматике и предназначено для формирования на- о пряжения, пропорционального интегралу от входного сигнала. Оно может использоваться в системах автоматического управления различными объектамиjj, когда требуются большие постоянные интегрирования,

Целью изобретения является повыше- Q с ние точности записи начальных условий в интегратор.

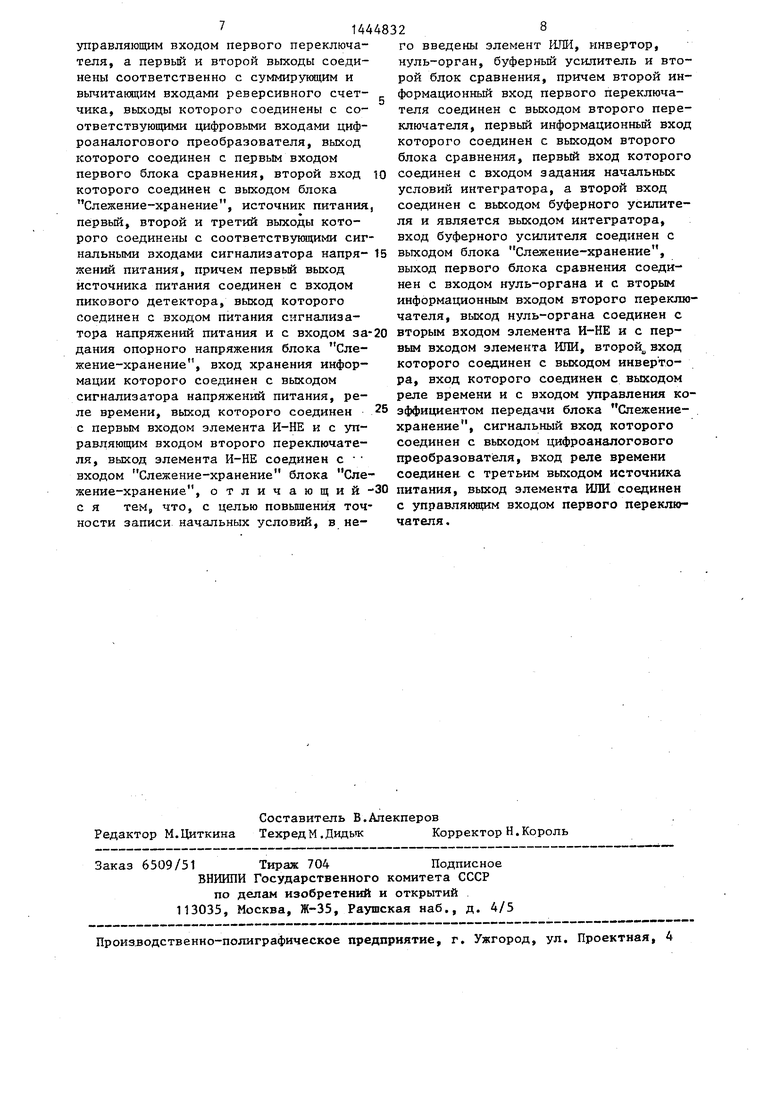

На чертеже приведена схема аналого-цифрового интегратора.

Интегратор содержит первьй пере- 5 ключатель 1, преобразователь 2 напря-- жение - частота, реверсивньш счетчик 3, цифроаналоговый преобразователь 4, блок 5 Слежение-хранение, первый блок 6 сравнения, нуль-орган 7, элемент И-НЕ 8, инвертор 9, элемент ИЛИ 10, источник 11 питания, пиковьй детектор 12, сигнализатор 13 напряжений питания, реле 14 времени, буферный усилитель 15, второй блок 16 сравне-f 25

ны о ж ч и н пр

с н п п

пр г п 20 с

вх к з в

ния, второй, переключатель 17.

Блок 5 Слежение-хранение содержит первый и второй масштабные резисторы ,18 и 19, зарядный резистор 20, два переключателя 21 и 22, операционньй усилитель 23, запоминающий конденса тор 24, МОП-транзистор 25.

Для рассматриваемого интегратора характерны следующие режимы работы: интегрирование, восстановление информации после сбоев счетчика и кратковременных перерывов в подаче питания и запись начальных условий.

В режиме интегрирования устройство работает после окончания переходных процессов в цепях питания и прихода реле 14 времени во включенное состояв

30

35

40

с н в

л

ка хо ло ра ни ро пр вх ви од ра ин то

выходной сигнал имеет единичное значение, по которому переключатели 17, 22 удерживаются в нижнем положении. При этом выходные напряжения источника 11 питания имеют номинальные значения и сигнализатор 13 напряжений питания и пиковый детектор 12 переводят МОП- транзистор 25 в открытое состояние, в результате чего запоминающий конденсатор 24 подключается к выходу операционного усилителя 23.

Исходное состояние контура восстановления информации, включающего в се бя блок 5 Слежение-хранение, первьй блок 6 сравнения, нуль-орган 7, и элементы И-НЕ 8 и ИЛИ 10, соответствует

с

равенству абсолютных значений выходных напряжений цифроаналогового преобразователя 4 () и блока 5 Слежение-хранение (Uf,), в результате чего выходные сигналы нуль-органа 7 и элемента ИЛИ 10 имеют нулевые значения и переключатель 1 соединяет вход преобразователя 2 напряжение-частота

входом устройства (Ug) а элемент И-НЕ 8 удерживает ключ 21 в замкнутом состоянии, и блок 5 Слежение-хранение работает в режиме слежения за напряжением с выхода цифроаналогового преобразователя 4.

При наличии входного сигнала U 0 преобразователь 2 напряжение-частота генерирует импульсы с частотой f vi, пропорциональной U , которые в зави- симости от знака U поступают на

входы + или - реверсивного счетчика 3. За каждьй период работы преобразователя 2 в счетчике 3 фиксируются величина и знак приращения интеграла

входного напряжения U, т.е. осуще

0

5

0

5

0

5 величину, ствляется квантование интеграла входного сигнала по уровню. Таким образом, в счетчике 3 формируется цифровой

код N, характеризующий , кото . - t

рьй с помощью цифроаналогового преобразователя 4 преобразуется в эквива- . лентное электрическое напряжение.

При нормальной работе аналого-цифрового интегратора (без сбоев счетчика) блок 5 Слежение-хранение находится в режиме слежения за сигналом с выхода цифроаналогового преоб разователя 4, причем скорость слежения выбирается выше максимальной скорости изменения напряжения на выходе преобразователя 4, а приведенная к входу блока 6 сравнения зона нечувствительности нуль-органа 7 не менее одного кванта сигнала с выхода преобразователя 4 и контур восстановления информации находится в исходном состоянии, рассмотренном выше.

Если в процессе интегрирования (или хранения интеграла при УВЯ произойдет сбой счетчика 3, то из-за ограниченной скорости слежения блока 3 Слежение-хранение сигналы на вхо дах блока 6 сравнения отличаются на

превышающую зону нечувствительности. На выходе блока б сравне - ния возникает напряжение, знак которого определяется рассогласованием

сигналов Уцдп п Р этом нуль- орган 7 формирует независимо от знака рассогласования единичное значение логического сигнала, по которому элемент И-НЕ 8 переводит ключ 21 в разомкнутое состояние, и блок 5 Слежение-хранение переходит в режим поддержания напряжения, предшествующего сбою счетчика 3 (режим хранения).

Одновременно по единичному значению выходного сигнала элемента ИЛИ 10 переключатель 1 соединяет вход преобразователя 2 напряжение-частота через переключатель 17 с выходом блока 6 сравнения. Под действием сигнала с вы хода блока 6 сравнения преобразователь 2 восстанавливает информацию в

Поскольку сигнализатор 13 напряжезапоминающего конденсатора 24 при условии выхода из допустимой зоны хотя бы одного напряжения питания, нарушения нормальных состояний узлов

счетчике 3, т.к. подача импульсов на

один из входов счетчика 3 осуществля-20 питания обеспечивает отключение ется до тех пор, пока разность напряжений с выхода блока 5 Слежение-хранение и цифроаналогового преобразователя 4 не снизится до величины, при которой произойдет отключение нуль-ор-25 интегратора, возникающие после этого, гана 7. После этого выходной сигнал приводят к изменению заряда на за- нуль-органа 7 принимает нулевое зна- поминающем конденсаторе. Необходимые чение, а следовательно, переключатель . значения напряжений на подложке МОП- 1 подключает вход преобразователя 2 к транзистора 25 и на выходе сигнализа- входу устройства (U), ключ 21 пере- зо сохраняются в течение перерыходит в замкнутое состояние, а блок 5 Слежение-хранение - в режим слежег ния за сигналом Ущп и схема возвращается в прежнее состояние, обеспечивая дальнейшее формирование интеграла от входного сигнала Ug.

Для уменьшения погрешности интегратора, связанной с изменением потенциала на запоминающем конденсаторе 24 при работе блока 5 Слежение-хранение в режиме хранения, необходимо увеличивать частоту преобразователя 2 напряжение-частота, т.е. сокращать время восстановления информации. Это достигается тем, что при срабатьюании нуль-органа 7 преобразователь 2 сигналом, поступающим на вход перестройки частоты с нуль-органа 7 через элемент ИЛИ 10, перестраивается на по- вьпиенную частоту следования импуль40

на питания за счет пикового детектора 12. Кратковременные перерывы питания не приводят к запуску реле времени 14, и состояние переключателей 17 и 22 в этом режиме соответствует исходному.

Появление напряжения U. в. питающей сети после кратковременного его исчезновения вызывает увеличение выходных напряжений источника 11 питания от нулевых значений до номинальных. При этом состояние сигнализатора 13, соответствующее закрытому МОП-транзистору 25, сохраняется до тех пор, пока хотя бы одно из этих напряжений находится вне допустимой зоны. Как только последнее из них примет допустимое значение, при котором на все узлы интегратора поступают напряжения питания, близкие к номинальным, сигнализатор 13 релейно изменяет полярность своего выходного сигнала, МОП-транзистор 25 открывается и на выходе блока 5 Слежение-хранение устанавливается напряжение u|,, определенное 55 потенциалом на конденсаторе 24 и близкое по значению напряжению Up, которое было на нем до перерыва в подаче питания. Если 11 то срабатывает

45

сов ,.

Работа интегратора в режиме восстановления информации при кратковременных перерывах питания происходит следующим образом.

При исчезновении напряжения Uj в питающей сети выходные напряжения источника 11 питания уменьшаются до нулевых уровней с различными постоян

ными времени. Пока они близки к номинальным значениям, сигнализатор 13 напряжений питания поддерживает МОП- транзистор 25 в открытом состоянии. Но как только хотя бы одно из выходных напряжений источника 11 питания выйдет из допустимой зоны, выходной сигнал, сигнализатора 13 релейно изменяет свою полярность, что приводит к закрыванию МОП-транзистора 25. В результате этого запоминающий конденсатор 24 оказьтается отключенным от операционного усилителя 23 и напряжение на нем за время перерьша питания изменяется относительно первоначального уровня (UQ) на незначительную величину.

Поскольку сигнализатор 13 напряжезапоминающего конденсатора 24 при условии выхода из допустимой зоны хотя бы одного напряжения питания, нарушения нормальных состояний узлов

питания обеспечивает отключение интегратора, возникающие после этого, приводят к изменению заряда на за- поминающем конденсаторе. Необходимые значения напряжений на подложке МОП- транзистора 25 и на выходе сигнализа- сохраняются в течение переры

0

на питания за счет пикового детектора 12. Кратковременные перерывы питания не приводят к запуску реле времени 14, и состояние переключателей 17 и 22 в этом режиме соответствует исходному.

Появление напряжения U. в. питающей сети после кратковременного его исчезновения вызывает увеличение выходных напряжений источника 11 питания от нулевых значений до номинальных. При этом состояние сигнализатора 13, соответствующее закрытому МОП-транзистору 25, сохраняется до тех пор, пока хотя бы одно из этих напряжений находится вне допустимой зоны. Как только последнее из них примет допустимое значение, при котором на все узлы интегратора поступают напряжения питания, близкие к номинальным, сигнализатор 13 релейно изменяет полярность своего выходного сигнала, МОП-транзистор 25 открывается и на выходе блока 5 Слежение-хранение устанавливается напряжение u|,, определенное 5 потенциалом на конденсаторе 24 и близкое по значению напряжению Up, которое было на нем до перерыва в подаче питания. Если 11 то срабатывает

5

0

514448326

нуль-орган 7 и в интеграторе происхо- временная задержка, формируемая реле дит восстановление информации подоб- 14 времени, с - постоянная времени но тому, как это имеет место при сбо- заряда конденсатора 24. При выполне- ях счетчика.нии этих соотношений конденсатор 24

Работа интегратора в режиме записи в конце вьиержки времени р0 оказы- начальных условий происходит следую- вается заряженным до уровня выходного щим образом.напряжения ()„) усилителя 23, соотЕсли после длительного нахождения ветствующего условию Ug(,,Un,j, а на- генератора в обесточенном состоянии jg пряжение на выходе блока 6 сравнения он подключается к питающей сети, то близко к нулевому уровню (т.к. 11, в первый момент времени выходной сиг- ицдп) и выходной сигнал нуль-органа нал реле 14 времени имеет нулевое зна- 7 в конце C pg имеет нулевое значение, чение. При этом переключатели 17 и 22 После окончания задержки tp выход- устанавливаются в верхнее положение, 15 ой сигнал реле 14 времени принимает а переключатели 1 и 21 - в нижнее не- единичное значение, что приводит к из- зависимо от состояния нуль-органа 7. менению состояния переключателей 7 Рассогласование UUu,,j-Ugy с выхо- 22 и 1,, и интегратор переходит в ре- да второго блока 16 сравнения поетупа- жим интегрирования входного сигнала, ет через переключатели 17 и 1 на вход 20 При этом выходное напряжение блока 5 преобразователя 2 напряжение - часто- Слежение-хранение не изменяется, та, который настраивается (по входу так как левая обкладка конденсатора перестройки частоты) на повьшенную 24 переключается мезвду точками, на- частоту следования импульсов ( пряжения в которых практически равны сигналом с элемента ИЛИ 10, принимаю- 25 нулю (ток заряда конденсатора отсутст- щим в этом случае единичное значение вует, усилитель 23 работает в линей- за счет инвертора 9.ном режиме и потенциал на его инПо нулевому значению сигнала реле вертирующем входе определяется смеще- 14 времени переключатель 22 отключает нием нуля усилителя, т.е. не превы- конденсатор 24 от инвертирующего вхо- ЗО шает нескольких мшшивольт). да усилителя 23 и подключает его к ре- За счет того, что в режиме записи зистору 20, в результате чего блок 5 начальных условий конденсатор 24 вы- Слежение-хранение переходит в режим ключается из цепи отрицательной об- аналогового инвертора, коэффициент ратной связи усилителя 23 и заряжа- передачи которого определяется отноше- с ется через резистор 20, а в конце за- нием сопротивлений резисторов 19 и 18. держки pg безударно подключается Конденсатор 24 при этом обеспечивает к усилителю 23, достигается безынерци- выходное напряжение усилителя 23, за- онность блока Слежение-хранение и ряжаясь через резистор 20, переключа- устраняется самовозбуждение аналого- тель 22 и открытый МОП-транзистор 25. 40 цифрового интегратора .в этом режиме, В результате в этом режиме преобразо- в результате чего исключаются динами- ватель 2 напряжение - частота, рабо- ческие составляющие погрешности запитая на повьшенной частоте fсц обес- си начальных условий, связанные с ука- печивает быстрое изменение кода в занными факторами. Погрешность прер- счетчике 3 до тех пор, пока рассогла- 45 ложенного интегратора в этом регкиме сование bUnu на выходе блока 16 срав- определяется практически только бло- нения не станет равным нулю, т.е. до ком 16 сравнения (его смещением нуля) выполнения условия Ug,UHU Время, и неидеальностью входных цепей. которое требуется для достижения этого условия (т.е. фактическое время за-5о Формулаизобретения писи начальных условий t цц) определяется в основном частотой импульсов Аналого-цифровой интегратор, со- f на выходе преобразователя 2 и зна- держащий первьй переключатель, первьй чением записываемого в счетчик 3 кода. информационный вход которого является

Обеспечение нормальной работы инте-55 входом интегратора, а выход соединен гратора в режиме записи начальных ус- с информационным входом преобразовате- Ловий связано с вьшолнением соотноше- ля напряжение - частота, вход пере- тй Грв Ьц,.рИ ,, где с рв - стройки частоты которого соединен с

14448328

управляющим входом первого переключа- го введены элемент ИЛИ, инвертор, теля, а первьй и второй выходы соеди- нуль-орган, буферный усилитель и вто- нены соответственно с суммирующим и рой блок сравнения, причем второй ин- вьгчитаницим входами реверсивного счет- формационный вход первого переключа- чика, выходы которого соединены с со- теля соединен с выходом второго пере- ответствующими цифровыми входами циф- ключателя, первый информационный вход роаналогового преобразователя, выход которого соединен с выходом второго которого соединен с первым входом блока сравнения, первый вход которого первого блока сравнения, второй вход ю соединен с входом задания начальных которого соединен с выходом блока условий интегратора, а второй вход Слежение-хранение, источник питания, соединен с выходом буферного усилите- первый, второй и третий выходы кото- ля и является выходом интегратора, рого соединены с соответствующими сиг- вход буферного усилителя соединен с нальными входами сигнализатора напря- 15 вьпсодом блока Слежение-хранение, жений питания, причем первый выход выход первого блока сравнения соеди- источника питания соединен с входом нен с входом нуль-органа и с вторым пикового детектора, выход которого информационным входом второго переклю- соединен с входом питания сигнализа- чателя, выход нуль-органа соединен с тора напряжений питания и с входом за-20 вторым входом элемента И-НЕ и с пер- дания опорного напряжения блока Сле- вым входом элемента ИЛИ, второй вход жение-хранение, вход хранения инфор- которого соединен с выходом инверто- мации которого соединен с выходом ра, вход которого соединен с выходом сигнализатора напряжений питания, ре- реле времени и с входом управления коле времени, выход которого соединен 25 эффициентом передачи блока Слежение- с первым входом элемента И-НЕ и с уп- хранение, сигнальный вход которого равляющим входом второго переключате- соединен с выходом цифроаналогового ля, выход элемента И-НЕ соединен с преобразователя, вход реле времени входом Слежение-хранение блока Сле- соединен с третьим выходом источника жение-хранение, отличающий -30 питания, выход элемента ИЛИ соединен с я тем, что, с целью повышения точ- с управлякшщм входом первого переклю- ности записи начальных условий, в не- чателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1988 |

|

SU1534473A2 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Аналого-цифровой интегратор | 1989 |

|

SU1672477A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Программная следящая система | 1981 |

|

SU1108394A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU813456A2 |

| Аналого-цифровой интегратор | 1973 |

|

SU507872A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Устройство для управления четырехфазным двигателем переменного тока | 1983 |

|

SU1138918A2 |

Изобретение может найти примене ние при автоматизации различных технологических процессов. Целью изобре тения является повышение точности записи начальных условий. Аналого- цифровой интегратор содержит первый переключатель 1, преобразователь 2 напряжение - частота, реверсивный счетчик 3, цифроаналоговый преобразователь 4, блок 5 Слежение-хранение, первый блок 6 сравнения, нуль-орган 7, элемент И-НЕ 8, инвертор 9, элемент ИЛИ 10, источник 11 питания, пиковый детектор 12, сигнализатор 13 напряжений питания, реле 14 времени, буферный усилитель 15, второй блок 16 сравнения, второй переключатель 17. Сущность изобретения состоит в том, что в режиме записи начальных условий путем подачи питания на интегратор по сигналу реле времени происходит изменение структуры интегратора, в результате чего рассогласование между его выходньм напряжением и сигналом начальных условий уменьшается до нуля. 1 ил. § ила 4 4 4 ОО СО to

| Аналого-цифровой интегратор | 1973 |

|

SU507872A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-15—Подача