(54) АНАЛОГО-ЦИФРОВОЙ ИНТЕГРАТОР

34

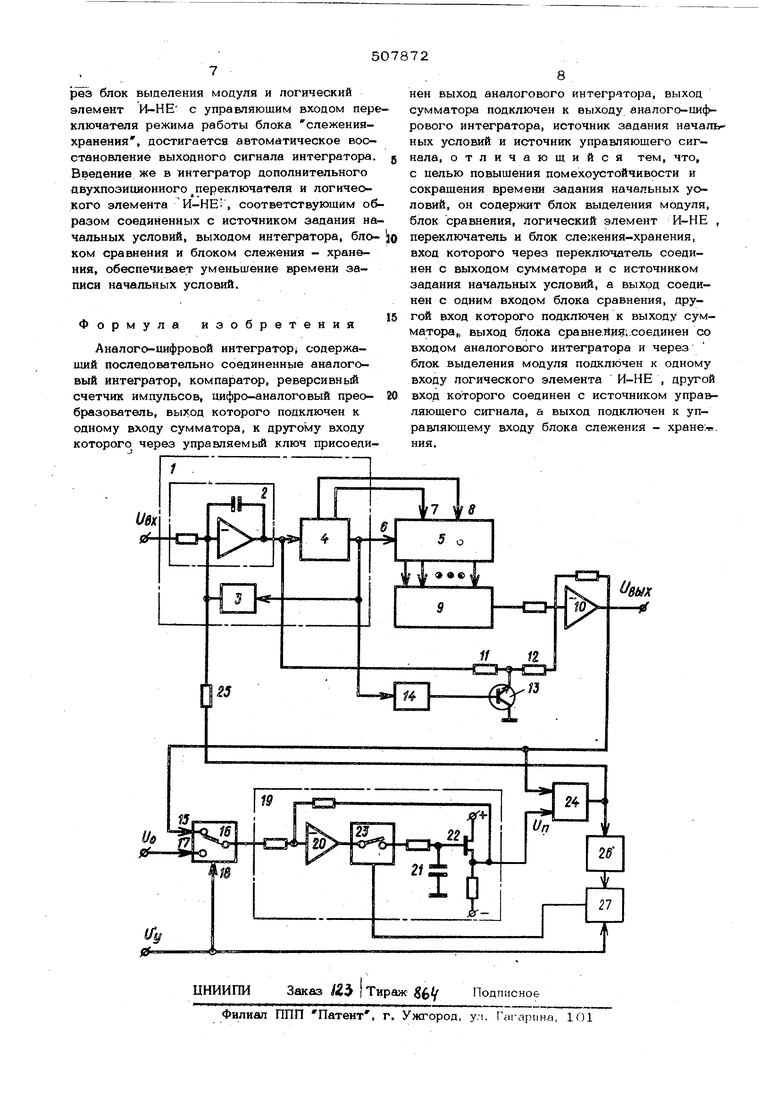

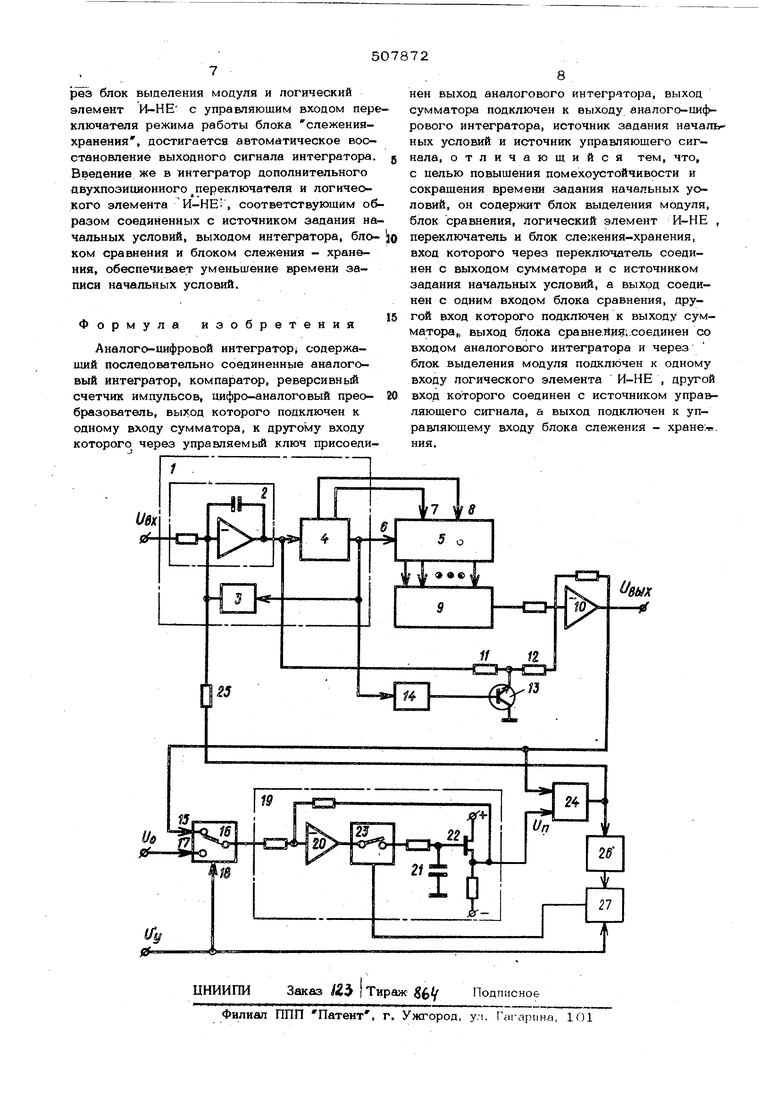

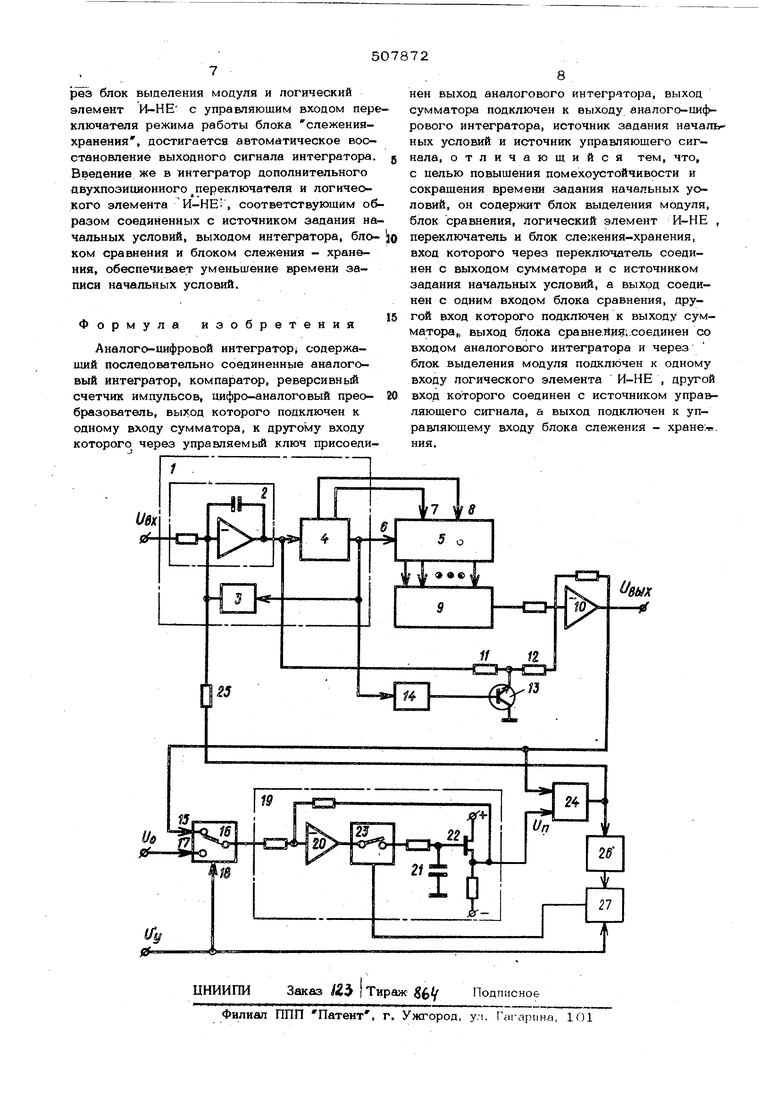

ние-частота 1, построенный на аналоговомпающий на вход сумматора 10. Воэникнове-

интеграторе 2 с целью: сброса в нулевоение импульсов на счетном входе 6 реверси&состояние 3 и трехпоаиционном компараторе.него счетчика 5 происходит в момент вре4, реверсивный счетчик импу/тьсов 5 со , когда напряженке на выходе аналоговое

ньм входом 6 и входами управления ревер- интегратора 2 достигает уровня срабатысом 7,8 соединенными с имгульсным и по-вания компара ора 4, после чего под дейтенциальными выходами компаратЬра, дифро-ствием выходного сигнала компаратора осуаналоговый преобразователь9, соединенныйществляется быстрый сброс (разряд емкос сумматором 10, к другому входу сумма-с™) аналогового интегратора, В результатора через резисторы 11, 12 и управляв- ю компаратор выключается и процесс зарямый ключ на транзисторе 13, подключенныйЯ емкости под действием сигнала повк имгольсному выходу компаратора 4 черезторяется. Поэтому за каждьА период работы

согласующую цепь 14 i подсоединен аналоге.преобразователя 1 с помощью компаратора

вый интехратор 2. Выход аналого-аифрово- . фиксируется величина и знак приращения

го интегратора подключен к входу 15 двух- 16интеграла входного напряжения М л . т, е.

позиционного переключателя 16, другой схеме осуществляется квантование интевход 17 которого соединен с источникомграла входного сигнала по уровню. Приразадания начальных условий Uo , а управляю-шения накапливаются в реверсивном счетчике

ший вход 18 связан с источником сигнала5 « преобразуются в электрическое напряуправления записью начальных условий Иц . 20женйе с помощью цифро-аналогового преобраВыход переключателя 16 подключен кзователя 9. При определенном выборе уроввходу блока слежения - хранения 19, переключения компаратора 4, масштаба держащего усилитель 20, запоминающий кон-цифро-аналогового преобразователя 9 и соденсатор 21, истоковый повторитель на по-противлении на входах сумматора 10 можно левом транзисторе 22 и переключатель ре- 25обеспечить равенство между приращением жима работы слежение-хранение 23. Блокинтеграла входного сигнала на выходе аналослежения - хранения подключен к трехпози-гового интегратора 2 и изменением напряционному блоку сравнения 24. К другомужения на выходе цифро-аналогового преобвходу блока сравнения подключен выход ана-разователя 9, соответствующим приращению лого-цифрового интегратора tttx 30кода в счетчике на единицу младшего разВыход блока 24 через резистор 25 под ряда. В этом случае на входе сумматора ключен к сзтимирующей точке аналогового10 формируется напряжение, пропорционал1уинтегратора 2 и через блок выделения мо-ное интегралу от входного сипнаяа U , дуля 26 и логический элемент И-НЕ- 27-причем погрещность дискретности такого к управляющем у входу переключателя режи- 85аналого-цифрового интегратора практически ма слежение - хранение.равна нулю. Поскольку в реальной схеме Для рассматриваемого устройства харак-время сброса аналогового интегратора 2 терны два режима рабогы - интегрированиеимеет конечное значение (определяемое паи запись начальных условий.раметрами цепи сброса 3), на выходе1сумВыбор режима осуществляется с помо- 40матора 10 могут возникать всплески напрящью переключателя 16 по сигналу управ-жения с амплитудой, равной щагу квантова:

ления U . Работа схемы в режиме инте-ния, и с периодом, обратно- пропоршюнальгрирования (сигнал Ы имеет единичное зна- входному сигналу. Это явление может

чение и переключатель 16 находится в по-привести к существенному искажению выходложении, при котором на вход блока спеже- 45ного сигнала интегратора, особенно при

ния - хранения 19 подключен выходной сиг-больших значениях входного напряжения,

нал аналого г 1шфрового интегратора и, )Ддд уменьщения влияния указанных всплеопроисходит следующим образом.JKOB напряжения в схеме предусмотрен клюПри наличии входного сигнала jift прв-:чввой транзистор 13, которьШ под действиобразователь напряжение-частота 1 гене-je счетного импульса, поступающего на его

рирует импульсы с частотой, пропоршюналь-,базу через согласующую цепь 14, открываной 11|х . При этом в зависимости от зна-ется и отключает сумматор 10 от аналогока Ll4,x на потенциальных выходах трехпо-догд интегратора 2 на емя разряда его

зиционйого сомпаратора 4, соединенных семкости.

входами управления реверсом 7, 8 счетчи- 55 при нормальной работе аналого-цифровока 5, устанавливаются напряжения, настра -го интегратора (без сбоев счетчика 5) блок

вающие счетчик на сложение или вычитаниеслежения - хранения 19 находится в режпймпульсов. Кодовые комбинации, вЬзникак. слежения за выходным сигналом Ubf

щие в счетчике, преобразуются цифро-анало-В этом режиме переключатель 23 замкнут

|говым преобразователем 9 в сигнал, посту-|вОц запоминающий конденсатор 21 подключен

507872 к Bbixony усилителя 20, Благодаря глубокой отрицательной обратной связи на этом конденсаторе поддерживается такое напряженке, при KOTOpONt сигнал на выходе исто:кового повторителя практически все время равен выходному сигналу аналого-цифрового интегратора , (скорость слежения устрой ства аналоговой памяти выбирается выше максимальной скорости интегрирования аналого-иифрового интегратора)., При этом сигнал на выходе блока сра&нения 24 равен нулю, так как разность сиг налов на его входах находится в зоне нечувствительности блока, В этом режиме блок сравнения 24 не оказывает влияния |на работу преобразователя напряжение частота 1, В то же время наличие нулевого напряжения на его выходе поддерживает переключатель 23 в замкнутом состоя нии (сигнал на выходе логического элемента И-НЕ 27 имеет единичное значение), :благодаря чему блок слежения-хранения 19 : работает в режиме слежения. Если же по каким - либо причинам про.т изойдет сбой счетчика 5, то из-за ограниченной скорости слежения блока на входах блока сравнения 24 будут отличаться на величину, превышающую его зону нечувствительности. На выходе блока сравнения 24 возникает напряжение, знак которого определяется рассогласованием си налов на выходах аналого-цифрового интегратора и блока слежения - хранения Благодаря блоку выделения модуля 26 на вход логической схемы 27 поступает сигнал соответствующего знака независимо от рассогласования сигналов , и U н В результате переключатель 23 размыкается и запоминающий конденсатор 21 отключается от усилителя 20. Одновременно сигнал с выхода блока сра нения 24 поступает на вход преобразователя напряжение - частота 1 (через резиicTop 25 напряжение с выхода схемы 24 подается к суммирующей точке аналогового интегратора 2). Под действием этого сигнала преобразователь 1 восстананливает информацию в счетчике 5, так. как подача импульсов на счетный вход 6 осушествляеся до тех пор, пока разность напряжений и U н не снизится до величины, при которой произойдет отключение блока сравнениг 24, После этого переключатель режима слежение-хранение 23 переходит в замкнутое положение, блок сле :ения-хран ния 19 начинает следить за выходным сигналом интегратора Ujj| и схема продол - :жает нормальную работу т. е. формирова - ние интеграла от входного сигнала Лtt Для уменьшения погрешностей восстлио ления информации после сбоев счетчикл n;ii перерывов в подаче питания необходимо увеличивать частоту преобразователя 1 при ;срабатывании релейного элемента блока срлв;нения 24, т. е. сокращать время восстановления информации. Это достигается соответ;ствующим выбором резистора 25. CjniiocT;венно также, чтобы за время восстановления информации напряжение на запоминающем конденсаторе 21 практически не изменяло |своей величины. С этой целью в рассмотренной схеме необходимо использовать переключатель 23 с малыми точками утечки и истоковый повторитель на полевом транзисто; Рассмотрим теперь работу устройства в |режиме записи начальных условий. В этом случае U гО и переключатель 16 устанавливается в положение, при котором на вход блока слежения - хранения подключен источник задания начальных условий И о . Одно- , временно переключатель 23 переходит в Замкнутое состояние независимо от сигнала на выходе блока сравнения 24. В peayHi тате блок слежения - хранения 19 отрабатывает напряжение начальных условий, т. е. а а. (if, , Под действием разности сигналов Uи- и блок сравнения 24 включает1ся и на его рыходе возникает сигнал, по- (ступающий на преобразователь напряжениечастота 1, который по знаку напряжения на выходе блока сравнения 24 настраивает реверсивный счетчик 5 на слеже1гие или вы читание импульсов, : Как и в случае восстановления информации, заполнение счетчика 5 происходит до тех пор, пока не произойдет выключение блока сравнения, т. е, до момента, когда (разность между выходным напряжением анаjлого-цифрового интегратора tH% и сигналом I UH, не станет меньше порога отпускания 1блока сравнения. При соответствующем выi6ope этого порога напряжение .кх будет практически совпадать с напряжением начальных условий Уд , Время записи начальных условий в предлагаемом устройстве ограничивается скоростью слежения устройства аналоговой памяти 19, Это время и опредвг, .:ляет необходимую длительность интервала. :в течение которого на управляющем входе 18 двухпозиционного переключателя 16 допжно поддерживаться нулевое напряжение, Таким образом, благодаря соединению выхода интегратора с блоком слежения :хранения и блоком сравнения, другой вход которого подключен к выходу блока слеже- ния - хранения, а выход - с дополнителр ным входом аналогового интегратора и чс

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU682908A2 |

| Аналого-цифровой интегратор | 1979 |

|

SU813456A2 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Устройство для интегрирования | 1976 |

|

SU596966A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Интегратор | 1978 |

|

SU748438A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| Аналого-цифровой интегратор | 1988 |

|

SU1534473A2 |

Авторы

Даты

1976-03-25—Публикация

1973-10-17—Подача